# NEAR EAST UNIVERSITY

# Faculty of Engineering

Department of Electrical and Electronic Engineering

## FRUIT PACKING OTOMATION SYSTEM (PLC)

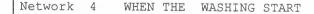

## GRADUATION PROJECT EE - 400

Student: Aliksan Taşdemir (951112)

Supervisor: Özgür C. Özerdem

Lefkoşa - 2001

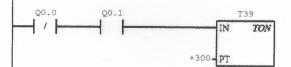

|                                                       |           |      | 21       |

|-------------------------------------------------------|-----------|------|----------|

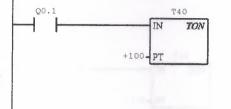

|                                                       |           |      | -ARY     |

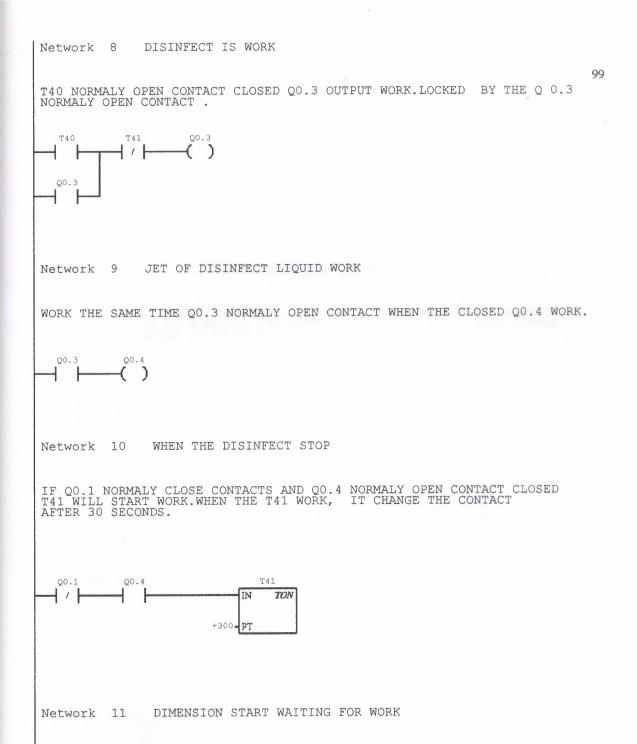

|                                                       |           |      | USRA.    |

|                                                       |           |      | 5        |

|                                                       |           |      | The set  |

|                                                       |           |      | UBRARY 2 |

| ACKNOWLEDGEMENT                                       |           |      |          |

| LIST OF ABREVATIONS                                   |           |      |          |

|                                                       |           |      |          |

| ABSTRACT                                              |           |      |          |

| 1. Introduction                                       |           | 1    |          |

| 1.1 Basics of programmable logic controllers          |           | 2    |          |

| 1.2 Logic                                             | • • • •   | 5    |          |

| 1.3 The laws of boolean algebra                       |           |      |          |

| 1.4 Ladder diagram                                    |           | 10   |          |

| 2. Design, structure and operation                    |           | 10   |          |

| 2.1 PLC architecture                                  |           | 10   |          |

| 2.2 CPU                                               |           | . 13 |          |

| 2.3 Memory                                            |           | 14   |          |

| 2.4 Bus                                               |           | . 16 |          |

| 2.5 Input/output interfaces                           |           | 16   |          |

| 2.5.1 D.C. voltage digital input circuit              |           | 17   |          |

| 2.5.2 A.C. voltage digital input circuit              |           | 18   |          |

| 2.5.3 Pulse counter interface                         |           | 18   |          |

| 2.5.4 Analogue to digital converter (ADC) interface   |           | 20   |          |

| 2.5.5 Transistor output circuit                       |           | . 21 |          |

| 2.5.6 Thac output interface                           |           | 22   |          |

| 2.5.7 Digital to analogue converter (DAC) interface   |           | 22   |          |

| 2.6 Input / output assignment                         |           | 24   |          |

| 2.7 Keyboard and display                              |           | .25  |          |

| 2.8 Program execution                                 |           | . 26 |          |

| 2.9 Multitasking and multiprocessing.                 |           |      |          |

| 2.10 Development systems                              |           | 28   |          |

|                                                       |           |      |          |

| 3. Input devices                                      |           |      |          |

| 3.1.1 Pressure and temperature switches               |           | 30   |          |

| 3.1.2 Proximity switches                              |           | 30   |          |

| 3.1.3 Photoelectric switches                          |           | 32   |          |

| 3.1.3 Photoelectric switches                          |           | 35   |          |

| 3.1.4 Optical switches                                |           | 37   |          |

| 3.2 Analogue devices                                  |           | 37   |          |

| 3.2.1 Linear potentiometer.                           |           | 38   |          |

| 3.2.2 Linear variable differential transformer (LVDT) |           | 30   |          |

| 3.2.3 Tachogenerator                                  | • • • •   | 30   |          |

| 3.2.4 Temperature sensor                              |           | 12   |          |

| 3.2.5 Strain gauge                                    |           | . 42 |          |

| 3.3 Basic interfacing techniques                      |           | . 45 |          |

| 4. Programming methods                                |           |      |          |

| 4.1 Graphical languages                               |           | . 4/ |          |

| 4.1.1 Ladder diagram (LD)                             | • • • • • |      |          |

| 4.1.2 Function block diagram (FBD)                    |           | . 40 |          |

| 4.2 Sequential function chart                         |           | . 49 |          |

| 4.3 Translating between languages                     | • • • •   |      |          |

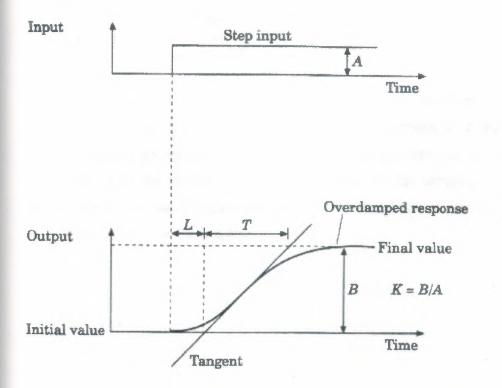

| 5. Ladder programming examples                     | 55  |

|----------------------------------------------------|-----|

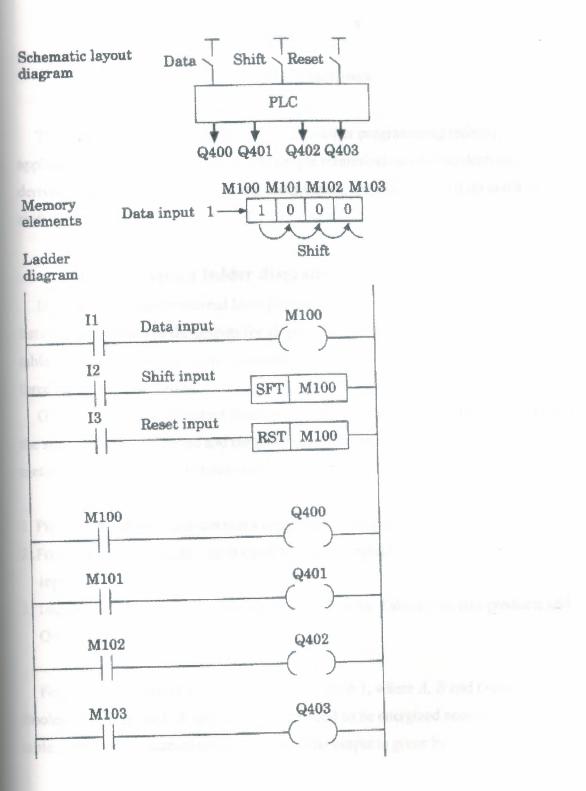

| 5.1 Combinationallogic                             |     |

| 5.2 Latching                                       |     |

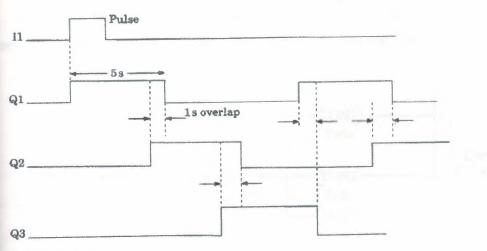

| 5.3 Generating a pulse signal                      | 61  |

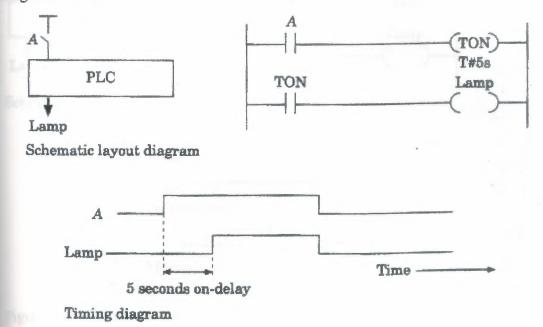

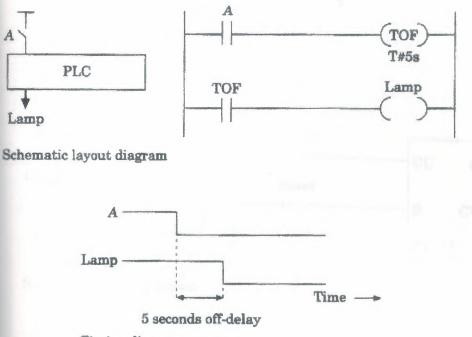

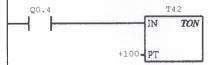

| 5.4 Timers                                         |     |

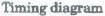

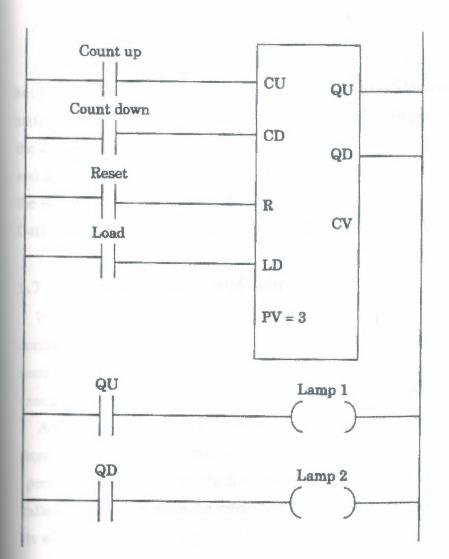

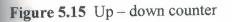

| 5.5 Counters                                       |     |

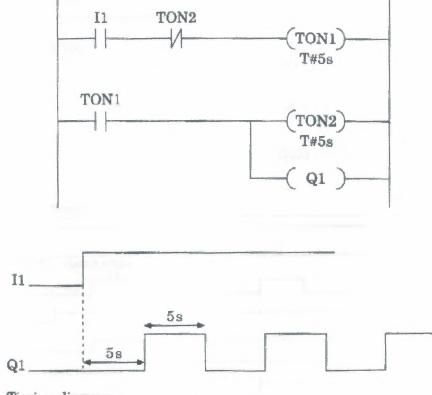

| 5.6 Shift register                                 |     |

| 5.7 Conditional jumps and subroutines              |     |

| 5.8 Arithmetic functions                           | 67  |

| 6. Tutorial examples                               |     |

| 6. IDeriving a ladder diagram from a truth table   | 69  |

| 6.2An off-delay timer circuit                      |     |

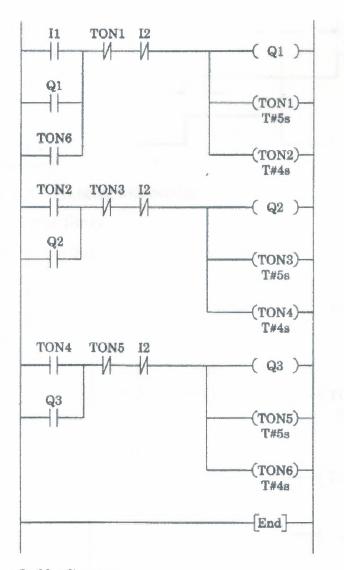

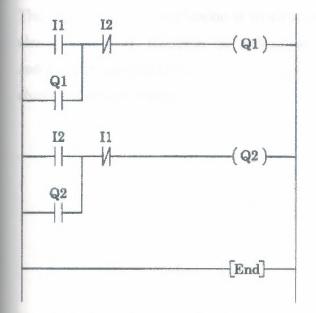

| 6.3Controlling output using timers                 |     |

| 6.4Cyclic timer                                    |     |

| 7.Application examples                             |     |

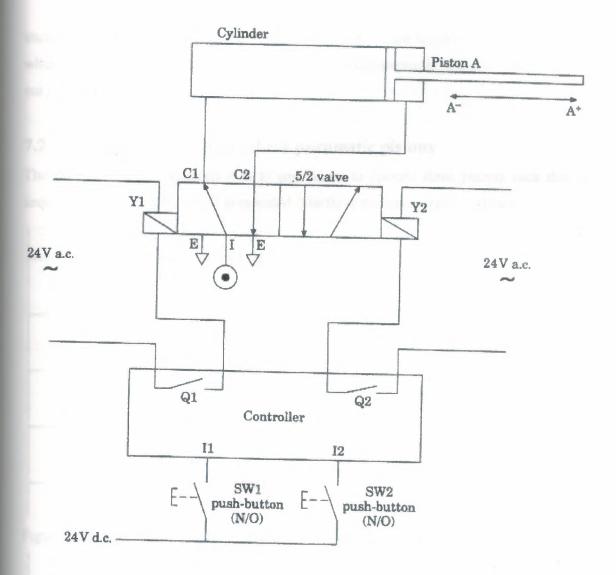

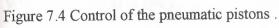

| 7. Example 1: control of a pneumatic piston        |     |

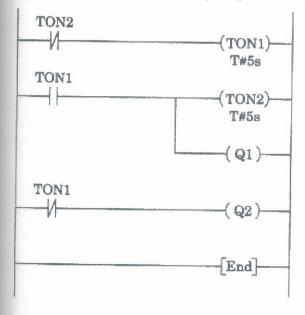

| 7.2Example 2: sequencing of three pneumatic piston | 80  |

| 7.3Example 3 counting and packaging                |     |

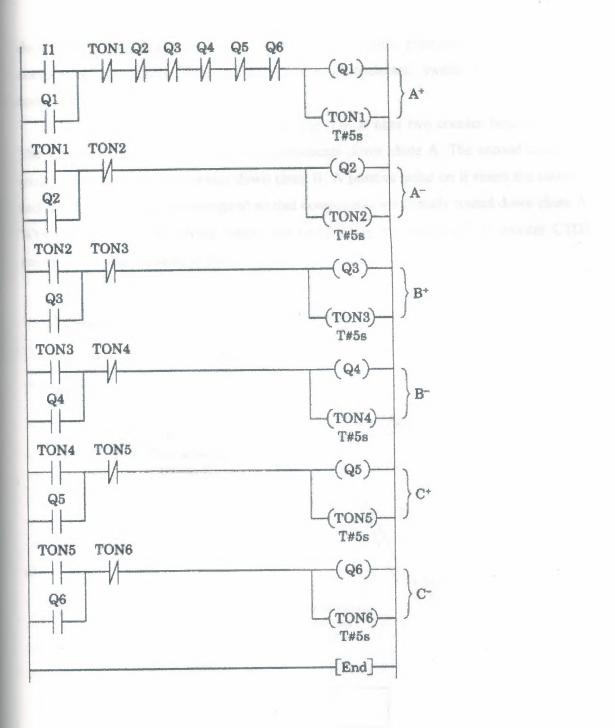

| 7.4Example 4 : component detection and sorting     | 85  |

| 7.SExample 5: pick and place unit                  | 87  |

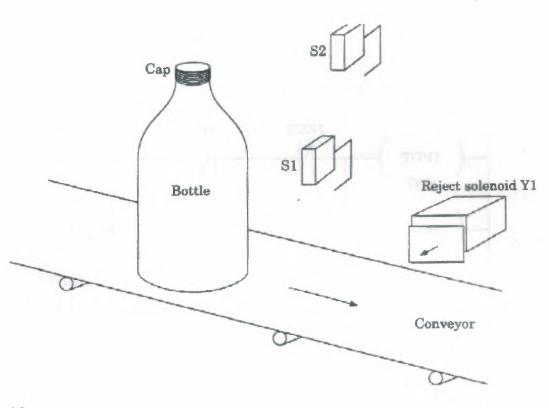

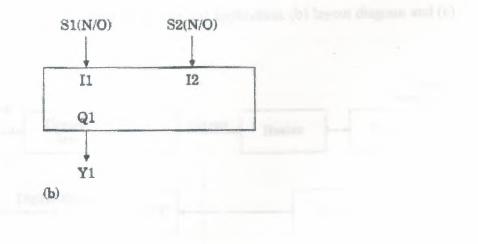

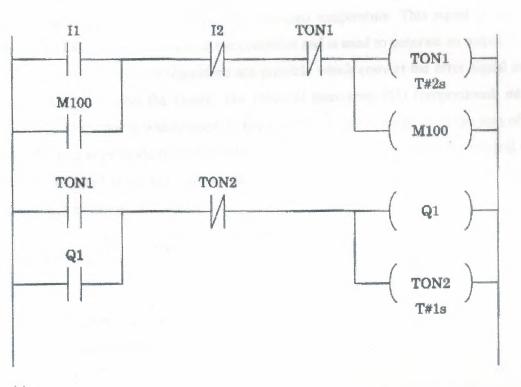

| 7.6Example 6 checking for a missing bottle cap     | 87  |

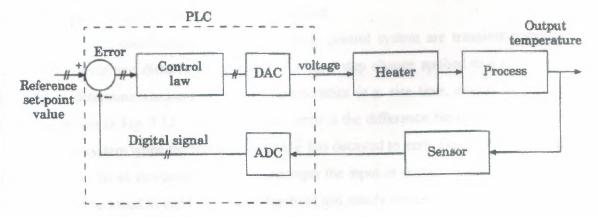

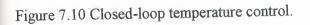

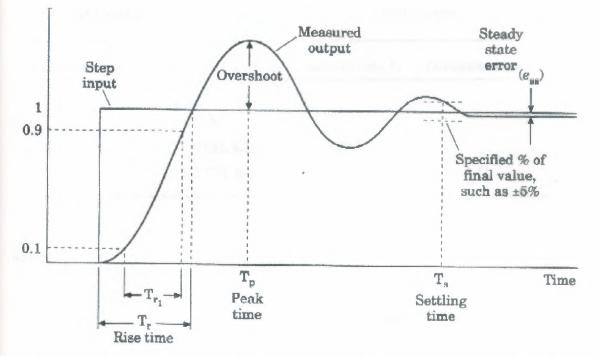

| 7.7Example 7 : PD temperature control              | 89  |

| TABLE OF SYMBOL                                    | 96  |

| MY PROJECT DRAWING AND INTRODUCTION                | 97  |

| CONCLUSION                                         |     |

| REFERENCES                                         | 104 |

| APPENDIX                                           | 105 |

### ACKNOWLEDGEMENTS

i

First of all, I want to thank to my teacher's the supervisor Mr.Özgür C. ÖZERDEM, Mr. Kaan UYAR, and Mr.Mherdad KHALEDİ for supporting me durring my education.

Also thanks to Prof. Haldun GÜRMEN, Prof. Dr. Fakhreddin MAMEDOV,

Prof. Dr. Şenol BEKTAŞ and Prof. Dr. Khalil İSMAİLOV

Then I wish to thank to my friends Altınay ORMAN, Bora E. TUGLU, Orhan ŞADİ Fatoş GÜVEN and Bülent GÜVEN for their help. And finally I want to thank everybody who helped and suppurted me from my first day at the university till my graduation.

### ABSTRACT

The aim of the project is to provide an introduction to the desing structure and operation of PLC's and an insight into their applications.

Chapter 1: Describes the basic of PLC's and their logic based operation

Chapter 2-3: Mainly deal with hardware aspects relating to PLC's. The basic of a PLC's internal hardware structure and program execution are covered in chapter 2-3

Chapter 4: Contains information on the PLC programming languages covered by the international standard

Chapter 5 : Covers all the major espects of ladder function block programming showing how counters, timer and shift registers can be implemented.

Chapter 6 : Covered a set of tutorial-type worked examples.

Chapter 7 : A number of application examples are given in this chapter.

#### ABBREVIATIONS

Absolute encoder A shaft or linear encoder that generates a unique number for resolvable position A.C. or a.c. Alternating current

Access time The time taken for data to be read from memory

Acumulator A CPU register used to hold the results of arithmetic and logic operations

ADC Anologue to digital converter.

Address The numerical assingment of a particular memory location

ALU Arithmetic logic unit.

ANSI American national standard institute

ASCII American standard code for information interchange

**Bandwidth** Iformation carrying capacity of a communication channel expressed in bits/s.

Baud A unit of transmission.

BCD Binary code decimal

**Bit** Binary digit

Boolean data Data represented as a single bit.

Boot To load an operating system

bps Bts per second

**BS** british standart

Buffer A bolck of memory used for temporary storage

Bus A set of conductors used for communicating signals

Byte A group of eight bits

CAD Computer aided design

CAM Computer aided manufacture

**CIM** Computer integrated manufacture

Clock Aperiodic signal used for synchronization

**Closed-loop control** A system in which the output signal is measured and fed back to the input point.

**CNC** Computer numerical control

200

**Contact bounce** The problem relating to mechanical switches which produce a noisy signal when swithed

Compiler A program to translate a high-level language into machine code

**Counter** A function block that gives an output when a set number of pulses have been applied to the input

**CPU** Central processing unit

CSMA/CD Carrier sense multiple access with collusion detection

Current sinking The action of receiving current

DAC Digital to analog convertor

EEPROM Electrically erasble programmableread only memory

EPROM Electrically programmableread only memory

FET Field effect transistor

Flag A single bit variable used the indicate that some conditions has occurred

Full dublex A full dublex data link allows the transmission data simultaneously

In bth direction

Gateaway A device thas connects and allows messages to be communicated between to or more differet network system

Gray code A binary code in which consecutive codes differ in only a single bit position

Hexadecimal Base 16 number system

Hz Hertz .the unit of frequency equal to one cycle per second

**IC** Integrated circuit

**IEC** International electrotechnical commisions

**IEE** Institute of electrical enngineers

**IEEE** Institute of electrical and eletronic eng.

Ladder diagram A programming language in which a circuit, consisting of contacts,

coils and other elements, such as functions blocks, and bounded between left and right vertical lines.

LSB Least significant bit

Machine code Binary number that represent CPU instruction

MSB Most significant bit

MTBF Mean time between failure

N/C Normaly closed

N/O Normaly open

**Off-delay timer** A function block that holds its output high for a specified duration when its input changes from high to low

**On-delay timer** A function block that delays setting its output high when its input changes from low to high

**Program counter** A CPU register containing the address of next instruction to be executed

**Programming language** IEC – defined programming languages are function block diagram (FBD)

RAM Random access memory

**ROM** Read only memory

Run The run mode executes the user program stored in memory

Scan PLC program execution loop to continously read input values and set outputs

according to the program requirement

State The condition of a Boolean variable

Tachogenerator A permanent magnet d:c: motor operated as a voltage generator:

TTL Transistor-transistor logic.

Two's complement A system for representing negative numbers in binary notation

## CHAPTER 1 Information about PLC

## 1.1 Basics of programmable logic controllers

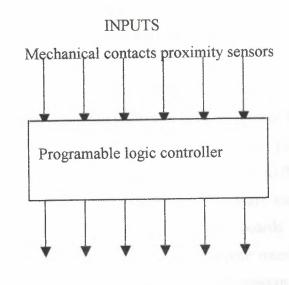

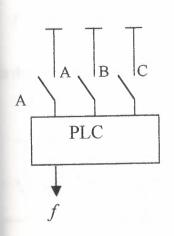

An apt definition of a programmable logic controller (PLC) is that it is a 'digitally operating system, designed for use in an industrial environment which uses a programmable memory for internal storage of user-orientated instructions for implementing specific functions such as logic, sequencing, timing, counting and arithmetic, to control, through digital or analogue inputs and outputs, various types of machines or processes. Figure 1.1 shows how the control action is achieved. Input devices (e.g. limit switches, proximity switches) and output devices (e.g. relay coils, signal lamps) from the machine or process to be controlled are connected to the PLC. A user enters a sequence of instructions (known as the program) into the PLC's program memory. The controller then continuously monitors the states of the inputs and activates outputs according to the control algorithm defined by the user's program.

#### OUTPUTS

Pilot lamps, solenoid valves, contactors

Figure 1.1 the control action of a PLC.

Because the stored program can be modified, new control features can be added or old ones changed without rewiring the input and output devices. The result is a flexible

1

system which can be used for control tasks that can vary in nature and complexity. The main differences between a PLC and, say, a microcomputer are that:

1. Programming is predominantly concerned with control logic and function block operations.

2. Interfacing circuits are integral to the controller.

3. PLCs are rugged, being packaged to withstand vibration, temperature, humidity and noise.

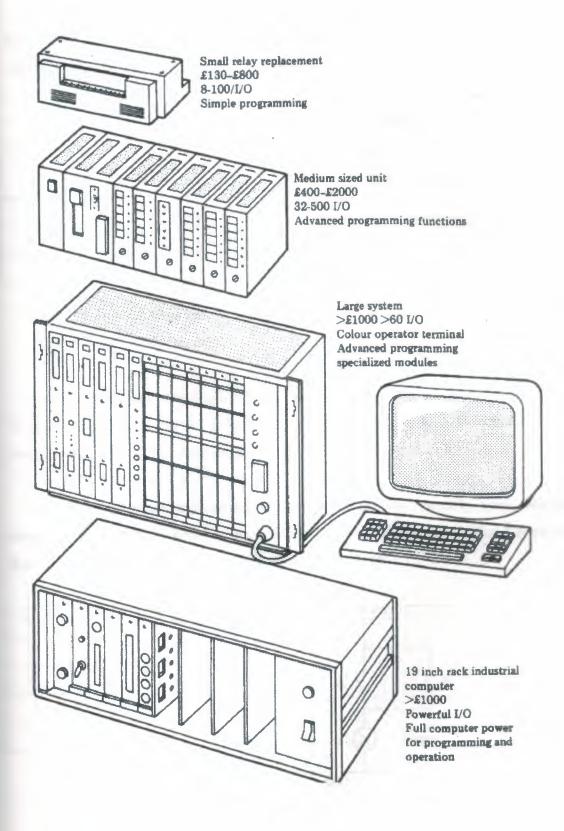

Some typical programmable controllers are shown in Fig. 1.2.2 Systems range from:

1.Stand-alone single unit PLC systems. These systems have a fixed number of input/output (I/O) points and are suited for small I/O automation tasks. Programming consoles are usually hand-held units which attach directly to thePLC.

2.Modular PLC systems. These systems are composed of self-contained hardware building blocks (modules), which plug directly into a proprietary bus back plane. A minimum configuration would utilize a CPU unit, a power supply unit and input/output (both digital and analogue) modules. The modular approach to PLC hardware means that the number and type of I/O points can be expanded. Special function modules for operations such as networking and computer linking are often provided. A host computer is usually used to develop program code, which is then targeted to the PLC hardware.

3.Computer bus based systems. Although not strictly a PLC system, it is possible to construct a custom computer controller using processor boards and peripheral interface boards which plug into a common bus back plane (rack). Various international bus standards have been developed for this purpose such as the STE (Euro card) bus and the VME bus. The modular approach to target hardware means that processing power can be increased by adding additional processor boards (assuming multiprocessing is supported by a bus scheduler) and special purpose interface boards can be designed to the bus standard. Bus based systems are usually programmed using high level language (e.g. PASCAL and C) cross compilers which execute on a host computer and which target hardware on the bus. Such systems fall outside the scope of this book.

#### 1.2 Logic

The term 'logic' features in the name 'programmable logic controllers' because programming is based on the logic demands of input devices. Programs implemented are predominantly logical rather than discrete versions of continuous algorithms. This section provides an introduction to logic.

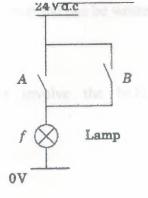

The field of logic is concerned with systems that work on a straightforward two-state basis. A common electric light switch can be either *on* or off and these alternate possibilities can be labeled as true and false or as 1 and 0 (binary form) respectively. A Boolean variable (i.e. a logical variable) such as A can be used to represent any switchlike element, which can have one of two states. For example, it is possible to define thatA=1 when the switch on andA=O when the switch is off

Any condition in which there are two possibilities can be defined using a Boolean variable. For example, a work piece can be in or out of position. This may be represented as a simple binary statement B=1 (work piece is in position) or B=0 (work piece is not in position). Another example is a lamp, which can be either on or off.

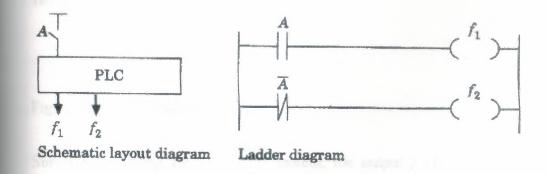

If the Boolean variable A is used to represent the on and off positions of a single throw normally open (abbreviated to N/O) switch the variable NOT A represents a normally closed (abbreviated to N/C) switch. The NOT logic function inverts the state of the input. The variable NOT A can be written as A, where the over bar denotes negation. Figure 1.3 tabulates the truth values (i.e. 0 and 1) of A against those of NOTA for the two switch positions.

| Switch position | Α | A |

|-----------------|---|---|

| Off             | 0 | 1 |

| On              | 1 | 0 |

Truth table for the NOT function closed

Figure 1.3 The NOT function.

Normally open

Normally

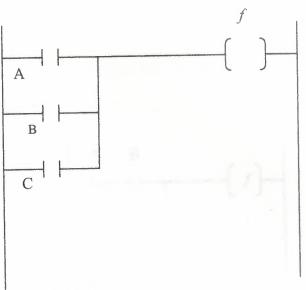

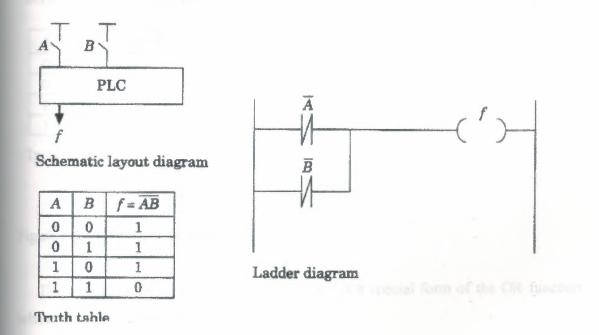

The AND logic function describes the operation of two normally open single-pole, single-throw switches connected in series as shown in Fig. 1.4. Current flows only when

both the two switches A and B are on, i.e. when A=1 and B=1. The output f can be written as the Boolean expression:

| A | В | f = AB |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

0 V

Truth table for the AND gate Figure 1.4 The AND function.

Note that this is not a multiplication but the logical notation used to mean that f is 1 if A is 1 and B is 1. For an AND function with three inputs A,B,C (e.g. three N/O switches in series) the Boolean expression for the output f would be written as

f = ABC

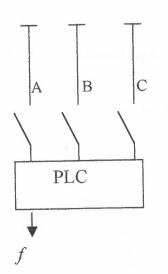

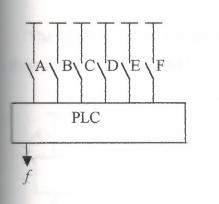

The OR logic function describes the operation of two normally open switches connected in parallel as shown in Fig. 1.5 Current flows when either switch A or switch B are in the on position. The Boolean notation for A OR B

| А | В | f = AB |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

Figure 1.5 The OR function.

### 1.3 The laws of Boolean algebra

The above introduction has established the link between switching circuit diagrams and Boolean expressions. Rev. George Bode (1815-64) developed laws to analyze and

construct logical statements. Boolean algebra deals with two-valued variables and is useful when analyzing switching circuits such as ladder diagrams.

The laws of Boo lean algebra consist of postulates and theorems. The four postulates, which deal with the combination of one Boolean variable and with, the constants 0 and 1 are

| A+0=A |  |  | (1.1) |

|-------|--|--|-------|

| A+1=1 |  |  | (1.2) |

| A0=0  |  |  | (1.3) |

| A1=A  |  |  | (1.4) |

The two postulates that deal with one variable with itself are called the idem potent laws and are

| A+A=A | (1.5) |

|-------|-------|

| A+A=A | (1.5) |

$$AA=A$$

(1.6)

The commutative laws emphasize the fact that the position of the variables in an expression is not important. The commutive laws are

| $\mathbf{A} + \mathbf{B} = \mathbf{B} + \mathbf{A}$ | (1.7) |

|-----------------------------------------------------|-------|

|-----------------------------------------------------|-------|

$$AB = BA \tag{1.8}$$

The associative laws deal with the use of brackets at can be expressed as

$$(A+B) + C = A + (B+C)$$

(1.9)

(AB)C = A(BC) (1.10)

The distributive laws show how factors are combined and can be written as

(AB) + (AC) = A (B+C) (1.11)

(A+B)(A+C) = A + (BC) (1.12)

The complementarity's and involution laws involve the NOT function. The complementarity's laws are

$$\mathbf{A} + \mathbf{\overline{A}} = 1 \tag{1.13}$$

$$AA=0 \tag{1.14}$$

The involution law is

$$(A)=A$$

(1.15)

Two other\_postulates that involve the NOT function are called De Morgan's theorems which are

$(AB) = A + B \tag{1.16}$

### $\overline{(A+B)} = \overline{A} \overline{B}$

#### (1.17)

The function A AND *B* all negated (i.e. (*AB*) is called the NAND function. NAND is an abbreviation for NOT AND. Similarly, the function *A* OR *B* all negated (i.e. (A + B)) is called the NOR function. NOR is an abbreviation for NOT OR.

There are two branches of logic called combinational logic and sequential logic. A combinational logic system is one in which the output is a direct and unique consequence of the input conditions. A sequential logic system is one that depends on the sequence in which the inputs occur. This introduction has dealt with combinational logic. Sequential logic devices (e.g. flip-flops, shift registers) are discussed in Chapter 5.

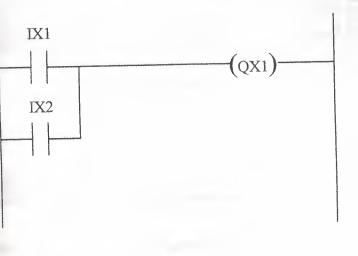

#### 1.4 Ladder diagrams

PLCs were developed to offer a flexible (e.g. programmable) alternative to conventional electrical circuit relay-based control systems built using discrete devices. The terminology and other concepts used to describe the operation of a PLC are based on conventional relay control terminology. The relationship is such that inputs are referred to as contacts, outputs are referred to as coils and memory elements (bits) are referred to as auxiliary relays.

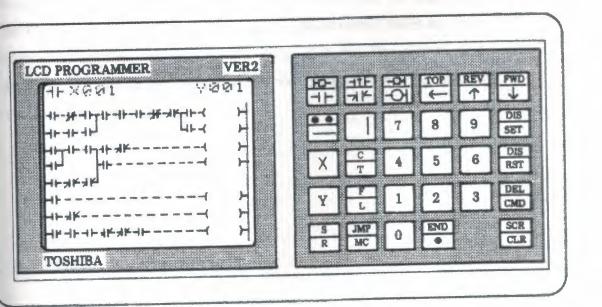

The International Electro technical Commission (IEC) advocates five programming methods for PLCs, which are fully discussed in Chapter 5. Of these five, the predominant programming method used by all mainstream PLC systems is the ladder diagram method. This is a graphical programming technique, which has been evolved from conventional electrical circuit relay logic control methods. PLC systems provide a design environment (either in the form of software tools running on a host computer terminal or a hand-held LCD graphic programming console), which allow ladder diagrams to be developed and diagnosed.

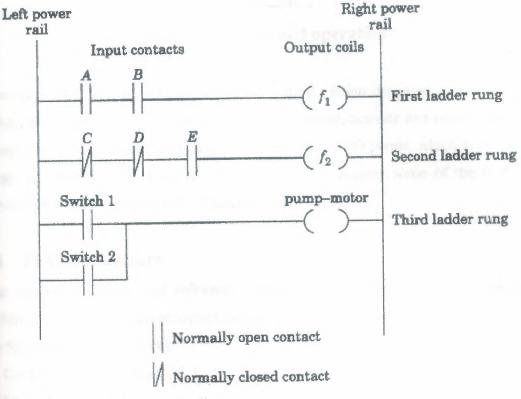

In its simplest form, a ladder diagram is a network of contacts and coils bounded on the left and (optionally) on the right by vertical lines called power rails. The key features of a ladder diagram are:

1. Contacts represent the states of Boolean variables. For example, a contact called 'start\_fan' might represent the ON and OFF state of a switch which is used to initiate a ladder rung which operates a fan. The ladder symbols for normally open and normally closed contacts are and respectively.

2. A typical ladder rung is a horizontal line of contacts which start from the left power rail and which provide the logic to operate a coil (or coils). A coil is a Boolean variable on the right of a ladder rung, which can be set to a true state when the contacts connecting it to the left power rail are on. The ladder symbol for a coil is a pair of parenthesis().

3. When contacts of a ladder rung are in the true state notional power is deemed to flow from the left power rail through the contacts to operate a coil (or coils) at the righthand end of the rung. The drawing of the right power rail is optional as its use is implied.

4. The normal convention for evaluating ladder rungs is from top to bottom. Each ladder rung is scanned and evaluated one after the other starting from the top. The cyclic scan based operation is further discussed in Chapter 2.

5.Function block elements such as timers, counters and shift registers can be Connected into a ladder diagram provided that their inputs and outputs are Boolean variables. Function block elements are discussed further in Chapter 5.

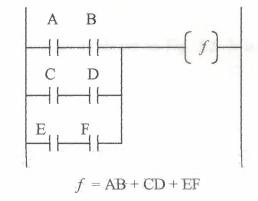

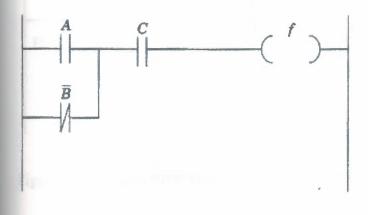

An example ladder diagram is shown in Fig. 1.6. A ladder diagram is drawn as a set of rungs with each one representing a control action. An input contact represents the state of a Boolean variable. In the first ladder rung the inputs labeled A and B are connected in series and represent a two-input AND function. The output  $f_1$  is 1 (true) if A is 1 and B is 1. In the notation of Boolean algebra the AND function is written as  $f_1 =$ AB.

The second ladder rung represents a three-input (i.e. the inputs C, D and F) AND function in which two normally closed (N/C) contacts are used. The third ladder rung represents a two-input OR function. This time the contacts have been labeled (identified) as switch 1 and switch 2 and the output as the Boolean variable 'pump motor'.

The names that are used to reference Boolean variables are called 'identifiers'.

9

Figure 1.6 An example ladder diagram.

In Fig. 1.6 the names switch 1, switch 2 and pump motor which refer to input and utput devices are examples of identifiers. The naming of contacts and coils in this way ids the readability of a ladder diagram. However, note that each identifier has to be ssigned a unique memory address used to identify an I/O point. The binary, octal and exadecimal number systems (see Appendix 2) are widely used in the direct referencing f I/O points.

#### **CHAPTER 2**

#### Design, structure and operation

A modern PLC is a microprocessor-based control system designed to operate in an industrial environment. PLCs are programmed to sense, activate and control industrial equipment and therefore incorporate a large number of I/O points, which allow a wide range of electrical signals to be interfaced. In this chapter some of the important concepts behind the design of PLC hardware are presented.

#### 2.1 PLC architecture

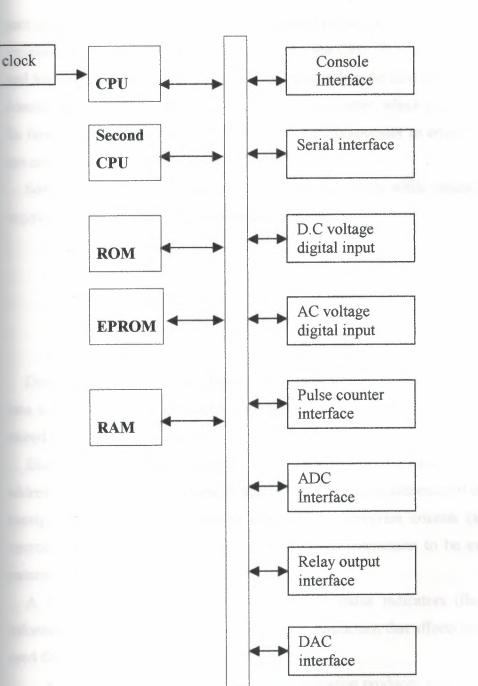

The internal hardware and software configuration of a PLC is referred to as its architecture. Being a microprocessor-based system the design of a PLC is based around the following building blocks:

- Central processing unit (CPU)

- Memory

- Input/output interface devices

These elements are semiconductor integrated circuits (ICs). They are interconnected by means of a bus as shown in Fig. 2.1. A bus is a group of lines over which digital information (e.g. 8 bits of data) can be transferred in parallel. In most systems there are three distinct buses: the data bus, the address bus and the control bus.

A program written by the user determines the operation of a PLC system. High-level programs such as ladder diagrams are converted into binary number Instruction codes so that they can be stored using digital memory devices such as RAM (random access memory) or programmable ROM (read only memory). Each successive instruction is fetched, decoded and executed by the CPU.

#### 2.2 CPU

A CPU generally takes the form of a single microprocessor device. The function of the CPU is to control the operation of memory and I/O devices in the system and to process data in accordance with the program. To do this it requires a clock signal to sequence its internal operations.

BUS (address data and control)

Figure 2.1 Simplified architecture of a PLC system.

The essential elements of a microprocessor are:

- •Registers

- •Arithmetic logic unit (ALU)

- •Control unit

A register is a byte (8 bits), word (16 bits) or long word (32 bits) of memory which is

part of the microprocessor as opposed to general purpose memory. A register is used for temporary storage of data and addresses within the CPU. The ALU performs arithmetic and logical operations such as addition and subtraction on data stored in registers. The control unit is basically a set of counters and logic gates, which is driven by the clock. Its function is to control the units within the microprocessor to ensure that operations are carried out in the correct order.

Some CPU registers are accessible to the programmer while others are not. Some registers common to most microprocessor devices are:

- Data registers

- Address registers

- A program counter

- A flag register

- A stack pointer

Data registers hold data, which is to be operated on by the ALU. A bit pattern moved into a data register can be added, subtracted, compared, etc., with another bit pattern stored in a separate data register.

Each memory location in RAM and ROM for storing data is given an unique address. The programmer to specify source and destination addresses of data items to be manipulated can use CPU address registers. The program counter (also called the instruction pointer) holds the address of the next instruction to be executed and is automatically incremented by the CPU.

A flag register is a collection of single-bit status indicators (flags) that holds information about the result of the most recent instruction that affects them. Commonly used flags are:

• Carry bit Set to 1 if a binary addition operation produces a carry or a subtraction operation produces a borrow.

• Zero bit Set to 1 whenever the result of an operation is zero.

• Negative bit In signed binary arithmetic it indicates the sign (positive or negative) of the result.

• Overflow Set to 1 when the result of an arithmetic operation cannot be represented in the specified register size.

A stack is a variable length data structure in which the last data item inserted is the first to be removed. A stack pointer register contains the address of the top element of

the stack. The CPU uses the stack to store subroutine return addresses for example.

The execution time of each instruction code takes a specific number of clock cycles. The clock cycle time is the reciprocal of the clock frequency. For example, a 10 MHz clock has a clock cycle of  $0.1 \, \mu$ s.

#### 2.3 Memory

Memory devices store groups of binary digits (usually bytes) at individual locations identified by their own unique addresses. Memory devices are ICs having an address input (commonly 16 bits wide) and an in/out data port (commonly 8 bits wide). There are two main types of memory, namely RAM (random access memory) and ROM (read only memory). The number of binary digits it can hold determines the storage capacity of a memory device. A 1K-byte memory device is capable of storing 1024 (i.e. 210) bytes.

A large proportion of the total addressable memory space is devoted to RAM, which is capable of having data written to it and read from it by the CPU. RAM is used for program and data storage. A backup battery supply is needed to retain the memory contents of RAM, as stored data is lost when the power is removed.

There are two main types of RAM, namely SRAM (an abbreviation for static RAM) and DRAM (an abbreviation for dynamic RAM). Static RAM holds data in flip-flop type cells, which stay in one state until rewritten. SRAM has a fast data access time of typically 10—20 ns. Dynamic RAM requires special circuitry to provide a periodic refresh signal in order to maintain the stored data. This is because DRAM technology stores data in capacitor type cells, which must be periodically refreshed as capacitors discharge as time increases. DRAM is cheaper to manufacture but because a refresh signal is used access time is slower than that of SRAM, typically 50—60 ns.

The PLC operating system (i.e. the program that allows the user to develop and run applications software) is stored in a type of memory referred to as ROM. Once programmed, this type of memory can only be read from and not written to but does not lose its contents when the power is removed.

Common types of read only memory that are user programmable are EPROM (erasable programmable read only memory) and EEPROM (electrically erasable programmable read only memory). EPROM's are programmed using a dedicated programmer and erased by exposing a transparent quartz window found in the top of

each device to ultraviolet light. The erasing process clears all memory locations and akes between 10 and 20 minutes. EEPROM is erased using electrical pulses rather than altraviolet light. Most PLC systems provide facilities that allow application software to be stored in either EPROM or EEPROM.

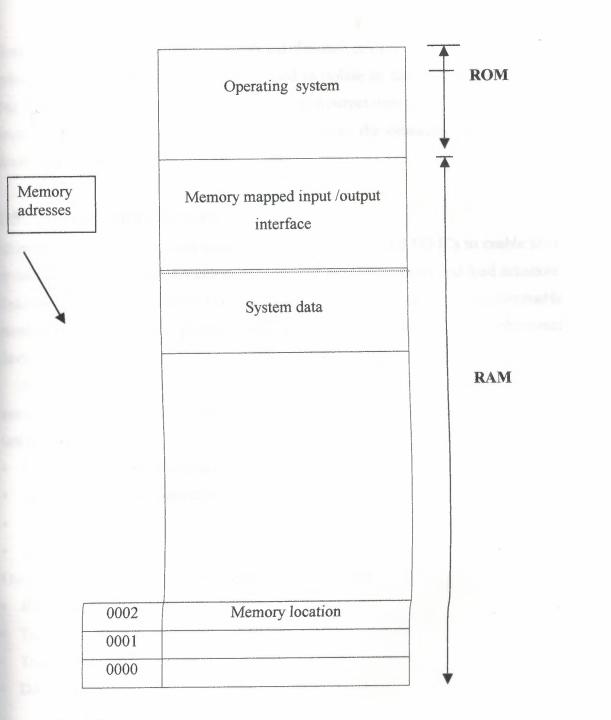

A memory map is used to indicate how address locations are allocated to ROM, RAM and input/output devices. If I/O devices are placed in the memory address space they are said to be memory mapped and access to I/O points is via load and store memory instructions. This has the advantage that common sets of instructions are used for memory and I/O operations. A memory map of a typical PLC system is shown in Fig. 2.2.

#### 2.4 Bus

A bus can be considered as a set of lines over which digital information (e.g. 16-bit address or 8-bit data) can be transferred in parallel. In most systems there are three distinct buses:

- Data bus

- Address bus

- Control bus

The data bus is a bi-directional path on which data can flow between the microprocessor, memory and I/O. An 8-bit microprocessor has a data bus, which is 8 lines wide. A 16-bit microprocessor has a data bus, which is 16 lines wide.

The address bus is a unidirectional set of lines, which carry binary number addresses. The CPU generates addresses during the execution of a program to specify the source and destination points of the various data items to be moved along the data bus. An address identifies a particular memory location or I/O point.

#### Figure 2.2 Memory map.

The control bus consists of a set of signals generated by the CPU to control the devices in the system. An example is the read/write control line, which selects one of two operations, either a write operation where the CPU is outputting data on the data bus or a read operation where the CPU is inputting data from the data bus.

Digital devices sharing a bus must be tri-state. This means that when the output lines are not in use they are put into a high impedance state so that they will not load the bus. Therefore an output line can have one of three possible conditions, which are logic 0

15

low), logic 1 (high) and output disconnected. Tri-state devices incorporate a chip select also called chip enable) input, which is used to isolate its data output lines from the ous. When the chip select line is not active the data output lines are placed in to the high mpedance or tri-state. The control bus co-ordinates the connection of the various devices to the data bus.

## 2.5 Input/output interfaces

Microprocessors are supported with special purpose peripheral I/O ICs to enable them to interface with external devices such as keypad displays, sensors and load actuators. Examples of special purpose I/O ICs include keyboard controllers, programmable parallel interface devices, programmable serial interface devices and counter/timer devices.

As far as the user is concerned, it is the front end circuits to which sensors and actuators are connected that is important. Input points can include the following types of interface:

- D.C. voltage digital input circuit

- A.C. voltage digital input circuit

- Pulse counter circuit

- ADC interface

Output points can include the following types of interface:

- Relay output circuit

- Transistor output circuit

- Triac output circuit

- DAC interface

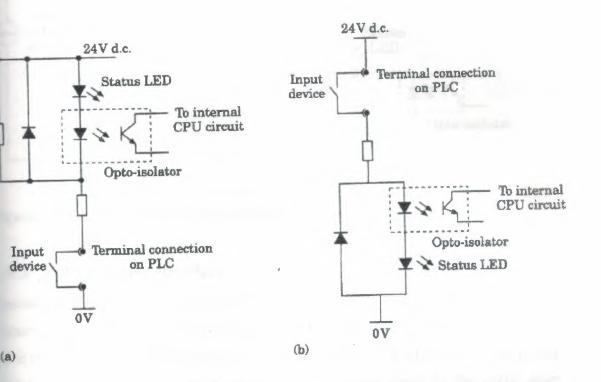

## 2.5.1 D.C. Voltage digital input circuit

Figure 2.3 illustrates typical 24 V D.C. input circuits for connecting current sinking and sourcing input devices. With the sink input interface the input device when turned on connects the circuit to the 0 V line of the D.C. supply. Current then flows through the status LED (light-emitting diode) used to indicate the current logic state of the input point and the opto-isolator.

An opto-isolator combines an LED and photoelectric transistor. When current is passed through the LED it emits light, causing the photoelectric transistor to turn on.

ovided a separate supply is used for the LED and photoelectric transistor circuits a ry large degree of isolation is maintained between the two components.

igure 2.3 D.C. voltage digital input circuits: (a) sink input circuit and (b) source aput circuit.

With the current sourcing interface the input device, when turned on, connects the ircuit to the positive polarity of the supply (i.e. 24 V). Current flows from the supply hrough the status LED and opto-isolator circuit.

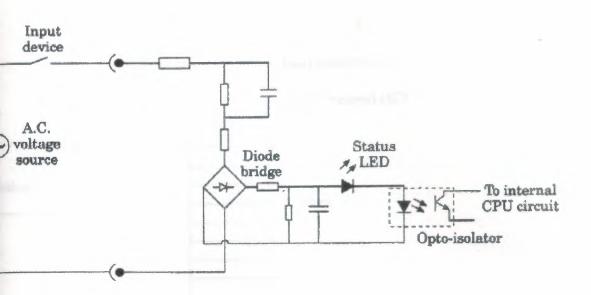

## 1.5.2 A.C. Voltage digital input circuit

Figure 2.4 illustrates an a.c. voltage digital input circuit. A full-wave diode bridge circuit is used to convert the a.c. input signal into a rectified D.C. signal. The status ED and opto-isolator are turned on by the rectified D.C. signal.

ure 2.4 A.C. voltage digital input circuit.

#### 5.3 Pulse counter interface

ecial purposes ICs are available which integrate a high-speed digital pulse counter cuit and buffer memory. Input modules based around these ICs can be used to read lse streams from an input device such as a shaft encoder. The advantage of using such odules is that high-speed pulse counting is not slowed down by the cyclic scan eration of a PLC because the counter circuit operates independently. Provided the emory buffer is accessible to the ladder program it can be read at the point in time then the pulse count value is required. It is also possible to use a technique whereby the gh-speed counter circuit interrupts the CPU when the count value reaches some prefined limit.

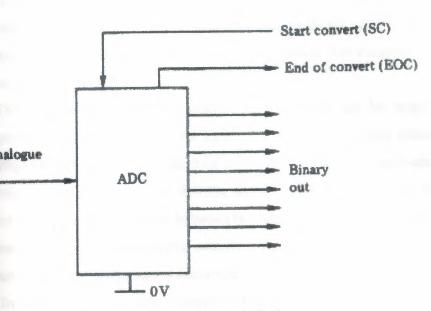

## 5.4 Analogue to digital converter (ADC) interface

a analogue input circuit will incorporate an analogue to digital converter (ADC) vice, as shown in Fig. 2.5. An ADC accepts an analogue input signal and converts it o an output binary value that corresponds to the level of the analogue input. Most DC devices incorporate a start convert (SC) pin, an end of convert (EOC) pin and a mple and hold circuit. When the start convert signal is pulsed the ADC samples and lds (stores) the analogue value input to the device at that time. The ADC converts the alogue signal into a digital value and then produce an end of convert signal when the nversion is complete.

ure 2.5 Analogue to digital converter (ADC).

The time taken by the ADC to convert an analogue signal into a digital number is led the conversion time. There are a number of different types, of AD. Devices numercially available, which work on different principles. One common type uses a hnique called successive approximation to obtain short conversion times. This olves comparing the output of a digital to analogue converter (DAC) with the voltage be converted by making a series of successive guesses (i.e. approximations) at the ue of the binary number required. The fastest type of ADC is the flash converter, ich determines simultaneously all the bits for the digital number representing the alogue input level.

According to sampling theory, an ADC should sample an input signal at lead twice fast as the input's highest frequency component. If the input signal i sampled too wly, aliasing occurs. In this case, a high frequency signal is represented by an oneous lower frequency value. A technique to prevent an aliasing. Error condition curring is to precede the ADC with an anti-aliasing filter which band limits the input nal to half the sample frequency.

Speed of operation is not the only consideration when selecting an ADC. An 8-bit DC approximates the analogue input voltage into one of 28 or 256 discreet levels illed quantization levels. If there are 256 quantization levels including, zero, there will 255 steps between them. This means that, for an 8-bit ADC designed so that the

eximum of the analogue input is limited to 5 V, the quantization interval (i.e. solution) is 5/255 or 19.6 mV. The only way to obtain more quantization levels is to crease the number of bits used in the conversion. For example, a 12-bit ADC will ve 212 or 4096 levels.

The input range of an analogue voltage interface can be unipolar (0-10 V for ample) or bipolar (± 10 V for example). In addition, input channels can often be infigured as either single-ended or differential inputs. A single-ended input has one rminal connected to 0 V so that the signal varies with respect to 0 V. A differential put measures the difference between two signal leads. Differential inputs can provide bise immunity as a noisy signal occurring equally on both signal leads is cancelled out hen the voltage difference is measured.

In industrial applications analogue currents rather than voltages are often used. This because the resistance of the cable reduces a voltage applied to one end of a cable hereas the current remains fixed. The resistance of a cable is proportional to its length and so the reduction of voltage increases with length. A commonly used current input ange is 4—20 mA. By using this range a broken cable gives a result of 0 mA, which is lentified as an error. Measuring the voltage across a known resistance through which are current is passing and applying Ohm's law performs the input of current to an ADC.

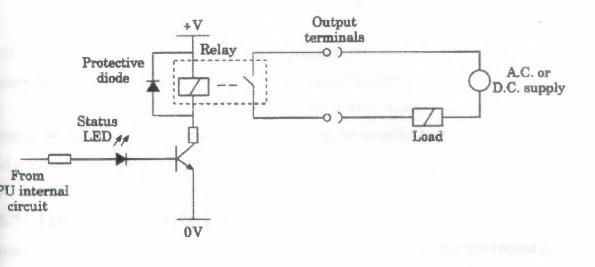

## .5.5 Relay output circuit

Figure 2.6 illustrates the circuit for a relay output interface. The NPN transistor is sed to switch current through the relay coil to close its contact. The internal circuit of he PLC controls the transistor. The diode is connected across the relay coil to protect he transistor from the effects of back e.m.f. This is the reverse voltage developed in the elay coil, which causes an inductive current, which opposes the normal flow of current. Both A.C. and D.C. supplied loads can be connected through the relay output terminals.

20

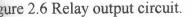

#### 5.6 Transistor output circuit

A transistor output circuit is used for switching d.c. Voltages. Figure 2.7 shows a bical opto-isolated NPN transistor switch output circuit. The principle of operation of ransistor switch ideally relies on there being:

•An open circuit (i.e. infinite resistance) between the collector and emitter when the se-emitter circuit is not forward biased

•A short circuit (i.e. zero resistance) between the collector and emitter when the se-emitter circuit is forward biased

gure 2.7 NPN transistor switch circuit.

The ideal switching action of a transistor requires that the base current be large ugh for the collector current to reach its maximum or saturation value. At saturation, voltage drop between the collector and emitter is very small. Consequently, the ector is close to 0 V and the collector current may be roughly determined from the d resistance and supply voltage.

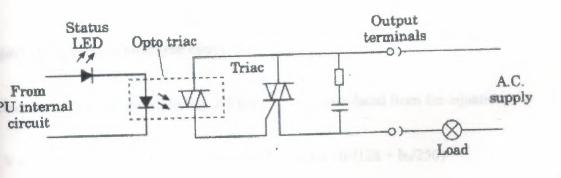

## .7 Triac output interface

riac output device is used for switching a.c. voltages. Triac devices that incorporate a o crossing circuit to monitor the a.c. cycle have the advantage that they turn off at o current. Inductive loads should be turned off at a zero current crossing point to vent interference. A typical opto-isolator-based triac output circuit is shown in Fig.

gure 2.8 Triac output circuit.

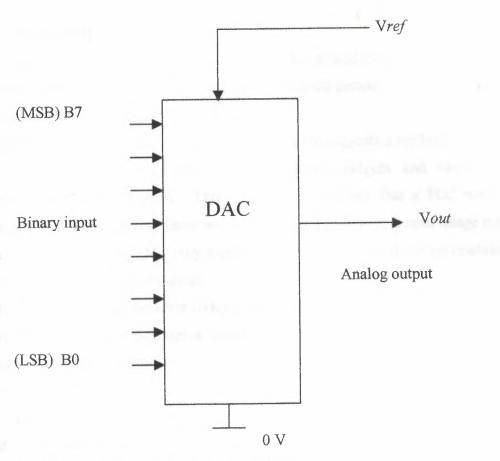

## 5.8 Digital to analogue converter (DAC) interface

In analogue output module will incorporate a digital to analogue (DAC) device as own in Fig. 2.9. A DAC converts a binary number input into a proportional Analogue vel. The analogue output is produced from a reference voltage Vref. The binary umber input to the DAC determines what fraction of Vref. is presented at the output.

re 2.9 Digital to analogue converter (DAC).

or the 8-bit DAC shown in Fig. 2.9 the output is calculated from the equation

$V_{\text{out}} = V (b_7/2 + b_6/4 + b_5/8 + b_4/16 + b_3/32 + b_2/64 + b_1/128 + b_0/256)$

Where the bits  $b_0$  to  $b_7$  can take the values 0 or 1 and are the binary inputs. Here  $b_7$  is most significant bit (MSB) and  $b_0$  the least significant bit (LSB).

In 8-bit DAC has 28 or 256 quantization levels and 255 steps between them. This ns that for an 8-bit DAC with a reference voltage of 10 V the quantization interval resolution) is 10/255 or 39.2 mV. A 12-bit DAC with a reference voltage of 10 V a quantization interval of 10/4095 or 2.4 mV.

The output of a DAC begins to change when it receives a new data value at the input. period required before the output is valid is called the settling time. Generally, ling times are small, being specified in microseconds.

23

#### **input/output assignment**

ch input and output connection point on a PLC has an address used to identify the I/O Each manufacturer uses a proprietary identification system, which is related to the and number of input/output options possible.

The IEC 113 1-3 programming languages standard suggests a method for the direct presentation of data associated with the inputs, outputs and memory of a ogrammable logic controller.' This is based on the fact that a PLC memory is ganized into three regions. These are input image memory (I), output image memory and internal memory (M). Any memory location including those representing I/O is can be referenced directly using

(first letter code) (second letter code)(numeric field)

here the % character indicates a directly referenced variable. The first letter code ecifies the memory region:

- I = input memory

- 0 =output memory

- M = internal memory

ne second letter code specifies how memory is organized:

- X = bit

- B = byte

- W = word

- D = double word

- L = long word

If a second letter code is not given it is assumed to be a bit.

The numeric field component is used to identify the memory location. It supports the oncept of I/O channels since numeric fields can be separated using a period.

Some examples of direct referencing of I/O memory as advocated in the IEC 1131-3 andard are:

- %X1 (\* input memory bit 1 \*)

- %I1 (\* also input memory bit 1 \*)

- %1B2 (\* input memory byte 2 \*)

- %IX1O.4 (\* input byte address 10 bit 4 \*)

- %QX1 (\* output memory bit 1 \*)

Ising names that identify the purpose of each contact and coil in a ladder diagram aids

ability. For example, the contact given the name 'start\_fan' clearly identifies the ose of the input signal. This variable may be the input point directly referenced as K1 (e.g. input memory bit 1). Input and output memory locations can be assigned only on a ladder diagram as shown in Fig. 2.10.

ure 2.10 Assignment of I/O points.

## Keyboard and display

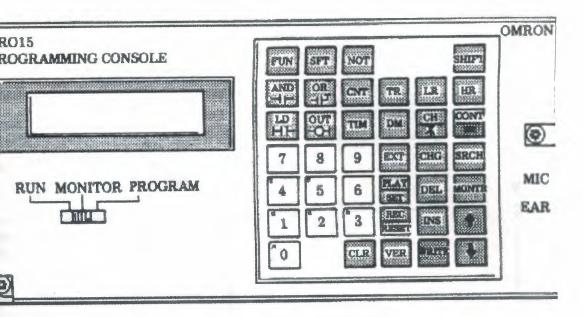

er programs can be entered into RAM using a program console unit consisting of a board and display. Some typical hand-held PLC programming consoles~ orporating liquid crystal displays for viewing ladder code and diagrams are shown in . 2.11.

re 2.11 Typical PLC program consoles.

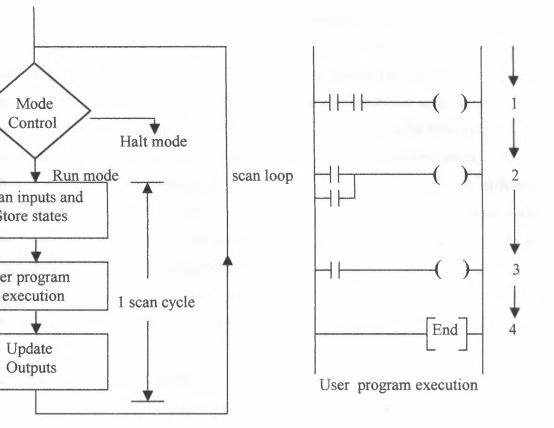

#### **Program execution**

most common approach taken to executing a PLC program is to use a cyclic scan or in program loop such that periodic checks are made on the input values. Figure 2.12 trates the way a ladder program can be executed. The program loop starts by uning the inputs to the system and storing their states in fixed memory locations rred to as input image memory. The ladder program is then executed rung-by-rung, ting at the first rung. Scanning the program and solving the logic of the various ler rungs determine the output states. The updated output states are stored in fixed mory locations referred to as output image memory. The output values held in nory are then used to set and reset the physical outputs of the PLC simultaneously at end of the program scan.

re 2.12 executing a ladder program.

he time taken to complete one cycle is called the cycle or scan time. It depends on ength and complexity (e.g. the number and types of functions used) of the program. equently, manufacturers specify an average value. For example, the average ution speed for Mitsubishi Fl series PLCs is specified as 12 us/step, with a mum program capacity of 1000 steps. This yields an average cycle time of 12 ms 000 steps. The average execution speed for Mitsubishi F2 series PLCs is specified us/step, with a maximum program capacity of 2000 steps (F2-40,60M) and 1000 (F2-20M).<sup>5</sup> This yields an average cycle time of 7 ms for 1000 steps.

can-based execution has a number of limitations when the PLC system has to ond to events within a specified time period. PLC systems, which accommodate rupts, can be used to spontaneously respond to a specific event such as an alarm. Interrupt is a special control signal to the CPU which tells it to stop executing the ram in hand and start executing another program stored elsewhere in memory (i.e. rupts the sequential execution of the ladder program).

#### Multitasking and multiprocessing

nced PLC systems incorporate a processor scheduler to enable multitasking and processing. Multitasking is the running of two or more tasks (also called esses) on a single processor such that they share processor time so that they appear n in parallel. Different tasks of a program can be executed at different rates. equently, time critical tasks (e.g. the monitoring of the state of a limit switch) can wen a high priority and scheduled to be executed within a fixed time period.

ultiprocessing is the running of tasks or processes simultaneously on different essors. In this context a task or process is considered to be a separate code nent, which performs a discrete activity (a program organizational unit, or POU in terminology). With a multiprocessing system, tasks such as 'closed loop PID portional, integral, derivative) control' and 'ladder circuit control' can be mapped separate processors and run concurrently, communicating with one another.

#### **10 Development systems**

C development system would normally comprise a host computer connected via a communications RS232C port to a target PLC. The host computer provides a vare environment to perform editing, file storage, printing and program operation toring. Typically, the process of writing a program to run on the PLC consists of:

sing an editor to write/draw a source program

onverting the source program to binary object code which will run on the PLC's icroprocessor

own loading the object code from the host PC to the PLC system via the serial ommunications port

he editor enables programs to be created and modified on the host computer in r graphical form, such as a ladder diagram, or text form, such as mnemonic code. rres such as cut and paste, copy program block and address search are standard.

#### **CHAPTER 3**

#### Input devices

This chapter provides a brief overview of sensing devices used in manufacturing rocesses. Sensing devices with a digital output can be connected directly to the digital nput port of a PLC. Sensors, which produce an analogue voltage signal, are connected sing an analogue to digital converter.

#### **3.1 Digital devices**

The operation of a PLC may be based on signals received from digital switching levices, which detect an event occurring. For example, the presence of an object on a conveyor belt can be detected using a proximity switch or a photoelectric detector. Some commonly used digital switching devices are described below.

#### **3.1.1** Pressure and temperature switches

Pressure switches monitor pressure and have a contact which changes state when a preet pressure threshold value is reached. When the pressure level falls below the threshold alue the contact resumes its initial position. Pressure switches are used in pneumatic and avdraulic applications.

Thermostats monitor temperature<sup>1</sup> and have a contact which changes state when a pre-set emperature threshold value is reached. When the temperature value falls below the hreshold value the contact resumes its initial position. Thermostats are used in a wide ange of applications including the temperature monitoring and control of machines and eating installations. Many thermostats incorporate some hysteresis, which means that they switch on and off at different temperatures. This is referred to as differential regulation etween two threshold values.

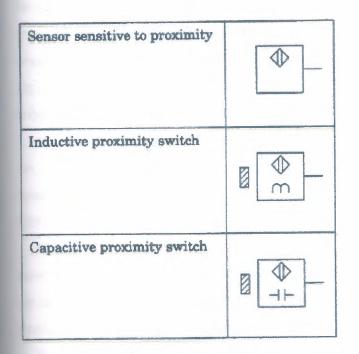

#### **3.1.2 Proximity switches**

Proximity switches are used for non-contact object detection. They integrate a Sensing

element and a transistor switch output circuit. The output changes state. When the object is in the vicinity of the sensor element. Proximity switches are classified as either inductive or eapacitive, which relates to the type of sensing technology used. Inductive types are suitable for detecting ferrous and non-ferrous metals.

Figure 3.1 The IEC graphical symbols for proximity switches.

Capacitive types will sense the presence of almost any material. The IEC symbols used to represent proximity switches are shown in Fig. 3.1.

The principle of operation of an inductive proximity switch is based on the generation of an alternating magnetic field, which is affected by a metal object passing within its range. A typical device would have a sensing range of 2 mm and a switching speed of 800 Hz. The principle of operation of a capacitive device is based on generating an electric field, which is modified by any object passing within its range. A typical device would have a sensing range of 1—10 mm (adjustable) and a switching speed of 400 Hz.

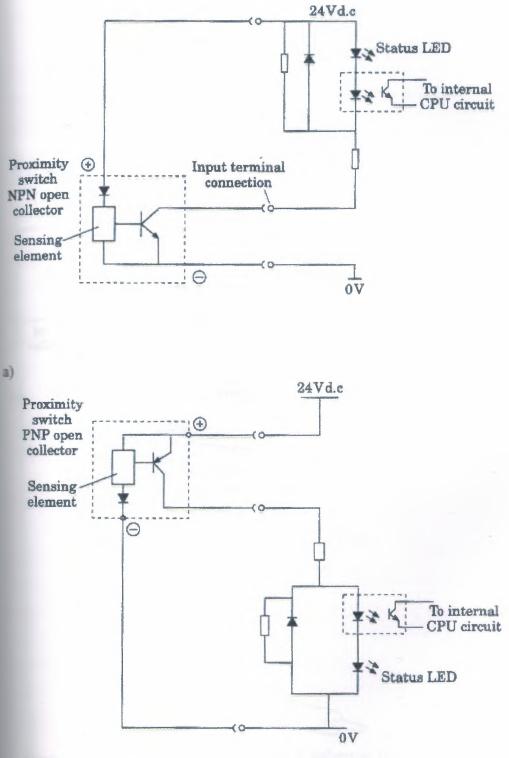

The d.c. switching proximity devices are available with NPN open collector and PNP open collector transistor output stages. Figure 3.2 illustrates how to connect an NPN transistor output to a PLC sink input circuit and a PNP transistor output to a PLC source

input circuit.

#### 3.1.3 Photoelectric switches

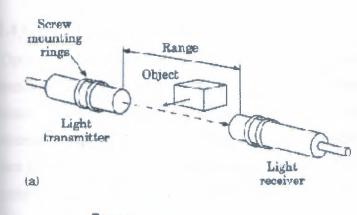

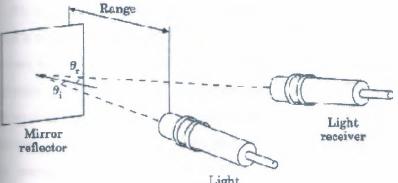

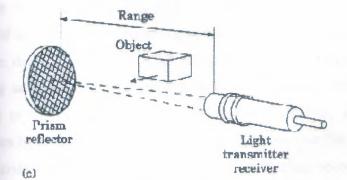

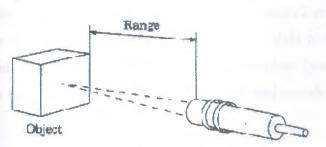

Photoelectric devices consist of a light source and a photo-receiver incorporating a transistor switch circuit. PNP and NPN transistor output devices are available. The ways in which the light source and photo-receiver can be set up to detect objects are illustrated in Fig. 3.3. Photoelectric switches are categorized as being either through beam, mirror reflection, retro-reflective or diffuse reflective.

The through-beam type of photoelectric system has a separate transmitter and receiver. An object is detected when it breaks the light beam. The through-beam photoelectric detector can be used for long-range sensing. A typical device would have a sensing range of 8000 mm.

A plane surface mirror can be used to reflect back the transmitted light beam to the receiver. In this case, the object is detected when the reflected beam is broken. With a plane mirror reflector, the transmitter and receiver must be mounted such that the angle of incidence equals the angle of reflection.

The retro-reflective type of photoelectric switch uses a special type of reflector which returns transmitted incident light back in the same direction from which it was sent. This allows the transmitter and receiver to be incorporated in the same housing. With proper alignment of the photoelectric device to the reflector a typical device would have a sensing range of 2000 mm.

If a parallel beam of light is incident on a sheet of paper the light is reflected in all directions because the surface is not perfectly smooth like that of a mirror. This is an example of diffuse reflection. A diffuse reflective type of photoelectric switch contains a transmitter and receiver in the same housing and switches when the diffuse reflection level exceeds a threshold value. A typical device would have a sensing range of 100 mm.

b)

Figure 3.2 Connecting NPN and PNP transistor output proximity switches: (a) Sink input circuit connection and (b) source input circuit connection.

(b)

Figure 3.3 (a) through beam (b) mirror reflection (c) retro-reflection (d) diffuse reflection

#### 3.1.4 Optical switches

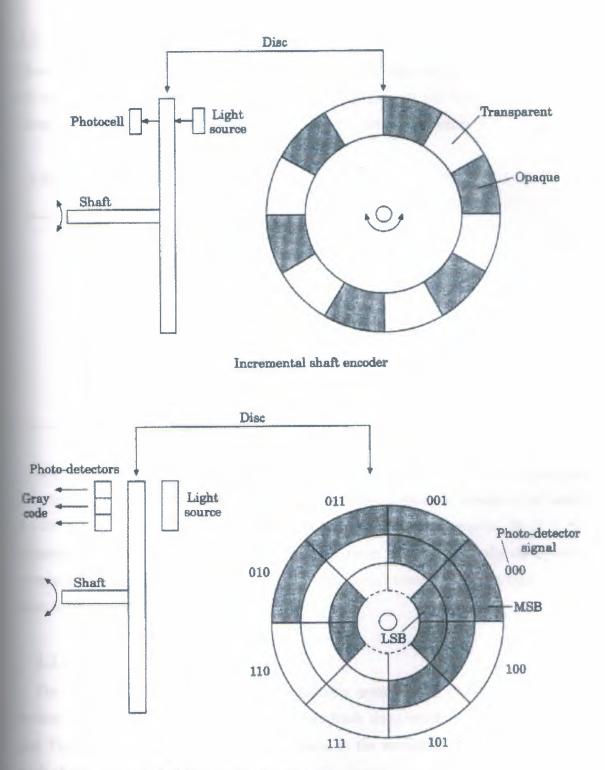

Optical encoders convert either translation or rotary displacement into digital information. They operate by using a grating, which moves between a light source and detector. There are two forms of optical encoder, namely incremental and absolute. Incremental encoders produce a pulse for each resolvable change in position. Counting pulses from some reference point can make a relative measurement of position. Absolute encoders produce a unique coded number for each resolvable position.

An example of an incremental shaft encoder is shown in Fig. 3.4. The grating is a disc with a single concentric track of evenly spaced opaque and transparent regions. When light passes through a transparent region of the grating an output is obtained from the photodetector. When the shaft is turned, the disc rotates and chops the light beam so that the photo-detector produces a series of electrical pulses. Position is measured by counting the number of pulses generated by the photo-detector as the disc rotates from a reference point. By incorporating two tracks shifted by a quarter-cycle relative to one another and two photo-detectors it is possible to produce two signals from which the direction of rotation can be determined by noting which signal rises first. If a motor the pulse rate drives the shaft of an incremental encoder is proportional to the motor's speed.

The disc of an absolute shaft encoder has several concentric tracks, with each track having an independent light source and photo-detector. With this arrangement a unique binary or Gray coded number can be produced for every shaft position. The Gray code changes by a single bit between successive positions (see Fig. 3.4). Table 3.1 compares the Gray code with binary code. Resolution of an absolute encoder depends on the number of racks (bits). For example, a 3-bit binary output produces 2 or 8 resolvable positions.

Linear encoders use a grating in the form of a slide to make a measurement of "near movement. They may be of incremental or absolute type. Rotary and linear absolute encoders read actual position and unlike incremental encoders they do hot need a counting device.

Figure 3.4 incremental and absolute snail encoders.

### 3.2 Analogue devices

Many applications involve monitoring analogue signals representing the variation of a physical quantity. For example, the variation of displacement can be measured using a linear variable differential transformer (LVDT), which converts a position

| Binary | Gray |

|--------|------|

| 0000   | 0000 |

| 0001   | 0001 |

| 0010   | 0011 |

| 0011   | 0010 |

| 0100   | 0110 |

| 0101   | 0111 |

| 0110   | 0101 |

| 0111   | 0100 |

## Table 3.1 Binary and Gray codes

A typical PLC analogue input unit will accept either voltage or current signals (see Chapter 2). Current input ranges for data acquisition are commonly configured to accept -20 mA or 0-20 mA signals. Voltage input ranges can be unipolar (0-5 V for example) or bipolar ( $\pm 5 \text{ V}$  for example). The input range is selected (usually via a jumper connection) to match the sensor signal variation. Some examples of analogue voltage sensors are described below.

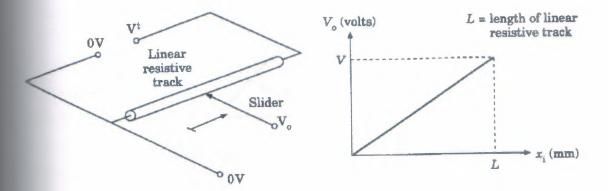

### 3.2.1. linear potentiometer

The linear potentiometer is used for measuring position and displacement. Modem devices consist of a printed circuit linear resistive track along which a slider makes contact (see Fig. 3.5). The slider is mechanically linked to the movement being measured. The rack of resistive material is connected across a d.c. Supply V. Assuming that the resistance is distributed linearly along the length L of the track the output voltage  $V_0$  from the slider can be written as

$$V_o = \frac{x_i}{L}V = Kx_i$$

The output voltage is directly proportional to the position of the slider along the track.

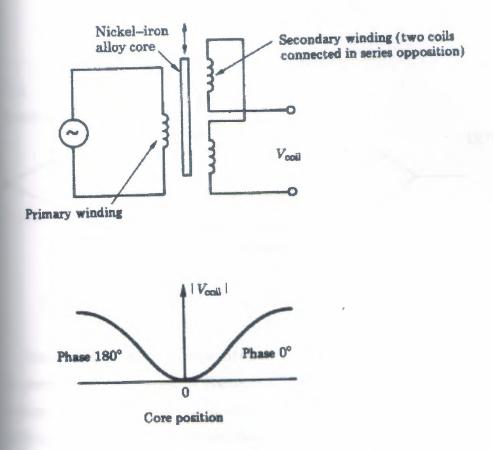

### 3.2.2. Linear variable differential transformer

The linear variable differential transformer, or LVDT, is a displacement transducer. It consists of a nickel-iron rod which is free to move through primary and secondary coils. The basic arrangement is illustrated in Fig. 3.6.

Figure 3.5 Linear potentiometer.

The primary coil is fed with alternating current so that voltages are induced in the two lalves of the secondary coil. Moving the rod up and down changes the phase and voltage in secondary windings. The output voltage versus core displacement characteristic in Fig. 56 shows that the phase of the output (secondary winding) relative to the input (primary inding) changes by 1800 as the core is moved through the central position. Consequently, phase detector is required to obtain an output for each core position.

Figure 3.6 Linear variable differential transformer (LVDT).

### 3.2.3 Tachogenerator

When the shaft of a permanent magnet d.c. motor is driven mechanically an output oltage is produced whose magnitude is proportional to the speed of rotation and polarity depends on the direction of rotation. A permanent magnet d.c. motor used for speed sensing ather than a machine for producing power is called a tachogenerator. Low-pass filtering is required to reduce the ripple voltage superimposed on the output.

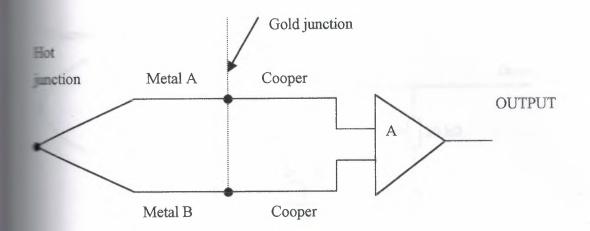

### 3.2.4 Temperature sensor

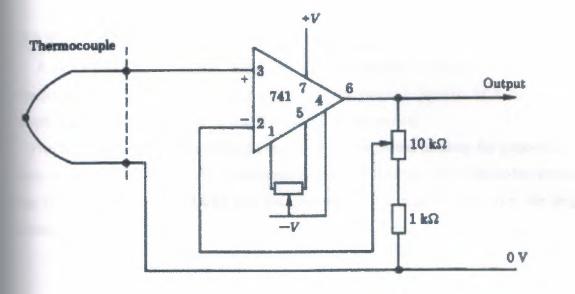

A thermocouple is a device that converts temperature into a voltage. It consists of two dissimilar wires, which are arranged as shown in Fig. 3.7. Thermoelectric effects produce roltage as the hot junction is heated. Thermocouple types are designated a letter which indicates the types of metals used in the thermocouple injunction (seeFig.3.7).

Figure 3.7 Thermocouple.

Thermocouples are non-linear devices, which means that their output voltage is not reportional to temperature. A Thermocouple is supplied with a calibration table of output oltages versus temperature. The output voltage produced by a thermocouple is at the illivolt level and needs to be amplified before it can be fed into an ADC unit. A simple remocouple amplifier circuit based on the 741 Operational amplifiers is shown in Fig. 38.

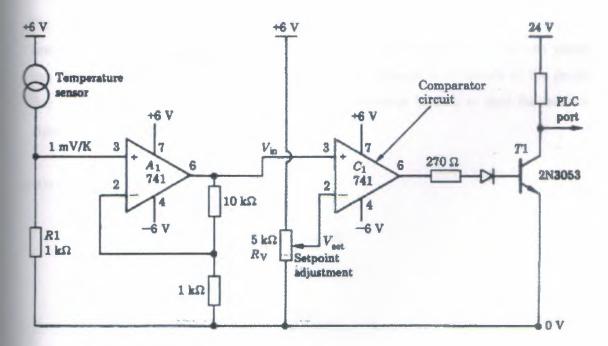

Semiconductor temperature sensors (e.g. RS590) are commercially available which can generate current as temperature is increased. A typical device would have a temperature coefficient of 1  $\mu$ AIK and operate in the temperature range of 218-403 K.

Figure 3.9 shows a temperature switch circuit based on a semiconductor temperature sensor. The circuit converts sensor current into voltage using the resistor R1. This voltage amplified by the operational amplifier circuit and fed to a comparator. The comparator roduces an output signal when the temperature Voltage input is equal to or greater than the threshold level set by Vset. In this the comparator output level turns on the transistor switch based on T1. The transistor switch Ti allows 24 V to be applied to the PLC digital input point. Note that the output to the PLC port is held on until a base current flows in T<sub>1</sub>

Figure 3.8 Simple thermocouple amplifier circuit

Figure 3.9 Temperature switch circuit.

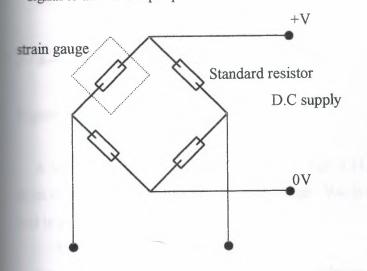

#### 3.2.5 Strain gauge

A strain gauge is a transducer whose principle of operation is based on the variation of resistance with dimensional displacement. A strain gauge is bonded to a surface of a mechanical element (e.g. a bar) in which strain is to be measured.

Provided that the variation in length under loaded conditions is along the piige-sensitive axis an increase in load causes an increase in gauge resistance. The relationship between the change in resistance  $(\Delta R/R)$  and the corresponding change in strain (i.e. the length change  $(\Delta L/L)$  is

$$G = \frac{\Delta R / R}{\Delta L / L}$$

where G is called the gauge factor. ~The gauge factor is about 2 for wire element metal alloy strain gauges and about 100 for semiconductor strain gauges.

A strain gauge is normally connected in a Whetstone bridge arrangement as shown in Fig. 3.10. The bridge is balanced under no load conditions so that any change in resistance due to loading unbalances the bridge and a signal is detected. A dummy gauge can be connected in the bridge to compensate for the change in resistance of the gauge due to temperature variations. An instrumentation amplifier is used to feed the balance signal to an ADC input point.

Figure 3.10 Strain gauge bridge.

#### **3.3 Basic interfacing techniques**

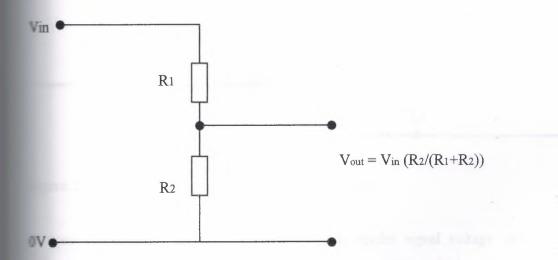

The voltage signal from a sensor will need to be matched to the specified voltage range and internal resistance of an ADC input port. A typical input port specification is an internal resistance of 200 k $\Omega$  for an input range of 0-5 V.

Matching the signal source voltage level to that of the input specification may require reducing or amplifying the voltage of the signal source. If the signal Source voltage ranges between -2.5 and +2.5 V (i.e. a bipolar signal) it will need to be converted into the range 5 V (i.e. a unipolar signal) before connect leg to an input specified at 0 5V. It is also recessary to ensure that the

Resistance (i.e. impedance) of the signal source is less than or equal to that of the input specification. An impedance changing circuit (e.g. emitter follower) may be required.

#### Figure 3.11 Voltage divider.

A voltage (potential) divider, as shown in Fig. 3.11, can be used to reduce tF voltage level of a transducer signal. The output voltage V<sub>out</sub> is always less than ii input voltage V<sub>in</sub> and is given by

#### $V_{out} = V_{in} (R_2/(R_1+R_2))$

Small signal amplifiers are used to amplify voltages at the micro volt to millivolt level.

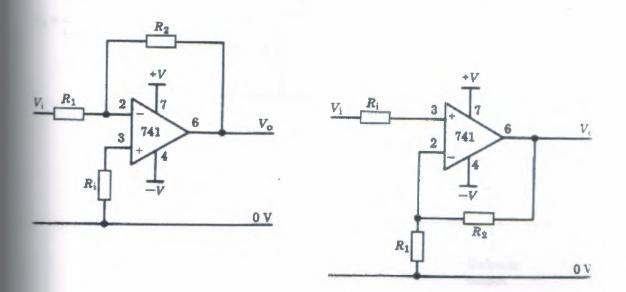

Figure 3.12 shows circuits for inverting and non-inverting amplifiers base around a 741 operational amplifier. The ratio of the output voltage V<sub>out</sub> to the input voltage V<sub>in</sub> is called the gain of the amplifier. The inverting amplifier has a gain  $R_2/R_1$ . The non-inverting amplifier has a gain of  $(R_2+R_1)/R_1$ . The resistance R<sub>1</sub> in these circuits ensures that both inputs to the operational amplifier see the saw resistance to 0 V and is calculated using

$R_1 = (R_1R_2) / (R_2 + R_1)$

Figure 3.12 (a) Inverting and (b) non-inverting amplifiers.

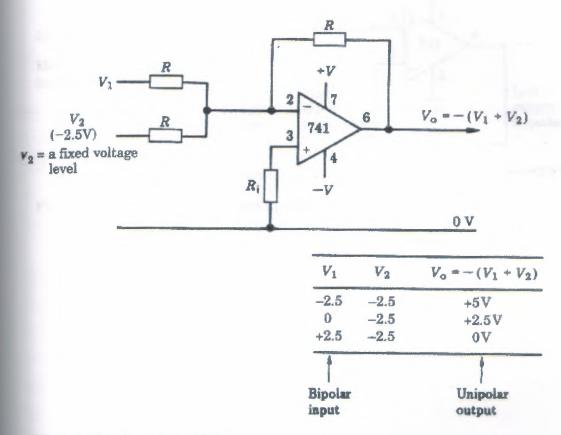

A summing amplifier can be used to convert a bipolar signal voltage into a umpolar voltage. Figure 3.13 shows a circuit for a summing amplifier which makes use of a 741 operational amplifier. The output voltage Vout is given by

If the summing amplifier is to convert a bipolar signal voltage into a unipolar Voltage, one of the inputs must be held at an appropriate negative voltage. For example, if  $V_2$  is held 2.5 V, then summing action ensures that the voltage range 2.5 to  $\pm 2.5$  V is converted into the unipolar voltage 5 - 0 V.

Figure 3.13 Summing amplifier.

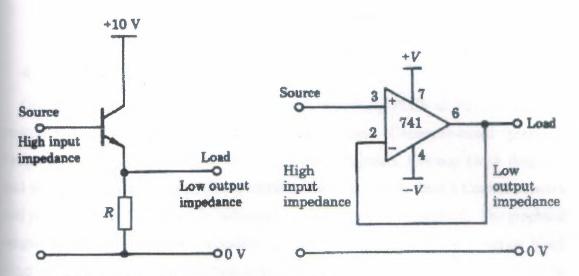

The emitter follower and voltage follower (a unity gain non-inverting amplifier) Used as impedance matching circuits. Figure 3.14 shows circuits for the emitter and voltage follower. In these circuits the output voltage follows the Voltage (e.g. from the signal source). The main characteristic of both circuits the input impedance is high and the output impedance is low. Consequently, they can be used as a buffer between a sensor and ADC port to ensure that the impedance matching criteria is met. Buffer amplifiers are also used for interfacing low current Sensors.

A document of any the concept of a second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second se

throughout this berelegang small- and annual backler and the question for 5 monted at a loss the correct of a loss

#### **CHAPTER 4**

## **Programming methods**

#### 4.1 Graphical languages

Graphical languages are widely used for programming PLCs as they are easy yet powerful tools for developing control applications. Computer-based graphical Programming packages exist for designing ladder diagrams, function block diagrams and sequential function charts. These literally allow the user to draw a Control network and provide a visual image of the solution to a particular control problem. The graphical languages defined in the IEC standard are ladder diagram. (LD) and function block diagram (FBD). Sequential function chart (SFC elements are also defined and can be used in conjunction with either of these languages.

A circuit network can be considered as a set of interconnected graphical elements representing a control plan. Graphical languages are used to represents the flow of a conceptual quantity through a network. With a ladder diagram network the conceptual quantity is power flow and the direction of power flow defined to be from left to right. With a function block diagram network the concern of signal flow is applied and the direction of signal flow is defined to be from the output side to the input side of connected function blocks or functions. With sequential function chart the concept of activity flow is applied. Activity flow between SFC elements is from the bottom of a step through the appropriate transition to the top of the following step.

### 4.1.1 Ladder diagram (LD)

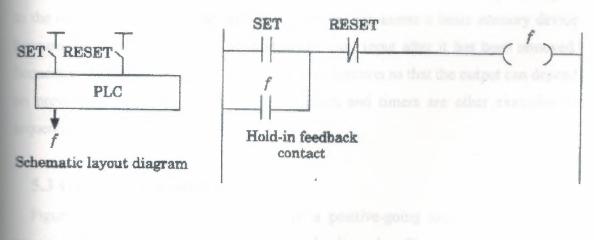

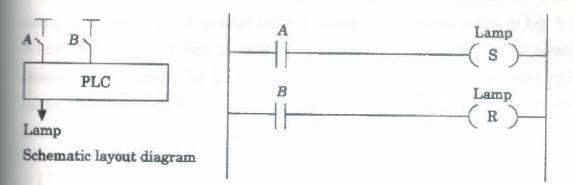

The ladder diagram method has been used throughout this book, as it is the predominant programming method for developing small- and medium-scale PD applications. The IEC standard is based on terminology and symbols as used b the majority of current PLC systems. The IEC standard ladder diagram graphic~ symbols are shown in Table4.4. The standard includes symbols for SET RESET coils, which allow a variable to be latched on, and then cleared at a late stage. Retentive coils (e.g. coils whose Boolean states need to be held during PL power interruption) are also defined.

Function blocks having Boolean inputs and outputs can be connected within ladder diagram. Functions used in a ladder diagram may have an execution enable (EN) input and an execution enable output (ENO). When EN is true the function is evaluated. When EN is false it remains inactive. A ENO is taken high on if successful completion of a function. It is possible to connect an ENO output to a EN of another function to provide execution control.

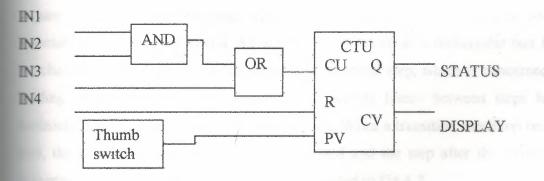

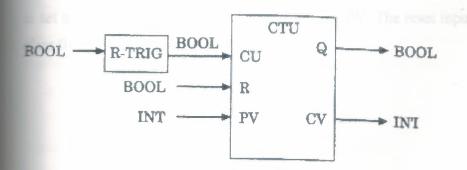

#### 4.1.2 Function block diagram (FBD)

The function block diagram (FBD) is a graphical language whereby programs are expressed as a set of interconnected function blocks. An analogy cans h drawn with a system circuit diagram where connections represent signal (FBD) paths. Each function block is represented as a rectangular block with input Drawn so that they enter on the left side and outputs drawn so that they exit o the right side. Signal flow is from an output of one function block to the input of another function block. An example of a function block diagram is shown in Fig. 4.1.

Figure 4.1 Example of a function block diagram (FBD).

The IEC standard defines a small number of standard function blocks which are the SR bitable, RS bitable, rising edge detector, falling edge detector, edge detecting

inputs, up-counter, down-counter, up-down counter, pulse timer, on delay timer, offdelay timer and real-time clock. These are shown in Table 4.5. Other special purpose blocks such as PID and ramp blocks can be designed using the ST language.

The FBD language is suited to Boolean logic and continuous (e.g. closed-loop) control applications. Although it is possible to construct a 'jump' within an FBD using a label identifier, the IEC does not recommend its use. Constructs such as IF/THEN/ELSE used with the structured text language are difficult to represent graphically within an FBD. Consequently, direct translation between ST and FBD is not always possible.

### 4.2 Sequential function chart (SFC)

The IEC 1131-3 standard describes the use of a graphical sequencing language referred to as the sequential function chart. This is based on Grafcet, a graphical language for developing sequential control programs, and defined as a French national standard. Telemecanique PLCs use the Grafcet language but most major PLC systems provide an option for sequential programming. In fact, the IEC 1131-3 standard uses an existing IEC standard to describe a graphical language for control sequences.

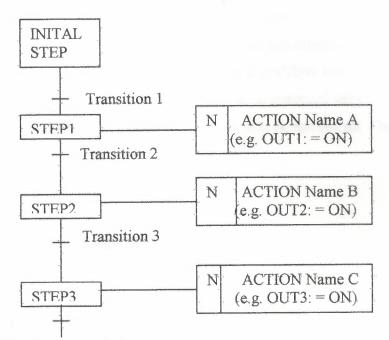

A sequence can be thought of as a series of steps that occur in a defined order. The sequential function chart language represents each step as a rectangular box, which is associated with a control action. An action can be drawn as a rectangular box that is attached to a step. Every sequence starts with an initial step, which is concerned with holding the system ready for operation. Connecting lines~ between steps have a horizontal bar representing a transition condition. When a transition condition becomes true, the step before the transition is deactivated and the step after the transition is activated. The main features of an SFC are illustrated in Fig.4.2.

Figure 4.2 Sequential function charts.

Steps are always separated by a transition and every transition must have a Boolean condition, which can be true. Every action and transition should be given a unique name within a program.

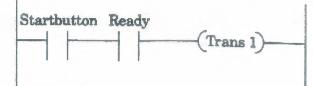

The software to implement transition conditions and actions can be written using any of the IEC languages. An example of a transition condition (Trans 1) written in ST is

TRANSITION Transl:

: = Startbutton AND Ready;

END TRANSITION

The same transition is shown as a Ladder Diagram in Fig.4.3. A transition can involve a timer (e.g. wait for an elapsed time to occur), a counter or any other type of function block.

An example of a simple action written in ST is

ACTION Name A

OUT1: =ON;

END\_ACTION

The action called 'Name A' sets OUT1 to an ON state. The action will occur as a result of an associated step (e.g. STEP 1 in Fig. 4.2) being activated.

An action can have a qualifier, which determines the way in which the action will be executed. An action qualifier is drawn as a rectangular box attached to the left hand side of an action as shown in Figure 4.2. Commonly used qualifiers are N (none), S (set) and R (reset). An N qualifier specifies that the action is executed only while the step is active. An S (set) qualifier specifies that the action is to be latched on. The step acts as a trigger for the latch and the action is said to be

### **TRANSITION Trans 1**

### END\_TRANSITION

#### Figure 4.3 Ladder diagram transition expression.

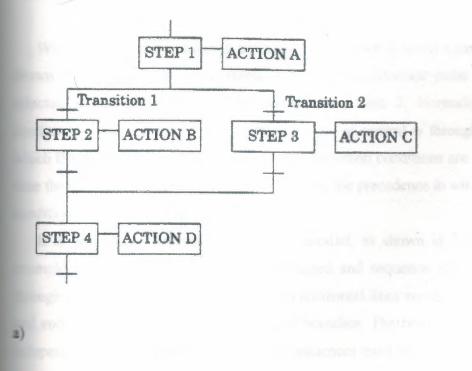

Only one path is selected. Normally transition conditions are tested from left to right but precedence can be user defined 'stored' since it will continue as the control sequence progresses. A set or stored action is cleared using an R (reset) qualifier.

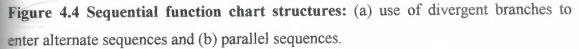

Within an SFC it is possible to use a divergent branch to select a path option. This is shown in Fig. 4.4(a). In this example, there are two alternate paths which could be selected according to the transition conditions 1 and 2. Normally the transition conditions are tested from left to right. The flow of control is through the branch for which the transition condition is true. If both transition conditions are true at the same time then the left-hand branch is taken. However, the precedence in which the transition conditions are tested can be user defined.

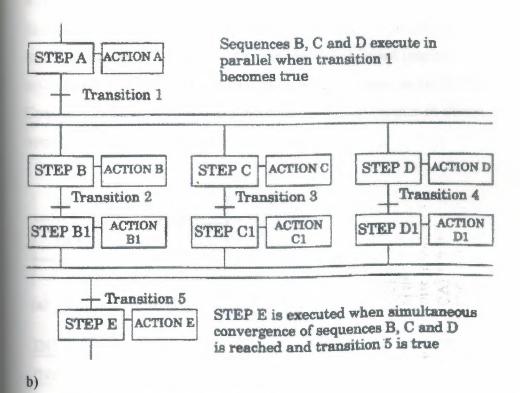

It is possible to activate sequences in parallel, as shown in Fig. 4.4(b). In this example, two parallel branches are constructed and sequence flow is simultaneous through the two branches. A pair of parallel horizontal lines are used to denote the start and end of the simultaneous sequencing of branches. The branch sequences continue independently. Convergence of the branch sequences must be obtained before they can be combined into one sequence.

### 4.3 Translating between languages

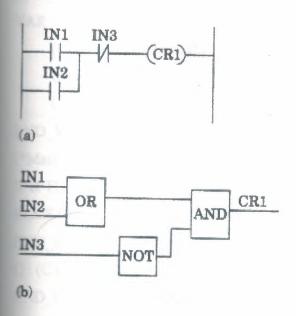

Simple ladder rungs involving combinational logic can usually be translated into FBD or ST, as illustrated in Fig. 4.5. The IEC 1131-3 standard specifies the operation of the up-counter, down-counter and up-down counter in terms of an ST language algorithm. Consider the function block representation of the up-counter as shown in Fig. 4.6. The operation of the up-counter function block can be.

Figure 4.5 Translating a ladder diagram into other IEC languages: (a) ladder diagram, (b) function block diagram and (c) structured text.

Figure 4.6 Up-counter function block.

FUNCTION BLOCK CTU

VAR INPUT

(\*data type of inputs\*)

CU: BOOL R\_TRIG;

R:BOOL;

PV : INT;

(\*CTU is an abbreviation for Count Up\*)

(\*Count input on rising edge transition\*)

(\*Reset\*)

(\*Preset value\*)

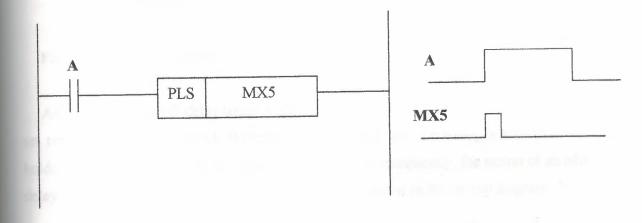

```

END_VAR

```

VAR\_OUTPUT

(\*data type of outputs\*)

Q:BOOL;

CV: INT;

(\*Current output\*) (\*Counter count value\*)

END VAR

(\*Main body of function block\*)

**IF R THEN CV**: 0;

ELSIF CU AND (CV < PV) THEN CV:=CV+1;

END IF;

$Q:(CV \ge PV);$

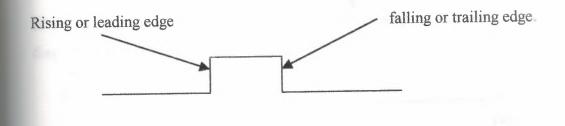

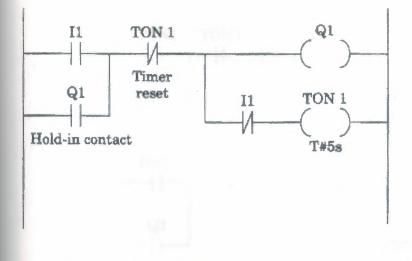

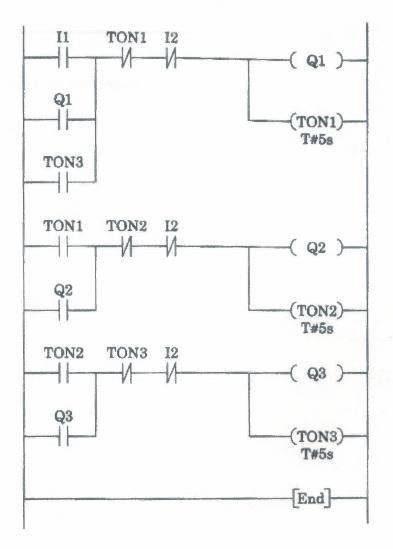

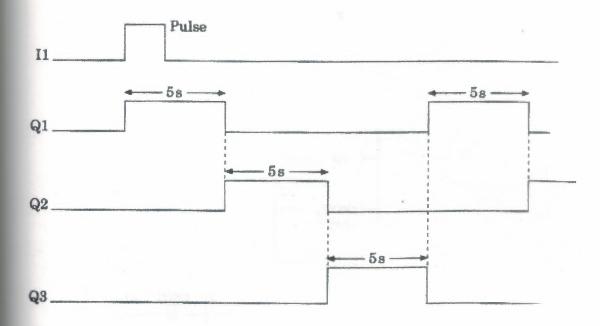

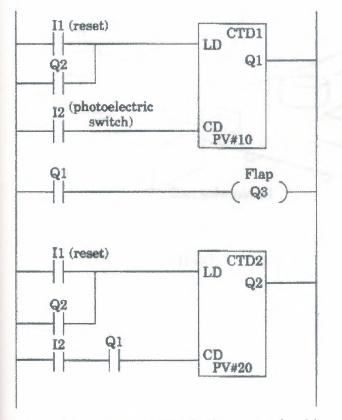

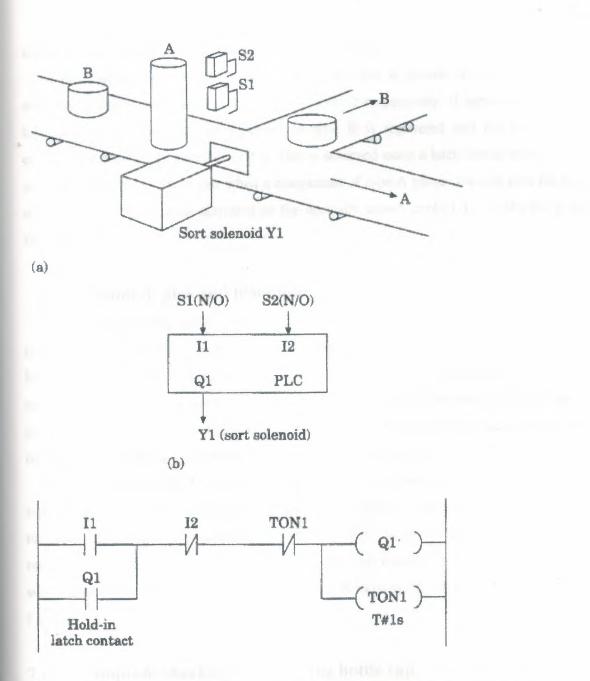

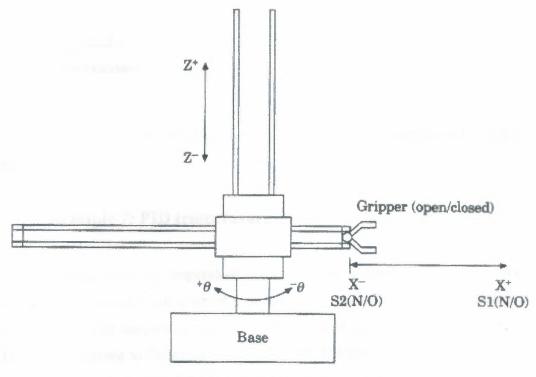

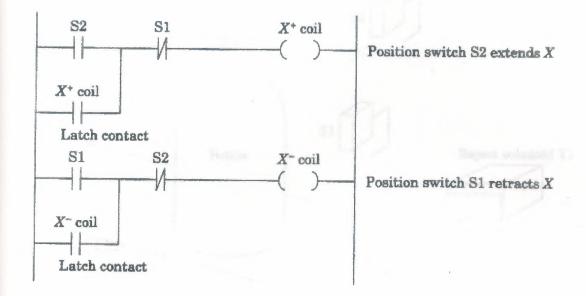

END FUNCTION BLOCK