# NEAR EAST UNIVERSITY

# **Faculty of Engineering**

# Department of Electrical and Electronic Engineering

# CONTROL ELECTRIC COUNTERS WITH PLC DEVICE

Graduation Project EE-400

Student:

Buğra Tansu (20000275)

Supervisor:

Mr. Özgür Özerdem

Lefkoşa-2001

### ACKNOWLEDGMENTS

First I want to thank Mr. Özgür Özerdem to be my advisor. Under his guidance, I successfully overcome many difficulties and learn a lot about PLC's. In each discussion, he explained my question patiently, and I left my quick progress from his advises. He always help me a lot either in my study. I asked him many questions in PLC's and he always answered my question quickly and in detail.

Special thanks to Cemal. With he kind help, I could use Step7-Microwin16, which is called Simatic successfully to perform computational problem. Thanks to faculty Engineering for having such a good computational environment.

I also want to thank my friends in NEU: Bora, Mertsan, Türkay and Cüneyt.

Finally, I want to thank my family, especially my parents. Without their endless support and love for me, I would never achieve my current position.

### ABSTRACT

My project aim is control the electric counter with PLC device and CPU 212. First step sensor read the red point on the electric counter and to work out the units that are connected to the counter when they reach the value that we determine.

I can do PLC device with STEP 7-Micro/WIN programming. STEP 7-Micro/WIN is a programming software application for the S7-200 family of programmable logic controllers.

When programming in statement list (STL), in order to ensure that your user program will also display, compile, and run correctly in ladder (LAD).

STEP 7-Micro/WIN automatically compiles a project when you perform a project download. Components that fail to compile will not be downloaded.

The STEP 7-Micro/WIN STL compiler checks all lines for proper comment syntax, makes sure the program contains valid instruction names with the correct number of parameters, and verifies that correct address identifiers are used.

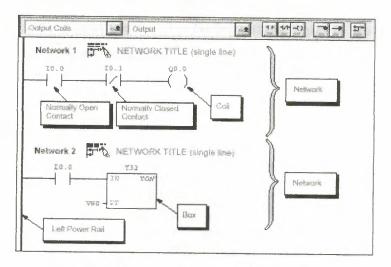

In LAD programs, the basic elements of logic are represented with contacts, coils, and boxes. A set of interconnected elements that make a complete circuit is called a network.

STL program elements are represented by a set of instructions for performing the desired functions.

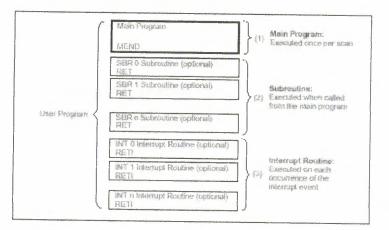

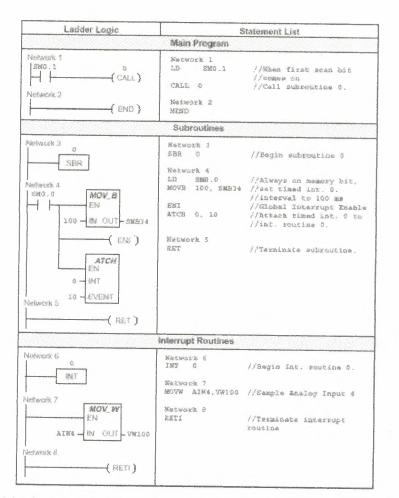

S7-200 programs consist of a main user program that may be followed by subroutines and/or interrupt routines. The main program is terminated by an unconditional END (MEND in STL).

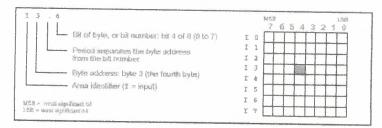

When writing your program, you can use either of two modes of addressing instruction operands; direct or indirect.

Direct addressing specifies the memory area, size, and location, you can address indirectly the data types Q, M, T, C, V, and I.

The user memory in the S7-200 CPUs consists of three blocks; program, data, and configurable parameters.

### **INTRODUCTION**

A PLC (i.e. Programmable Logic Controller) is a device that was invented to replace the necessary sequential relay circuits for machine control. The PLC works by looking at its inputs and depending upon their state, turning on/off its outputs. The user enters a program, usually via software, that gives the desired results.

The first chapter represent, history of PLC and communication began to appear in approximately 1973. The first such system was Modicson's Modbus.

In chapter two, the PLC mainly consists of a CPU, memory areas, and appropriate circuits to receive input/output data.

Chapter three represents, a PLC works by continually scanning a program.

The fourth chapter explain ladder diagram with give examples and explain how we can understand truth table.

Chapter five present, the CPU 212 is the low-cost entry into the SIMATIC S7-200 family; explain functions and how we can use programming.

In chapter six, the S7-200 series is a line of micro-programmable logic controllers that can control a variety of automation applications and explain S7-200 Programming Language.

Chapter seven present direct addressing, counter and timer.

Chapter eight present of the project.

Chapter nine explains part of processing unit and advantages of PLC.

In TRNC PLC devices are used, in local newspaper, medicine factory and washing machine room in a hotel.

PLC is very expensive, but they occupy small area and we can change their program.

PLC is used in communication are widely.

r

Nowadays, PLC, PC and relay systems are used in the control of Industrial Machines. From two type of PLCs, although the compact PLC cheaper than the modular PLC, modular PLC is used widely rather than compact PLC.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS                           | i   |

|-------------------------------------------|-----|

| ABSTRACT                                  | ii  |

| INTRODUCTION                              | 111 |

| CHAPTER 1                                 |     |

| PLC HISTORY                               | 1   |

| 1.1 First Introduced                      | 1   |

| 1.2 Control System                        | 1   |

| 1.3 Mid70's the dominant PLC technologies | 1   |

| 1.4 Communications                        | 2   |

| CHAPTER 2                                 |     |

| PLC MAINLY CONSIST                        | 3   |

| 2.1 What does each part do?               | 3   |

| 2.1.1 Input Relays (contacts)             | 3   |

| 2.1.2 Internal Utility Relays (contacts)  | 3   |

| 2.1.3 Counters                            | 3   |

| 2.1.4 Timers                              | 4   |

| 2.1.5 Output Relays (coils)               | 5   |

| 2.1.6 Data Storage                        | 5   |

| CHAPTER 3                                 |     |

| PLC OPERATION                             | 6   |

| 3.1 PLC Scanning                          | 6   |

| 3.1.1 Check Input Status (step1)          | 6   |

| 3.1.2 Execute Program (step 2)            | 6   |

| 3.1.3 Update Output Status (step 3)       | 6   |

| 3.2 Response Time Concerns                | 7   |

| 3.2.1 Pulse Stretch Function              | 8   |

| 3.2.2 Interrupt Function                  | 8   |

# **CHAPTER 4**

| PLC REGISTERS                                                          | 10  |

|------------------------------------------------------------------------|-----|

| 4.1 Ladder Diagram and PLC Registers                                   | 10  |

| 4.2 Truth Table                                                        | 11  |

| 4.3 The Program Scan                                                   | 12  |

| CHAPTER 5                                                              |     |

| CPU 212                                                                | 15  |

| 5.1 Overview                                                           | 15  |

| 5.2 Area of application                                                | 15  |

| 5.3 Design                                                             | 15  |

| 5.4 Functions                                                          | 16  |

| 5.5 Programming                                                        | 18  |

| CHAPTER 6                                                              |     |

| S7-200 MICRO PLC                                                       | 19  |

| 6.1 Introducing the S7-200 Micro PLC                                   | 19  |

| 6.2 Comparing the Features of the S7-200 Micro PLCs                    | 19  |

| 6.2.1 Equipment Requirements                                           | 19  |

| 6.2.2 Capabilities of the S7-200 CPUs                                  | 20  |

| 6.3 Major Components of the S7-200 Micro PLC                           | 21  |

| 6.3.1 S7-200 CPU Module                                                | 21  |

| 6.4 Installing and Using the STEP 7-Micro/WIN Software                 | 22  |

| 6.5 Installing the Step 7-micro/win software                           | 22  |

| 6.5.1 Pre-Installation Instruction                                     | 22  |

| 6.5.2 Installation Instruction for windows 3.1                         | 23  |

| 6.5.3 Installation instruction for Windows 95 or windows NT 4.0        | 23  |

| 6.5.4 Troubleshooting the Installation                                 | 24  |

| 6.6 Using STEP7-Micro/WIN to set up to the Communications Hardware     | 24  |

| 6.6.1 General Information for Installing or Removing the Communication | ons |

| Hardware                                                               | 24  |

| 6.7 Special Hardware Installation Information for Windows NT Users     | 25  |

| 6.8 Establishing Communication with the S7-200 CPU                | 26 |

|-------------------------------------------------------------------|----|

| 6.8.1 Connection Your Computer to the S7-200 CPU                  |    |

| Using the PC/PPI Cable                                            | 26 |

| 6.8.2 Connecting your computer to the S7-200                      |    |

| Using the MPI or CP Card                                          | 27 |

| 6.8.3 From what point do I set up Communications?                 | 29 |

| 6.9 Setting Up Communication within STEP 7-Micro/WIN              | 29 |

| 6.10 Setting up communication from the Windows Control Panel      | 30 |

| 6.11 Setting up communication during installation                 | 31 |

| 6.12 Selecting the correct module parameter set and setting it up | 31 |

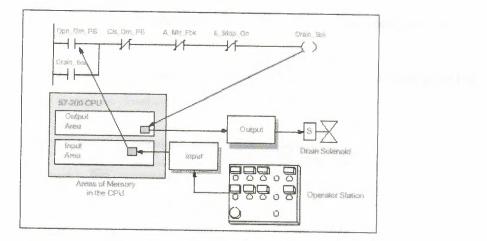

| 6.13 Concept of an S7-200 Program                                 | 32 |

| 6.13.1 Relating the program to inputs and outputs                 | 32 |

| 6.14 Concepts of the S7-200 Programming Languages                 | 33 |

| 6.14.1 Understanding the basic elements of ladder logic           | 33 |

| 6.14.2 Understanding the statement list instruction               | 34 |

| 6.15 Basic Elements for Constructing a Program                    | 35 |

| 6.15.1 Organizing a Program                                       | 35 |

| 6.15.2 Example Program using subroutines and interrupts           | 37 |

| 6.16 Selecting the Mode of Operation for the CPU                  | 37 |

| 6.16.1 Changing the operating mode with the mode switch           | 38 |

| 6.16.2 Changing the operating mode with STEP7-Micro/WIN           | 38 |

| 6.16.3 Changing the operating mode from the program               | 38 |

| CHAPTER 7                                                         |    |

| DIRECT ADDRESSING                                                 | 39 |

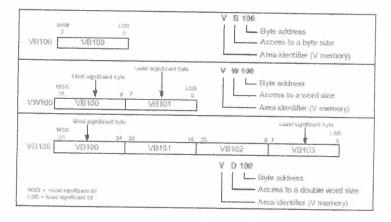

| 7.1 Direct Addressing of the CPU Memory Areas                     | 39 |

| 7.1.1 Using the Memory Address to Access Data                     | 39 |

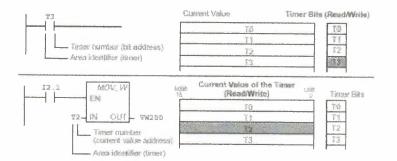

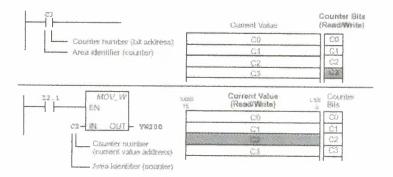

| 7.2 Timers and Counter                                            | 40 |

| 7.2.1 Addressing the Timer Memory Area                            | 40 |

| 7.2.2 Addressing the Counter Memory Area                          | 41 |

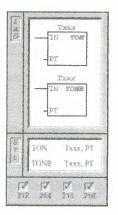

| 7.2.3 On-Delay Timer, Retentive On-Delay Timer                    | 42 |

| 7.2.4 Understanding the S7-200 Timer instruction                  | 43 |

|                                                                   |    |

,

| 9.8 Accessing Data Memory          | 64 |

|------------------------------------|----|

| 9.8.1 Bit Access                   | 64 |

| 9.8.2 Byte word double word access | 64 |

| 9.9 Advantage PLC                  | 64 |

|                                    |    |

| CONCLUSION                         | 65 |

| REFERENCES                         | 66 |

| APENDIX                            | 67 |

| CPU 212 Product Image              | 67 |

| CPU 212 Technical data             | 70 |

# CHAPTER 1 PLC HISTORY

### **11** First Introduced

In the late 1960's PLCs were first introduced. The primary reason for designing such a device was eliminating the large cost involved in replacing the complicated relay based machine control systems. Bedford Associates (Bedford, MA) proposed something called a Modular Digital Controller (MODICON) to a major US car manufacturer. Other companies the time proposed computer based schemes, one of which was based upon the PDP-8. The MODICON 084 brought the world's first PLC into commercial production.

### **1.2** Control System

When production requirements changed so did the control system. This becomes very expensive when the change is frequent. Since relays are mechanical devices they also have a limited lifetime, which required strict adhesion to maintenance schedules.

Troubleshooting was also quite tedious when so many relays are involved. Now picture a machine control panel that included many, possibly hundreds or thousands, of individual relays. The size could be mind-boggling. How about the complicated initial wiring of so many individual devices! These relays would be individually wired together in a manner that would yield the desired outcome.

These "new controllers" also had to be easily programmed by maintenance and plant engineers. The lifetime had to be long and programming changes easily performed. They also had to survive the harsh industrial environment. That's a lot to ask! The answers were to use a programming technique most people were already familiar with and replace mechanical parts with solid-state ones.

### 1.3 Mid70's the dominant PLC technologies

In the mid70's the dominant PLC technologies were sequencer state-machines and the bit-slice based CPU. The AMD 2901 and 2903 were quite popular in Modicon and A-B PLCs. Conventional microprocessors lacked the power to quickly solve PLC logic in all but the smallest PLCs. As conventional microprocessors evolved, larger and larger PLCs were

being based upon them. However, even today some are still based upon the 2903.(ref A-B's FLC-3) Modicon has yet to build a faster PLC than their 984A/B/X which was based upon the 2901.

### **1.4** Communications

Communications abilities began to appear in approximately 1973. The first such system Modicon's Modbus. The PLC could now talk to other PLCs and they could be far away from the actual machine they were controlling. They could also now be used to send and receive varying voltages to allow them to enter the analog world. Unfortunately, the lack of sandardization coupled with continually changing technology has made PLC communications a nightmare of incompatible protocols and physical networks. Still, it was a great decade for the PLC!

The 80's saw an attempt to standardize communications with General Motor's manufacturing automation protocol (MAP). It was also a time for reducing the size of the PLC and making them software programmable through symbolic programming on personal computers instead of dedicated programming terminals or handheld programmers. Today the world's smallest PLC is about the size of a single control relay!

The 90's have seen a gradual reduction in the introduction of new protocols, and the modernization of the physical layers of some of the more popular protocols that survived the 1980's. The latest standard (IEC 1131-3) has tried to merge plc-programming languages under one international standard. We now have PLCs that are programmable in function block diagrams, instruction lists, C and structured text all at the same time! PC's are also being used to replace PLCs in some applications. The original company who commissioned the MODICON 084 has actually switched to a PC based control system.

# **CHAPTER 2**

# **PLC MAINLY CONSISTS**

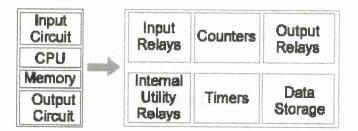

The PLC mainly consists of a CPU, memory areas, and appropriate circuits to receive eput/output data. We can actually consider the PLC to be a box full of hundreds or bousands of separate relays, counters, timers and data storage locations. Do these counters, emers, etc. really exist? No, they don't "physically" exist but rather they are simulated and can be considered software counters, timers, etc. These internal relays are simulated brough bit locations in registers (Figure 2.1)

Figure 2.1 PLC mainly consist

### 2.1 What does each part do?

### 2.1.1 Input Relays (contacts)

These are connected to the outside world. They physically exist and receive signals from switches, sensors, etc. Typically they are not relays but rather they are transistors.

### 2.1.2 Internal Utility Relays (contacts)

These do not receive signals from the outside world nor do they physically exist. They are simulated relays and are what enables a PLC to eliminate external relays. There are also some special relays that are dedicated to performing only one task. Some are always on while some are always off. Some are on only once during power-on and are typically used for initializing data that was stored.

### 2.1.3 Counters

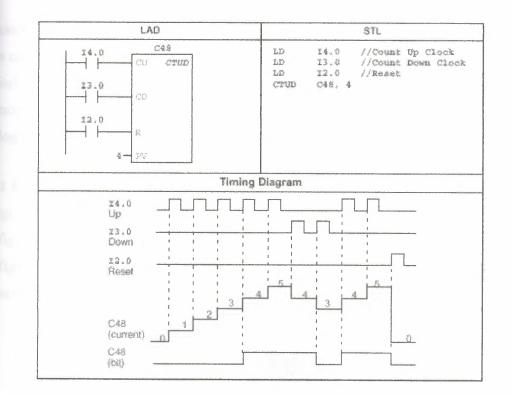

These again do not physically exist. They are simulated counters and they can be programmed to count pulses. Typically these counters can count up, down or both up and

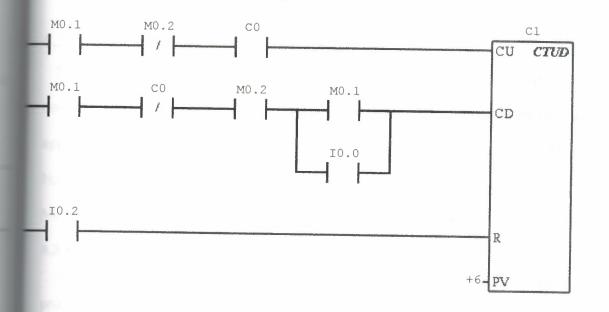

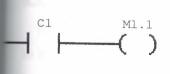

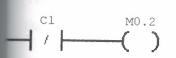

Since they are simulated they are limited in their counting speed. Some confacturers also include high-speed counters that are hardware based. We can think of see as physically existing. Most times these counters can count up, down or up and down. Symbol shows Figure 2.1.1). The Count Up/Down (CTUD) box counts up on rising edges the Count Up (CU) input. It counts down on the rising edges of the Count Down (CD) The Reset (R) input turns on.

Figure 2.1.1

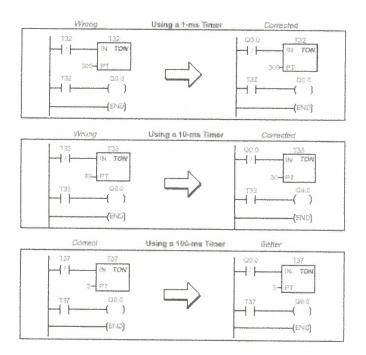

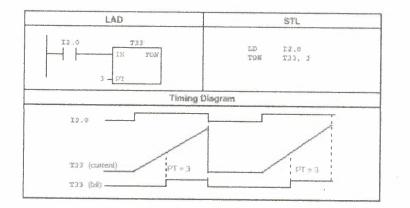

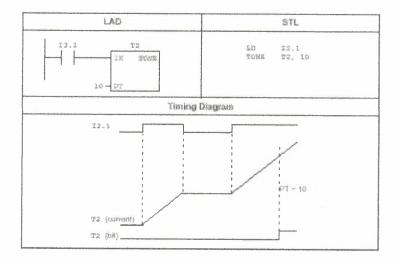

#### **21.4 Timers**

These also do not physically exist. They come in many varieties and increments. The most common type is an on-delay type. Others include off-delay and both retentive and con-retentive types. Increments vary from 1ms through 1s. The On-Delay Timer (TON) box times up to the maximum value when the enabling Input (IN) comes on. When the current value (Txxx) is  $\geq$ = the Preset Time (PT), the timer bit turns on. It resets when the enabling input goes off. Timing stops upon reaching the maximum value.

In the status chart, you can display timer and counter values as either bits or words. If you display a timer or counter value as a bit, the output status is displayed (output on or off). If you display a timer or counter value as a word, the current value is used.

The On-Delay Timers time in one of three resolutions, depending on the timer number you use. Each increment of the current value is a multiple of the time base. For example, a preset of 20 for a 10-millisecond timer represents 200 milliseconds. (Symbol shows in Figure 2.1.2)

### Figure 2.1.2

### **2.1.5 Output Relays (coils)**

These are connected to the outside world. They physically exist and send on/off signals to solenoids, lights, etc. They can be transistors, relays, or triacs depending upon the model chosen.

### **2.1.6 Data Storage**

Typically there are registers assigned to simply store data. They are usually used as temporary storage for math or data manipulation. They can also typically be used to store data when power is removed from the PLC. Upon power-up they will still have the same contents as before power was removed and very convenient and necessary.

# CHAPTER 3 PLC OPERATION

### **31** PLC Scanning

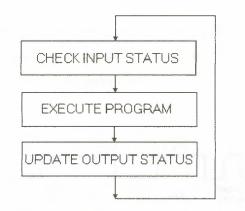

A PLC works by continually scanning a program (Figure 3.1). We can think of this scan consisting of 3 important steps. There are typically more than 3 but we can focus important parts and not worry about the others. Typically the others are checking the stem and updating the current internal counter and timer values.

Figure 3.1 Scanning a program

### **3.1.2 Execute Program (step 2)**

Next the PLC executes your program one instruction at a time. Maybe your program said that if the first input was on then it should turn on the first output. Since it already knows which inputs are on/off from the previous step it will be able to decide whether the first output should be turned on based on the state of the first input. It will store the execution results for use later during the next step.

#### **3.1.3** Update Output Status (step 3)

Finally the PLC updates the status of the outputs. It updates the outputs based on which inputs were on during the first step and the results of executing your program during the second step. Based on the example in step 2 it would now turn on the first output because the first input was on and your program said to turn on the first output when this condition is true.

After the third step the PLC goes back to step one and repeats the steps continuously.

## **3.2** Response Time Concerns

INPUT RESPONSE TIME \_\_\_\_\_\_ = TOTAL RESPONSE TIME \_\_\_\_\_\_ = TOTAL RESPONSE TIME \_\_\_\_\_\_

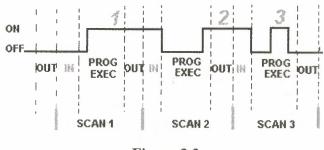

Now that we know about response time, here's what it really means to the application. The PLC can only see an input turn on/off when it's looking. In other words, it only looks at a mputs during the check input status part of the scan.

In the Figure 3.3, input 1 is not seen until scan 2. This is because when input 1 turned on, scan 1 had already finished looking at the inputs.

Input 2 is not seen until scan 3. This is also because when the input turned on scans 2 had already finished looking at the inputs.

Input 3 is never seen. This is because when scan 3 was looking at the inputs, signal 3 was not on yet. It turns off before scan 4 looks at the inputs. Therefore signal 3 is never seen by the PLC.

Figure 3.4

But what if it was not possible for the input to be on this long? Then the PLC doesn't enough turn on. Therefore it becomes a paperweight. Not true, of course there must be to get around this. Actually there are 2 ways.

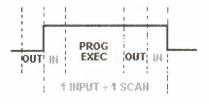

### **321** Pulse Stretch Function

This function extends the length of the input signal until the PLC looks at the inputs (Figure 3.5) during the next scan (i.e. it stretches the duration of the pulse.)

Figure 3.5

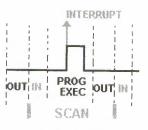

#### **3.2.2** Interrupt Function

This function interrupts the scan to process a special routine that you have written (Figure 16) i.e. As soon as the input turns on, regardless of where the scan currently is, the PLC mediately stops what its doing and executes an interrupt routine. (A routine can be cought of as a mini program outside of the main program.) After its done executing the memory routine, it goes back to the point it left off at and continues on with the normal scan process.

when a switch turns on we need to turn on a load connected to the PLC output.

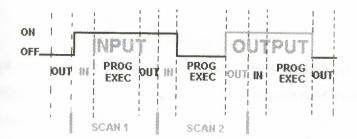

The Figure 3.7 below shows the longest delay (worst case because the input is not seen and scan 2) for the output to turn on after the input has turned on.

The maximum delay is thus 2 scan cycles - 1 input delay time.

# CHAPTER 4 PLC REGISTERS

# **4.1 Ladder Diagram and PLC Registers**

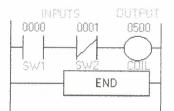

We'll now change switch 2 (SW2) to a normally closed symbol (load bar instruction). SW1 will be physically OFF and SW2 will be physically ON initially. The ladder diagram hows in the Figure 4.1.

Figure 4.1 Ladder diagram

Notice also that we now gave each symbol (or instruction) an address. This address sets uside a certain storage area in the PLCs data files so that the status of the instruction (i.e. rue/false) can be stored. Many PLCs use 16 slot or bit storage locations. In the example shove (Table 4.1) we are using two different storage locations or registers.

Table 4.1 Two different storage locations or registers

| -        |           |                |              |                                         |              | RE | EGIS | TER | 00 | en als here to be lega | idholithaichthanaid | indensfelenstenstens | Appendic for Street Sophie de | un controllan de Lan | ال والبات منها عالمت |

|----------|-----------|----------------|--------------|-----------------------------------------|--------------|----|------|-----|----|------------------------|---------------------|----------------------|-------------------------------|----------------------|----------------------|

| 15       | 14        | 13             | 12           | 11                                      | 10           | 09 | 08   | 07  | 06 | 05                     | 04                  | 03                   | 02                            | 01                   | 00                   |

|          |           | and the second |              |                                         |              |    |      |     |    |                        |                     |                      | Seldent-Jeakilout-Je          | 1                    | 0                    |

|          | Suman     | 3              | 1. commences | and | A            | A  | 1    | 1   | 1  |                        |                     | 5                    | 1                             |                      |                      |

| in Since | ânatanata | in the set     | 1            | i<br>distriction:                       | Ant EstimEtt | RE | EGIS |     |    |                        | concidend           |                      | )<br>176-2304-030             |                      |                      |

| 15       | 14        | 13             | 12           | 11                                      | 10           |    |      |     |    | 05                     | 04                  | 03                   | 02                            | 01                   | 00                   |

In the table 4.2 above we can see that in register 00, bit 00 (i.e. input 0000) was logic 0 and bit 01 (i.e. input 0001) was logic 1. Register 05 shows that bit 00 (i.e. output 0500) was logic 0. The logic 0 or 1 indicates whether an instruction is False or True.

### Table 4.2 The register

| LOGICAL    | CONDITION OF | SYMBOL | na Manana di kana dalama atalana dalama |

|------------|--------------|--------|-----------------------------------------|

| LOGIC BITS | LD           | LDB    | OUT                                     |

| Logic 0    | False        | True   | False                                   |

| Logic 1    | True         | False  | True                                    |

The PLC will only energize an output when all conditions on the rung are TRUE. So, tooking at the table above, we see that in the previous example SW1 has to be logic 1 and SW2 must be logic 0. Then and only then will the coil be true (i.e. energized). If any of the estructions on the rung before the output (coil) are false then the output (coil) will be false (not energized).

In LAD programs, the basic elements of logic are represented with contacts, coils, and boxes. A set of interconnected elements that make a complete circuit is called a network.

A hard-wired input is represented by a symbol called a contact. A normally open contact enables power flow when closed. A contact can also be normally closed. In this case, power fow occurs when the contact is opened.

# **4.2 Truth Table**

Let's now look at a truth table 4.3 of our previous program to further illustrate this mortant point. Our truth table will show all possible combinations of the status of the two mputs.

| Inputs  |          | Outputs   |         | Register Logic Bits                                                                                            |           |  |

|---------|----------|-----------|---------|----------------------------------------------------------------------------------------------------------------|-----------|--|

| SW1(LD) | SW2(LDB) | COIL(OUT) | SW1(LD) | SW2(LDB)                                                                                                       | COIL(OUT) |  |

| False   | True     | False     | 0       | 0                                                                                                              | 0         |  |

| False   | False    | False     | 0       | teleberteleberende versionliche auf ihre auf ihre en die seine der seinen der seinen der seinen der seinen der | 0         |  |

| True    | True     | True      | 1       | 0                                                                                                              | 1         |  |

| True    | False    | False     | 1       | 1                                                                                                              | 0         |  |

| Table 4.3 | Truth | Table |

|-----------|-------|-------|

|-----------|-------|-------|

Notice from the chart that as the inputs change their states over time, so will the outputs. The output is only true (energized) when all preceding instructions on the rung are true.

### **4.3** The Program Scan

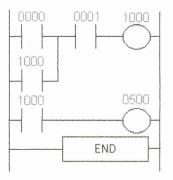

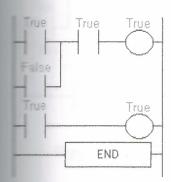

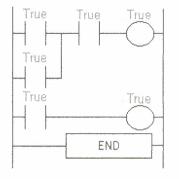

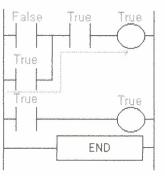

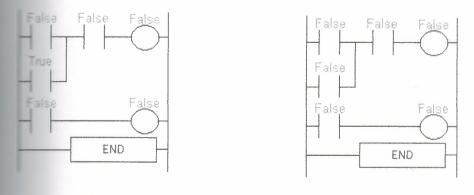

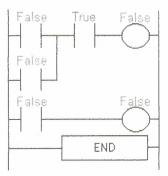

Let's watch what happens in this program scan by scan with Figure 4.2, Figure 4.3, Figure 4.4 and Figure 4.5.

## Figure 4.2

Initially the tank is empty. Therefore, input 0000 is TRUE and input 0001 is also TRUE.

Figure 4.3

Figure 4.4

After 100 scans the oil level rises above the low level sensor and it becomes open. **FALSE**)

Figure 4.5

Notice that even when the low level sensor is false there is still a path of true logic from to right. This is why we used an internal relay. Relay 1000 is latching the output (500) It will stay this way until there is no true logic path from left to right.(i.e. when 0001 becomes false) After 1000 scans the oil level rises above the high level sensor at it also becomes open (i.e. false) (Figure 4.6 and Figure 4.7)

Figure 4.6

Figure 4.7

Since there is no more true logic path, output 500 is no longer energized (true) and therefore the motor turns off.

After 1050 scans the oil level falls below the high level sensor and it will become true (Figure 4.8)

.

# CHAPTER 5 CPU 212

## **5.1 Overview**

- Low-cost entry into the SIMATIC S7-21x Series

- All round talent with a wide spectrum of connectable expansion modules

- With analog value processing

# 5.2 Area of application

The CPU 212 is the low-cost entry into the SIMATIC S7-200 family. A wide range of connectable expansion modules not only opens up the world of analog value processing but uso makes the CPU a real all round talent.

# **5.3 Design**

Figure 5.1

CPU 212 (Figure 5.1) features:

Integrated 24 V transmitter and load power supply;

for direct connection of sensors and transmitters. With its 180mA output current it can also be used to supply loads.

7 variants;

with different supply voltages and control voltages.

- Integrated digital inputs and outputs;

8 inputs and 6 outputs.

- Interrupt inputs;

for extremely rapid response to rising or falling edges of process signals.

- High-speed counter;

- 1 high-speed counter (2 kHz), for implementation as an up or down counter.

- Problem-free expansion with digital and analog expansion modules (EM, optional).

- Simulator (optional);

for simulating the integrated inputs and testing the user program.

- Analog potentiometer;

- 1 analog potentiometer, easy-to-use in everyday operation as a set point adjuster, e.g. for setting timers.

### **5.4 Functions**

- Comprehensive instruction set;

- numerous basic operations such as binary logic operations, result assignment, storing, counting, setting up timers, loading, transferring, comparing, shifting, rotating, generating complements, calling subroutines, integrated communication instructions (e.g. RECEIVE Freeport) and user-friendly functions such as pulsewidth modulation, pulse sequence function, arithmetic functions, jump functions, loop functions and code conversions aid programming.

- Counting;

user-friendly counter functions in conjunction with the integrated counters open up new applications for the user.

- Interrupt handling;

- Edge-triggered interrupts (activated by rising or falling edges of process signals on interrupt inputs) support a rapid response to process events.

- Timed interrupts can be set from 5 ms to 255 ms at intervals of 1 ms.

- Counter interrupts can be triggered when a set point is reached or when the direction of counting changes.

- Communication interrupts support the fast and easy exchange of information with I/O devices, e.g. printers or barcode readers.

- Direct scanning and control of inputs and outputs;

inputs and outputs can also be directly scanned and set independently of the cycle.

The controller is then able to respond quickly to process events (e.g. direct resetting of outputs on the occurrence of an interrupt).

- Password protection;

the three-level password protection concept provides effective protection for company expertise. The protection concept features the following modes of access to the user program:

- Complete access: The program can be changed as required.

- Read-only: The program is protected against unauthorized modification. Testing, setting system parameters and copying the program are all possible.

- Complete protection: The program is protected against modifications and unauthorized reading and copying. Parameters can be set.

- Test and diagnosis functions;

user-friendly functions support test and diagnosis: The complete program is executed over a number of cycles that can be specified and analyzed. Internal parameters, such as bit-memories, timers or counters are logged over up to 124 cycles.

"Forcing" of inputs and outputs in test and diagnosis mode;

inputs and outputs can be set independent of the cycle and therefore permanently,

for the purpose of testing the user program for example.

# 5.5 Programming

The program packages STEP 7-Micro/DOS V1.3, STEP 7-Micro/WIN16 V2.6 or STEP 7-Micro/WIN32 V3.0 are available for programming the CPU 212.

Every function of the CPU can be programmed using these packages. If programming is performed via the serial interface of the programming device or PC, a PC/PPI cable will **150** be necessary.

If the programming software STEP 7-Micro/WIN32 V3.0 is used, it is also possible to program the CPU via the SIMATIC CPs CP 5511 or CP 5611. In this manner, communication rates of up to 187 kbit/s are possible.

# CHAPTER 6 S7-200 MICRO PLC

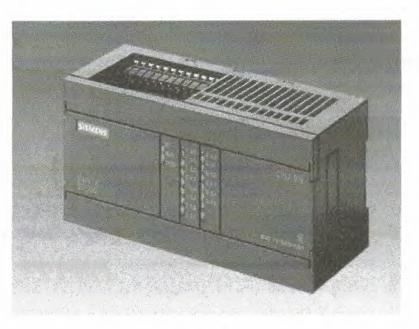

# 6.1 Introducing the S7-200 Micro PLC

The S7-200 series is a line of micro-programmable logic controllers (Micro PLCs) that can control a variety of automation applications. Figure 6-1 shows an S7-200 Micro PLC. The compact design, expandability, low cost, and powerful instruction set of the S7-200 Micro PLC make a perfect solution for controlling small applications. In addition, the wide variety of CPU sizes and voltages provides you with the flexibility you need to solve your utomation problems.

Figure 6.1 S7-200 Micro PLC

# 6.2 Comparing the Features of the S7-200 Micro PLCs

# **6.2.1 Equipment Requirements**

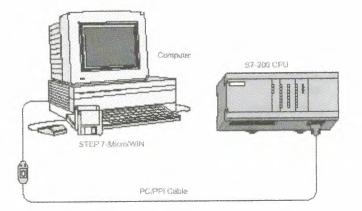

Figure 6.2 shows the basic S7-200 Micro PLC system, which includes an S7-200 CPU module, a personal computer, STEP 7-Micro/WIN programming software, and a communications cable. In order to use a personal computer (PC), you must have one of the following sets of equipment:

- A PC/PPI cable

- A communications processor (CP) card and multipoint interface (MPI) cable

- A multipoint interface (MPI) card. A communications cable is provided with the MPI card.

Figure 6.2 The basic S7-200 Micro PLC system

## Capabilities of the S7-200 CPUs

The S7-200 family includes a wide variety of CPUs. This variety provides a range of **CENTRES** to aid in designing a cost-effective automation solution. Table 6.1 provides a **CENTRES** of the major features of each S7-200 CPU.

| Features                 | CPU 212                 | CPU 214                 | CPU 215                 | CPU 216                 |

|--------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| Second Size of Unit      | 160 mm x 80 mm<br>×62mm | 197 mm x 80 mm<br>×62mm | 218 mm x 80 mm<br>×62mm | 218 mm x 80 mm<br>×62mm |

| Memory                   |                         |                         |                         |                         |

| EEPROM)                  | 512 words               | 2kwords                 | 4kwords                 | 4kwords                 |

| liser data               | 512 words               | 2kwords                 | 2.5kwords               | 2.5kwords               |

| memal memory bits        | 128                     | 256                     | 256                     | 256                     |

| lemony cartridge         | none                    | Yes(EEPROM)             | Yes(EEPROM)             | Yes(EEPROM)             |

| boonal battery cartridge | none                    | 200 days typical        | 200 days typical        | 200 days typical        |

| Sector upper capac       | 50 hours typical        | 190 hours typical       | 190 hours typical       | 190 hours typica        |

| mouts/Outputs (I/O)      |                         |                         |                         |                         |

| local I/O                | 8 DI/6 DQ               | 14 DI/10 DQ             | 14 DI/10 DQ             | 24 DI/16 DQ             |

| mansion modules (max.)   | 2 modules               | 7 modules               | 7 modules               | 7 modules               |

| -image I/O               | 64 DI/64 DQ             | 64 DI/64 DQ             | 64 DI/64 DQ             | 64 DI/64 DQ             |

| landog I/O (expansion)   | 16 AL/16 AQ             | 16 AL/16 AQ             | 16 AL/16 AQ             | 16 AL/16 AQ             |

| Selectable input filters | No                      | yes                     | yes                     | yes                     |

| Instructions             |                         |                         |                         |                         |

| Sociean execuation speed | 1.2µs/instruction       | 0.8µs/instruction       | 0.8µs/instruction       | 0.8µs/instruction       |

| Counters/timers          | 64/64                   | 128/128                 | 256/256                 | 256/256                 |

| For next loops           | No                      | Yes                     | Yes                     | Yes                     |

| more math                | Yes                     | Yes                     | Yes                     | Yes                     |

| math                     | No                      | Yes                     | Yes                     | Yes                     |

| PD                       | No                      | No                      | Yes                     | Yes                     |

Table 6.1 Provides a summary of the major features of each S7-200 CPU.

| subditional Features           |                          |                          |                             |                                       |

|--------------------------------|--------------------------|--------------------------|-----------------------------|---------------------------------------|

| speed counter                  | 1 S/W                    | 1 S/W, 2H/W              | 1 S/W, 2H/W                 | 1 S/W, 2H/W                           |

| and og adjustments             | 1                        | 2                        | 2                           | 2                                     |

| outputs                        | None                     | 2                        | 2                           | 2                                     |

| Communication interrupt evants | 1 transmit/<br>1 reciver | 1 transmit/<br>1 reciver | 1 transmit/<br>2reciver     | 2 transmit/<br>4reciver               |

| Final interrupts               | 1                        | 2                        | 2                           | 2                                     |

| are input interrupts           | 1                        | 4                        | 4                           | 4                                     |

| and time clock                 | None                     | Yes                      | Yes                         | Yes                                   |

| Communications                 |                          |                          |                             |                                       |

| ber of common ports            | 1 (RS-485)               | 1 (RS-485)               | 2 (RS-485)                  | 2 (RS-485)                            |

| Port 0:<br>Port 1:             | PPI, Freeport<br>N/A     | PPI, Freeport<br>N/A     | PPI, Freeport, MP<br>DP,MPI | · · · · · · · · · · · · · · · · · · · |

| her to peer                    | Slave only               | Yes                      | Yes                         | Yes                                   |

# Major Components of the S7-200 Micro PLC

An S7-200 Micro PLC consists of an S7-200 CPU module alone or with a variety of actional expansion modules.

### 1 S7-200 CPU Module

The S7-200 CPU module combines a central processing unit (CPU), power supply, and Escrete I/O points into a compact, stand-alone device.

- The CPU executes the program and stores the data for controlling the automation task or process.

- The power supply provides electrical power for the base unit and for any expansion module that is connected.

- The inputs and outputs are the system control points: the inputs monitor the signals from the field devices (such as sensors and switches), and the outputs control pumps, motors, or other devices in your process.

- The communications port allows you to connect the CPU to a programming device or to other devices. Some S7-200 CPUs have two communications ports.

- Status lights provide visual information about the CPU mode (RUN or STOP), the current state of the local I/O, and whether a system fault has been detected.

### **5.4 Installing and Using the STEP 7-Micro/WIN Software**

STEP 7-Micro/WIN is a Windows-based software application that supports both the 16-Windows 3.1 environment (STEP 7-Micro/WIN 16) and the 32-bit Windows 95 and endows NT environments (STEP 7-Micro/WIN 32). In order to use STEP 7-Micro/WIN, following equipment is recommended:

- Recommended: a personal computer (PC) with an 80586 or greater processor and 16 Mbytes of RAM, or a Siemens programming device (such as a PG 740); minimum computer requirement: 80486 processor with 8 Mbytes

- One of the following sets of equipment:

- A PC/PPI cable connected to your communications port (PC COM1 or COM2)

- A communications processor (CP) card and multipoint interface (MPI) cable

- A multipoint interface (MPI) card (A communications cable comes with the MPI card.)

- VGA monitor, or any monitor supported by Microsoft Windows

- At least 50 Mbytes of free hard disk space

- Microsoft Windows 3.1, Windows for Workgroups 3.11, Windows 95, or Windows NT 4.0 or greater

- Optional but recommended: any mouse supported by Microsoft Windows STEP 7-Micro/WIN provides extensive online help. Use the Help menu command or press F1 to obtain the most current information.

## **5.5 Installing the STEP 7-Micro/WIN Software**

### **5.1 Pre-Installation Instructions**

Before running the setup procedure, do the following:

- If a previous version of STEP 7-Micro/WIN is installed, back up all STEP 7-Micro/WIN projects to diskette.

- Make sure all applications are closed, including the Microsoft Office toolbar. Installation may require that you restart your computer.

### **152** Installation Instructions for Windows 3.1

you have Windows 3.1 (Windows for Workgroups 3.11) on your machine, use the ming procedure to install the STEP 7-Micro/WIN 16 software:

Start by inserting Disk 1 in the disk drive of your computer (usually drive A or drive B).

From the Program Manager, select the menu command File-Run...

The Run dialog box, type a:\setup and click "OK" or press ENTER. This starts the procedure.

- Follow the online setup procedure to complete the installation.

### **15.3** Installation Instructions for Windows 95 or Windows NT 4.0

If you have Windows 95 or Windows NT 4.0 on your machine, use the following mededure to install the STEP 7-Micro/WIN 32 software:

Start by inserting Disk 1 in the disk drive of your computer (usually drive A or drive B).

Click once on the "Start" button to open the Windows 95 menu.

Click on the Run... menu item.

The Run dialog box, type a:\setup and click on "OK" or press ENTER. This starts the procedure.

Follow the online setup procedure to complete the installation.

At the end of the installation, the Install/Remove Modules dialog box appears communically. See Figure 6.3. You can install the hardware for your machine to communicate now, or you can wait until later.

| Seladión:                                                                                                   |         | Irustanile <u>ed</u>     |                                                                           |

|-------------------------------------------------------------------------------------------------------------|---------|--------------------------|---------------------------------------------------------------------------|

| CPUE44<br>CPU5611 (Plug & Plug)<br>CPU5611 (Plug & Plug)<br>MPI-ISA (a) board<br>PC Adigater (PCI&PF-Cadde) | and sec | MPESA Cart<br>PCPM cable |                                                                           |

|                                                                                                             |         | Résources.               | This button appear<br>3 you are using a<br>Windows NY<br>operating system |

Figure 6.3 Install/Remove Modules Dialog Box

### **4 Troubleshooting the Installation**

The following situations can cause the installation to fail:

- Not enough memory: at least 50 Mbytes of free space are required on your hard disk.

- Bad diskette: verify that the diskette is bad, then call your salesman or distributor.

- Operator error: start over and read the instructions carefully.

• Failure to close any open applications, including the Microsoft Office toolbar eview the README x.TXT file included on your diskettes for the most recent comation about STEP 7-Micro/WIN. (In the x position, the letter A = German, B = clish, C = French, D = Spanish, E = Italian.)

### **5.6 Using STEP 7-Micro/WIN to Set Up the Communications Hardware**

**66.1** General Information for Installing or Removing the Communications Hardware

by you are using Windows 95 or Windows NT 4.0, the Install/Remove Modules dialog box appears automatically at the end of your software installation. See Figure 6.3. If you re using Windows 3.1, follow these steps:

Select the menu command Setup-Communications. The Communications dialog box

Click the "PG/PC Interface..." button. The Setting the PG/PC Interface dialog box

Click the "Install..." button. The Install/Remove Modules dialog box appears. See Figure

Teu will need to base your installation of communications hardware on the following

- The operating system that you are using (Windows 3.1, Windows 95, or Windows NT 4.0)

- The type of hardware you are using, for example:

- PC with PC/PPI cable

- PC or SIMATIC programming device with multipoint interface (MPI) or communications processor (CP) card.

- CPU 212, CPU 214, CPU 215, CPU 216

- Modem

- The baud rate you are using

Table 6.2 shows the possible hardware configurations and baud rates that STEP 7-WIN support, depending on the type of CPU that you are using.

Table 6.2 Hardware Configurations Supported by STEP 7- Micro/WIN

| Type of CFU                 | STEP 7-Micros<br>WIN Versizm | Hardware Supported                                                                    | Baust Rates<br>Supported   | Operating<br>System                         | Type of<br>Parameter Set |

|-----------------------------|------------------------------|---------------------------------------------------------------------------------------|----------------------------|---------------------------------------------|--------------------------|

| CPU 212,<br>CPU 214,        | Micro/WIN 16                 | PC/PPI cable, MPI-ISA<br>cand                                                         | 9.6 khaud or<br>19.2 khaud | Windows 3.1                                 | PPI.<br>PPI uniki-mastar |

| CPU 215<br>CPU 215 port 0   |                              |                                                                                       |                            | Windows 95 or<br>Windows NT                 | PPI                      |

|                             | MicneWIN 32                  | PC/PPI cable, MPI-ISA<br>card, MPI-ISA card on<br>bound, CP 5411,<br>CP 5514, CP 5611 | 9.6 kband or<br>19:2 kband | Wandows 95 or<br>Windows NT                 | FFI.<br>FFI unde-master  |

| CPU 215 port 1<br>(DP port) | Micna/WIN 16                 | Not supported                                                                         | Not supported              | Windows 3, 1<br>Windows 95 or<br>Windows NT | Not supported            |

|                             | Micro/WIN 32                 | MPI-ISA card,<br>MPI-ISA card en<br>board, CP 5411,<br>CP 5511, CP 5614               | 9.6 khand in<br>12 Mbatid  | Windows 95 or<br>Windows NT                 | MPI                      |

## Some Special Hardware Installation Information for Windows NT Users

Installing hardware modules under the Windows NT operating system is slightly erent from installing hardware modules under Windows 95. Although the hardware dules are the same for either operating system, installation under Windows NT requires e knowledge of the hardware that you want to install. Windows 95 tries automatically et up system resources for you; however, Windows NT does not. Windows NT provides with default values only. These values may or may not match the hardware figuration.

However, these parameters can be modified easily to match the required system settings.

When you have installed a piece of hardware, select it from the Installed list box and each the "Resources" button. The Resources dialog box appears. See Figure 6.4. The sources dialog box allows you to modify the system settings for the actual piece of dware that you installed. If this button is unavailable (gray), you do not need to do eaching more.

At this point you may need to refer to your hardware manual to determine the setting for

and of the parameters listed in the dialog box, depending on your hardware settings. You need to try several different interrupts in order to establish communication correctly.

| <u>14</u>   | enicey Ranges.                                                     | #600000 | 00-000CC/FF | 1.00 | <u></u> |

|-------------|--------------------------------------------------------------------|---------|-------------|------|---------|

| <u>1</u> 23 | statCutput Ranges                                                  | ſ       |             |      |         |

| W           | ebenuph <u>Receptent</u> i                                         | #15     | E           |      |         |

| D           | tect Memory Accessic                                               | [       | I           |      |         |

|             | Current hardwate setting<br>Possible cutoffici with other hardware |         |             |      |         |

Figure 6.4 Resources Dialog Box for Windows NT

### **Establishing Communication with the S7-200 CPU**

can arrange the S7-200 CPUs in a variety of configurations to support network munications. You can install the STEP 7-Micro/WIN software on a personal computer that has a Windows 3.1x, Windows 95, or Windows NT operating system, or you can it on a SIMATIC programming device (such as a PG 740). You can use the PC or programming device as a master device in any of the following communications gurations:

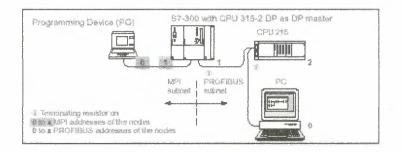

- A single master device is connected to one or more slave devices. See Figure 6.5.

- A single master device is connected to one or more slave devices and one or more master devices. See Figure 6.6 and Figure 6.7.

- A CPU 215 functions as a remote I/O module owned by an S7-300 or S7-400 programmable logic controller or by another PROFIBUS master. See Figure 6.8.

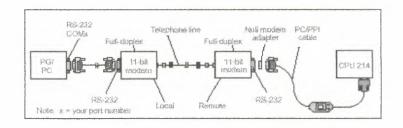

- A single master device is connected to one or more slave devices. This master device is connected by means of 11-bit modems to either one S7-200 CPU functioning as a slave device or else to a network of S7-200 CPUs functioning as slave devices. See Figure 6.9.

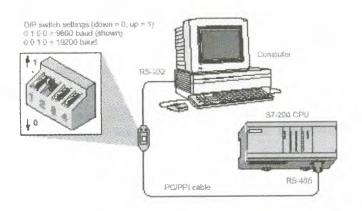

**EX.1** Connecting Your Computer to the S7-200 CPU Using the PC/PPI Cable

Figure 6.5 shows a typical configuration for connecting your personal computer to your

with the PC/PPI cable. To establish proper communications between the components, these steps:

Set the DIP switches on the PC/PPI cable for the baud rate.

Connect the RS-232 end of the PC/PPI cable labeled PC to the communications port of computer, either COM1 or COM2, and tighten the connecting screws.

Connect the other end (RS-485) of the PC/PPI cable to the communications port of the connecting screws.

Figure 6.5 Communicating with a CPU in PPI Mode

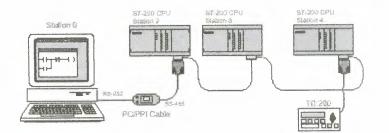

Figure 6.6 shows a configuration with a personal computer connected to several S7-CPU modules. STEP 7-Micro/WIN is designed to communicate with one S7-200 CPU time; however, you can access any CPU on the network. The CPU modules in Figure could be either slave or master devices. The TD 200 is a master device.

Figure 6.6 Using a PC/PPI Cable for Communicating with Several S7-200 CPU Modules 6.8.2 Connecting Your Computer to the S7-200 CPU Using the MPI or CP Card You can use STEP 7-Micro/WIN with a multipoint interface (MPI) or communications essor (CP) card. Either card provides a single RS-485 port for connection to the ork using an MPI cable. STEP 7 Micro/WIN 32 (the 32-bit version) supports the MPI meter set for an MPI network; STEP 7-Micro/WIN 16 (the 16-bit version) does not.

establishing MPI communications, you can connect STEP 7-Micro/WIN on a ork that contains other master devices. Each master must have a unique address.

Each 7 shows a sample network with master and slave devices.

Figure 6.7 Example of an MPI or CP Card with Master and Slave Devices

Figure 6.8 CPU 215 on a PROFIBUS Subnetwork, with MPI Subnetwork

Figure 6.9 S7-200 Data Communications Using an 11-Bit Modem

#### **EXAMPLE From What Point Do I Set Up Communications?**

The pending on the operating system that you are using, you can set up communications of the following points:

Under Windows 3.1

Within STEP 7-Micro/WIN 16 only

- Under Windows 95 or Windows NT 4.0

- During the final step of the installation (see Section 3.1)

- From the Setting the PG/PC Interface icon, found in the Windows Control Panel

- Within STEP 7-Micro/WIN 32

#### Setting Up Communications within STEP 7-Micro/WIN

gure your communications setup. See Figure 6.10. You can use one of the following to find this dialog box:

- Select the menu command Setup-Communications....

- Create a new project and click the "Communications..." button in the CPU Type dialog box.

- If you have a project open, select the menu command CPU-Type... and click the "Communications" button in the CPU Type dialog box.

| Statigents Faculty of the       |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current Communication Sellings  |                 | ProPG Interfac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Madale Parameter   PC/PP) cable |                 | Modern Selup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Local Station Ad                | himbererentered | president and a second and as second and a |

| Terrenission                    | Rate 8.6 ktor   | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| O G M                           | 1-2-2-51 A      | Mar .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Ramote Station Address          | 2               | • Jest Satap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Figure 6.10 Setting Up the Communications between Programming Device or PC and the

After you have called up the Communications dialog box, click the "PG/PC Interface" auton. The Setting the PG/PC Interface dialog box appears. See Figure 6.11.

| 5 STEP 7-Micron | the second states and the se |                  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Broject View S  | Serie of the RG/PC internace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ×                |

| DCD B           | Access Palls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |

|                 | Anceres Porst of Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                |

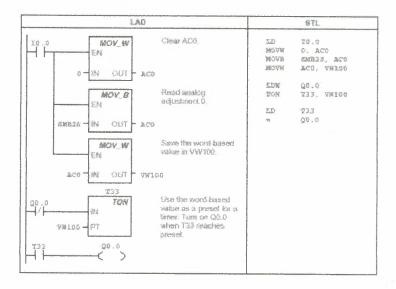

|                 | Ministeries<br>(Skatelineski for MinisterWillig)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |