# NEAR EAST UNIVERSITY

# Faculty of Engineering

# Department of Electrical and Electronic Engineering

# AIR CONDITION CONTROL OF AKM (PLC)

Graduation Project EE - 400

Student: Murat Muhammet GÜVEN(92063)

Supervisor:

# Özgür C. ÖZERDEM

Lefkoşa - 2001

LIBRARY LIBRARY

| CONTENTS                                             |        |

|------------------------------------------------------|--------|

| ACKNOWLEDGEMENT                                      | i      |

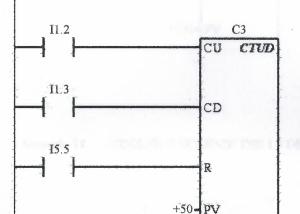

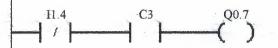

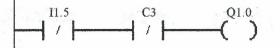

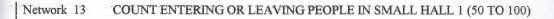

| ABSTRACT                                             | ii     |

| INTRODUCTION                                         | iii    |

| 1.WHAT IS A PLC?                                     | 1      |

| 2.PLC HISTORY                                        | 2      |

| 3.GENERAL PHYSICAL BUILD MECHANISM                   | 3      |

| 3.1 Compact PLC's                                    | 3      |

| 3.2 ModularPLC's                                     | 3      |

| 3.3 Basic Instruction                                | 4      |

| a) LOD Instruction                                   | 4      |

| b) Input, Output Internal and Special Relays         | 4      |

| c) Timer                                             | 5<br>5 |

| d) Counter                                           |        |

| e) shift Register                                    | 5<br>5 |

| f) AND Instruction                                   |        |

| g) OR Instruction                                    | 5      |

| h) NOT Instructions                                  | 6      |

| 4.ADVANTAGE                                          | 6      |

| 4.1 Accuracy                                         | 6      |

| 4.2 Flexibility                                      | 7      |

| 4.3 Control of Industrial Automation                 | 7      |

| 4.4 Data Areas                                       | 7      |

| 4.5 Data Object                                      | 8      |

| 5. LADDER AND STL PROGRAM                            | 9      |

| 6. MEMORY DESIGN                                     | 11     |

| 6.1 Prom                                             | 11     |

| 6.2 EProm                                            | 11     |

| 6.3 EAProm                                           | 11     |

| 6.4 EE Prom                                          | 12     |

| 6.5 Programming Devices                              | 12     |

| 6.6 Basic instruction word                           | 14     |

| 6.7 FA1J Series allocation numbers of special relays | 17     |

| 7.TYPES OF PLC                                       | 18     |

| 7.1 Small PLC's                                      | 19     |

| 7.2 Medium – Sized PLC's                             | 20     |

| 7.3 Large PLC                                        | 21     |

| 7.4 Remote Input / Output                            | 22     |

| 7.5 Programming Large PLC's                          | 22     |

| 7.6 Developments                                     | 23     |

| 8. PROGRAMMING OF PLC SYSTEMS                                             | 23       |

|---------------------------------------------------------------------------|----------|

| 8.1 Logic Instruction Sets and Graphic Programming                        | 24       |

| 8.1-1Input / Output Numbering                                             | 26       |

| 8.1-2 Negation – NAND and NOR Gates                                       | 26       |

| 8 1-3 Exclusive – OR Gate                                                 | 27       |

| 8.2 Facilities                                                            | 27       |

| 8.2-1 Standard PLC Functions                                              | 27       |

| 8.2-2 Markers / Auxiliary Relays                                          | 30       |

| 8.2-3 Ghost Contacts                                                      | 30       |

| 8.2-4 Retentive Battery – Backed Relays                                   | 30       |

| 8.2-5 Optional Functions on Auxiliary Relays                              | 31       |

| 8.2-6 Pulse Operation                                                     | 32       |

| 8.2-7 Set and Reset                                                       | 34       |

|                                                                           | 41       |

| 8.3-2 Magnitude Comparison<br>8.3-3 Addition and Subtraction Instructions | 41       |

|                                                                           | 42       |

| 9. LADDER PROGRAM DEVELOPMENT                                             | 42       |

| 9.1 Software Design                                                       | 42       |

| 9.2 Program Structure                                                     |          |

| 9.3 Further Sequential Control Techniques                                 | 47<br>48 |

| 9.4 Limitation of Ladder Programming                                      | 48       |

| 9.4-1 Advanced Graphic Programming Languages                              | 48       |

| 9.4-2 Workstations                                                        | 49       |

| <b>10. CHOOSING , INSTALLATION AND</b>                                    |          |

| COMMISSIONING OF PLC SYSTEMS                                              | 49       |

| 10.1 Feasibility Study                                                    | 49       |

| 10.2 Design Procedure for PLC Systems                                     | 50       |

| 10.2-1 Choosing a Programmable Controller                                 | 51       |

| 10.2-2 Size and Type of PLC System                                        | 51       |

| 10.2-3 I / O Requirements                                                 | 52       |

| 10.2-4 Memory and Programming Requirements                                | 52       |

| 10.2-5 Instruction Set / CPU                                              | 54       |

| 10.3 Installation                                                         | 55       |

| 10.4 Testing and Commissioning                                            | 57       |

| 10.4-1 Software Testing and Simulation                                    | 58       |

| 10.4-2 Installing and Running the User Control Program                    | 61       |

| 11.Table of symbol                                                        | 63       |

| <b>12. DESCRIPTION OF OPERATION</b>                                       |          |

| 13. CONCLUSION                                                            |          |

|                                                                           |          |

| 14. REFERENCES                                                            |          |

| 15 APPENDIX                                                               |          |

1

6. 6.1

6.5

6.7 7.**T** 7.11 7.21 7.21 7.21 7.21 7.21 7.51

# **INTRODUCTION**

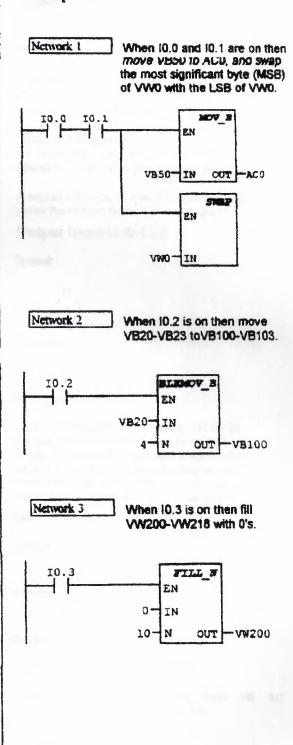

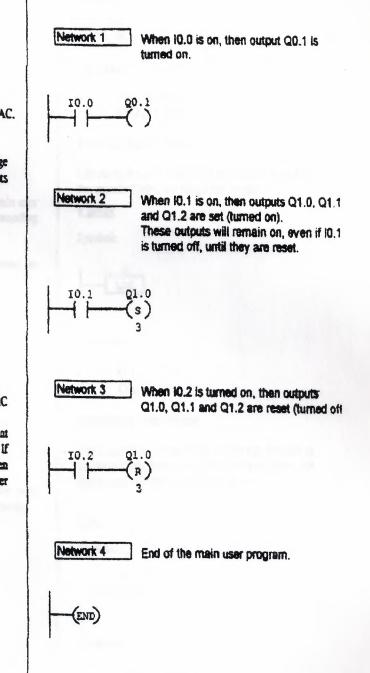

Now that understand how inputs and outputs are processed by the PLC, let's look at a variation of our regular outputs. Regular output coils are of course an essential part of our programs but we must remember that they are only true when all instructions before them on the rung are also true.

Think back to the we did a few chapters ago. What would' ve happened if we couldn't find a "push on / push off" switch? Then we would' ve had to keep pressing to button for as long as we wanted the bell to sound. The latching instructions let us use momentary switches and program the PLC so that when we push one the output turns on and when we push another the output turns off.

Picture the remote control for your TV. It has a button for on hand another for off. When I push the on button TV turns on. When I push the off button the TV turns off. I don't have to keep pushing the on button to keep the TV on. This would be the function of a latching instruction.

The latch instruction is often called a SET or OTL (output latch). The unlatch instruction is often called a RES (reset), OUT (output latch) or RST (reset). The diagram below shows how to use them in a program.

# ABSTRACT

My project is generally is about PLC information's. But my project can be separate into two part.

In the first part SIEMENS SIMATIC S7 PLC information's and sample program is given. At the same time in this part has SIMATIC S7 PLC generally information and instructions and history, is give In the second part MITSUBISHI FC-40 FC-20 PLC's general is given.

And the last part is about the project and the program that wrote and implemented a bout automation of air conditioner of AKM.

# ACKNOWLEDGEMENT

I am deeply indepted to my parents for their love and financial support. They have always encouraged me to pursue my interests and ambitions throughout life.

To my supervisor Mr. Özgür C. ÖZERDEM who was helped me to finish and realize this difficult task, my deep gratitudes and thanks.

Also thanks to Prof. Dr. Haldun GÜRMEN, Prof. Dr. Fakhreddin MAMEDOV, Prof. Dr. Şenol BEKTAŞ Prof. Dr. Khalil ISMAILOV assist Prof. Kadri BÜRÜNCÜK and assist Prof. Kamil DİMİLLER

i

Mr. Kaan UYAR and to all of my other teachers for their advices.

## **1.WHAT IS A PLC ?**

A programmable logic controller (PLC) is a device that was invented to replace the necessary sequential relay circuits for machine control. The PLC works by looking at its inputs and depending upon their state, turning on / off its outputs. The user enters a program, usually via software, that gives the desired results.

PLC's are used in many real word applications. If there is industry present, chances are good that there is a PLC present. If you are involved in machining, packaging, material handling, automated assembly or countless other industries you are probably already using them. If you are not, you are wasting money and time. Almost any application that needs some type of electrical control has a need for a PLC.

For example, let's assume that when a switch turns on we want turn a solenoid on for 5 seconds and then turn it off regardless of how long the switch is on for. We can do this with a simple external timer. But what if the process included 10 switches and solenoids? We would need 10 external timers. What if the process also needed to count how many times the switches individually turned on? We need a lot of external counters.

As you can see the bigger the process the more of a need we have for a PLC. We can simply program the PLC to count its inputs and turn the solenoids on for the specified time.

This site gives you enough information to be able to write programs far more complicated than the simple one above. We will take a look at what is considered to be the ' top 20' PLC instructions. It can be safely estimated that with a firm understanding of these instructions one can solve more than 80 % of the applications inexistence.

1

# 2.PLC HISTORY

In the late 1960' s PLC' s were first introduced. The primary reason for designing such a device was eliminating the large cost involved in replacing the complicated relay based machine control systems. Bedford Associates (Bedford , MA ) proposed something called a modular digital controller (MODICON) to a major US car manufacturer. Other companies at the time proposed computer based upon the PDP – 8. The MODICON 084 brought the world's first PLC into commercial production.

When production requirements changed so did the control system. This becomes very expensive when the change is frequent. Since relays are mechanical devices they also have a limited lifetime which required strict adhesion to maintenance schedules. Troubleshooting was also quite tedious when so many relays are involved. Now picture a machine control panel that included many, possibly hundreds or thousands, of individual relays. The size could be mind boggling. How about the complicated initial wiring of so many individual devices! These relays would be individually wired together in a manner that would yield the desired outcome.

These new controllers also had to be easily programmed by maintenance and plant engineers. The lifetime had to be long and programming changes easily performed. They also had to survive the harsh industrial environment. That's a lot to ask ! The answers were to use a programming technique most people were already familiar with and replace mechanical parts with solid – state ones.

In the mid70's the dominant PLC technologies were sequencer state machines and the bit – slice based CPU. The AMD 2901 and 2903 were quite popular in MODICON and A - B PLC's. Conventional microprocessors lacked the power to quickly solve PLC logic in all but the smallest PLC's. As conventional microprocessor evolved, larger and larger PLC's were being based upon them. However, even today some are still based upon the 2903. MODICON has yet to build a faster PLC than their 984A/B/X which was based upon the 2901.

Communications abilities began to appear in approximately 1973. The first such system was MODICON' s MODBUS. The PLC could now talk to other PLC' s and they could be far away from the actual machine they were controlling. They could also now be used to send and receive varying voltages to allow them to enter the analog

world. Unfortunately, the lack of standardization coupled with continually changing technology has made PLC communications a nightmare of incompatible protocols and physical networks.

The 80's saw an attempt to standardize communications with General Motor's manufacturing automation protocol. it was also a time for reducing the size of the PLC and making them software programmable through symbolic programming on personal computers instead of dedicated programming terminals or handheld programmers.

The 90's have seen a gradual reduction in the introduction of new protocols, and the modernization of the physical layers of some of the more popular protocols that survived the 1980's. The latest standard has tried to merge PLC – programming languages under one international standard. We now have PLC's that are programmable in function block diagrams, instruction list, C and structured text all at the same time! PC's are also being used to replace PLC's in some applications. The original company who commissioned the MODICON 084 has actually switched to a PC based control system.

# **3.GENERAL PHYSICAL BUILD MECHANISM**

PLC's are separated into two according to their building mechanisms.

### **3.1Compact PLC's**

Compact PLC's are manufactured such that all units forming the PLC are placed in a case. They are low price PLC with lower capacity. They are usually preferred by small or medium size machine manufacturers. In some types compact enlargement module is present.

#### **3.2Modular PLC's**

They are formed by combining separate modules together in a board. They can have different memory capacity, I / O numbers, power supply up to the necessary limits.

Some examples: SIEMENS S5-115U, SIEMENS S7-200 MITSUBISHI PC40, TEXAS INSTRUMENTS PLC'S, KLOCKNER – MOELLER PS316 OMRON C200H.

### **3.3. BASIC INSTRUCTION**

Each program written in PLC are started in 2 ways. One at these that we can draw the program with its symbols in the location called Ladder Diagram and load it to the computer as this. The second one is that we can make direct attribution using the key team of PLC. Because of this it will be told example symbol and attribution us. Instructions later whole LOD instruction and the other instructions are being stated.

### a) LOD Instructions:

This instructions is used at the beginning of logic diagram lines. It can be used once back by back or more than once to determine the situation at the beginning of the instructions such as AND LOD, OR LOD, SFR, CNT, TIM. As you see below an input relay is wanted to be loaded as a program. Symbol of it is declared as a show in ladder diagram. Program list from the statement.

This program is loaded as 0 LOD 1 and 0 which is seen an address must be given in each line of the end one by one starting from each line of the program. Value is appointed to each line orderly. We have mentioned before which numbers are separated for shift register, output, input, special relay, timer counter. Imaginary internal relay at the machine PLC.

We can divide our load process into 4 groups according to our functions.

### b) Input, Output Internal and Special Relays:

In the examples above example relay circuit of relay in ladder diagram and how the process of key and as a result of this the format seen in deplay was given.

We can choose a value between 0 and 77 except 8 and 9 in the example of input.

We can choose a value between 200 and 277 cxccpt 8 and 9 in the example of output.

We can choose a value between 400 and 697 except 8.and 9 in the example of internal relay

You can use special relay-which you need are between 700-717 in the example of special relay for example I use pulse generator of clock for one speed with special relay 714.

### c) Timer:

I wanted to use T8 timer from the 80 timer between 0-79 including 8 and 9 here aud you see how the load process had been done.

### d) Counter:

You can use any counter between 0 and 46 including 8 and 9. Load process is the saute as aside.

### e) Shift Register:

You can use any register from 128 of them between 0 and 127 including 8 and 9. Shift register numbered I was loaded in the next side.

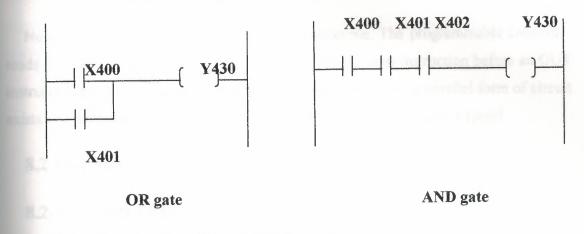

### f) AND Instruction:

It is same as AND logic we studied in Logic lessons. Both keys that are connected each other rapidly are on. output is on and is the other situations it becomes OFF in logic. In. a multiplying processes both inputs are 1 than output is 1. And had it ended with 2 limit switches and 1 solenoid valve in~order to understand the logic better by diagranis; it is stated as relay ladder diagnain and logic diagratn. So we cati telt iliat LS 1 relay A and; LS 2 relay is B input and output is .Y. In suck equality it is that Y=A.B according to the compulsion Of Boolean. If both inputs are 1 (ON) Y output will be ON. In other 3 probabilities, output Y will be 0 (OFF) You can see this in the table of truth.

As known, the series of TTL is Logic entegrate containing 4 and gate with 2 inputs in 7408. As in the circuit 1/4 has been made equal to ladder diagram by using 7408. In both of them The function of output and working are same.

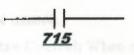

#### g) OR Instruction:

Or instruction has the same functions as or gate logic we studied in logic lessons. In here, just otily one of flie keys are OFF or 1 is enough for output to be 1 as 2 keys are connected in the parallel way As a result there is addition process and in this process one of the 2 parallel inputs is enough to be one. 1 gave 2 important information's with or instruction. One as thent is Out function that is symbolmed with 200 in the circle. I will speak about out flinction 2 or 3 classes later. But now, I gave output of parallel circuit, output 200 for file first time it means that: 1 mentioned that speciat relay 704 is a clock ptilse generator lint has f=1 HZ You see signal of clock pulse in the diagram. We determined time of I and 0 in. input relay of 36 by chance now so that nothing will be by chance in the following lessoni Let's accept that there is a time diagram for to learn Or let's ass,ame that input 3645 gained by niaking ON/OFF in the f~n. If we think that output 200 is connected to a lamb, the situations that lamb will be on are the times that output 200 is 1.

In this example. in order to understand or instructions better firstly, 2 limit switches were connected to each other rapidly and shown a lader diagram and a solenoid valve control in output of it. And same cIrcuit has heen gained Logic equality by using only lor gate of integrate of 7432. It is enou)41 to make on only one of the inputs for the outputs. to be ON in. 3 equaliavence circuit to make output OFF It is necessary to make both parallel inputs OFF. This position was shown in the truths table below.

### h) NOT Instructions:

It has the same duty as NOT gate that you studied in the logic lessons We take the opposite of the sign. If we have a look of the example above, they take the opposite of input relay 1 in PLC.. If you Carry out 1 logic level to input I from the outside, the sign is going to continue from B point as logic 0, because of the instruction of LOD NOT 1.

## **4.ADVANTAGES**

### 4.1 Accuracy

In relay control systems logical knowledge's carries in electro mechanical contactors, they can lose data because of mechanical errors. But PLC's are microprocessor based system so logical data are carried inside the processor, so that PLC's are more accurate than relay type of controllers.

6

### 4.2 Flexibility

When there is need of any change in control, relay type of controllers modification are hard, in PLC this change can be made with PLC programmer equipment.

### **4.3** Communication

PLC 's are computer based systems. So that they can transfers their data to another PC or they can take external inputs from another PC, with this specification we can control the system were they are we can effect the system with our PC. With relays ties is not possible.

### 4.4 Logic Control of Industrial Automation

Everyday examples of these systems are machines like dishwashers, clothes washers and dryers, and elevators. In these systems, the outputs tend to be 220 V AC power signals to motors, solenoids, and indicator lights, and the inputs are DC or AC signals from user interface switches, motion limit switches, binary liquid level sensors, etc. Another major function in these types of controllers is timing.

### 4.5 Data Areas

Data memory contains variable memory, and register, and output image register, internal memory bits, and special memory bits. This memory is accessed by a byte bit convention. For example to access bit 3 of Variable Memory byte 25 you would use the address V25.3.

The following table shows the identifiers and ranges for each of the data area memory types:

| Area Identifier | Data area       | CPU 212          | CPU 214         |

|-----------------|-----------------|------------------|-----------------|

| I               | Input           | 10.0 to 17.7     | 10.0 to 17.7    |

| Q               | Output          | Q0.0 to Q7.7     | Q0.0 to Q7.7    |

| М               | Internal memory | M0.0 to M15.7    | M0.0 to M31.7   |

| SM              | Special memory  | SM0.0 to SM 45.7 | SM0.0 to SM85.7 |

### 4.6 Data Object

V

The S7-200 has six kinds of devices with associated data: timers, counters, analog inputs, analog outputs, accumulators and high - speed counters. Each device has associated data. For example , the S7 - 200 has counter devices. Counters have a data value that maintains the current count value. There is also a bit value, which is set when the current value is greater than or equal to the present value. Since there are multiple devices are numbered from 0 to n. The corresponding data objects and object bits are also numbered.

The following table shows the identifiers and ranges for each of the data object memory types:

| Obj | ect Identifier | Object             | CPU 212       | CPU 214       |

|-----|----------------|--------------------|---------------|---------------|

|     | Т              | Timers             | T0 to T63     | T0 to T127    |

|     | С              | Counters           | C0 to C63     | C0 to C127    |

|     | AI             | Analog Input       | AIW0 to AIW30 | AIW0 to AIW30 |

|     | AQ             | Analog Output      | AQW0 to AQW30 | AQW0 to AQW30 |

|     | AC             | Accumulator        | AC0 to AC3    | AC0 to AC3    |

|     | НС             | High-Speed Counter | HC0           | HC0 to HC2    |

|     |                | Current            |               |               |

|     |                |                    |               |               |

|     |                |                    |               |               |

|     |                |                    |               |               |

|     |                |                    |               |               |

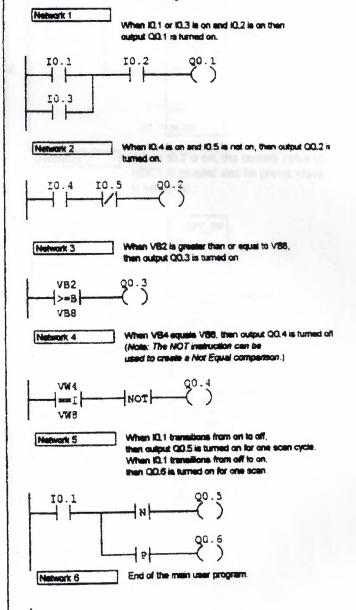

# **5.LADDER AND STL PROGRAM**

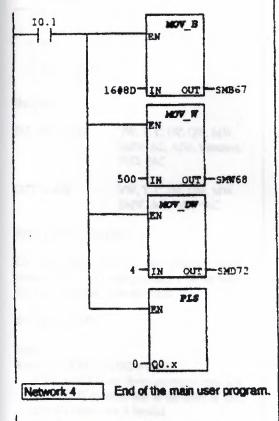

# SIEMENS SIMATIC S7- 200 PLC SAMPLE PROGRAM

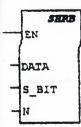

In this program;

Cotton to filament convert during the war. While cottons are to comb by the machine, separate operation during by the war cotton pieces are to gather of under the machine.

This program purposes are cotton pieces convert to back. With this program cotton cost decrease to less.

### **Program Work**

1- For the vakum if we gives the start, motor is start to work.

2- After the 15 s machines are made with raw and once vakum.

3- One machine and other machine between passed time 2 s, and vakum time is for the all machine 8 s.

4- If someone machine not work passed to other machine.

5- If fire alarm or tight alarm gives , fan motor and all other operations are stop. For the machines work are until push the button machines are not work.

| Input            | <u>Output</u>      |

|------------------|--------------------|

| - Start          | 1- Fan motor start |

| - Stop           | 2- Machine 1 vakum |

| - Reset          | 3- Machine 2 vakum |

| - Machine work 1 | 4- Machine 3 vakum |

| - Machine work 2 | 5- Fire alarm      |

# 6- Machine work 3

# 6-Tight alarm

# 7- Tight

| Symbol name           | Address | Note                             |

|-----------------------|---------|----------------------------------|

| Start                 | E0.0    | Start button                     |

| Stop                  | E0.1    | Stop button                      |

| Reset                 | E0.2    | Reset button                     |

| 1. Machine Work       | E0.3    | If 1. Machine Work send to sign  |

| 2. Machine Work       | E0.4    | If 2. Machine Work send to sign  |

| 3. Machine Work       | E0.5    | If 3. Machine Work send to sign  |

| Fire                  | E0.6    | If the fire alarm is coming      |

| Tight                 | E0.7    | Fan motor has tight              |

| Start – Output        | A0.0    | Fan motor is start               |

| Vakum 1               | A0.1    | 1. Machine Vakum Valve           |

| Vakum 2               | A0.2    | 2. Machine Vakum Valve           |

| Vakum 3               | A0.3    | 3. Machine Vakum Valve           |

| Fire Alarm            | A0.4    | If the fire sensor signal coming |

| Tight Alarm           | A0.5    | To throw the motor tight         |

| Cleanliness Air valve | A0.6    | Tube Cleanliness Valve           |

| Relay of Vakum        | T32     | After Start Vakum Relay          |

| Vakum Time            | T33     | Valves are Vakum Time            |

| Stop Time             | T34     | Between of Valves Stop Time      |

| Counter 0             | Z0      | 1. Machine Valve Work Counter    |

| Counter 1             | Z1      | 2. Machine Valve Work Counter    |

| Counter 2             | Z2      | 3. Machine Valve Work Counter    |

| Counter 3             | Z3      | Circle Reset                     |

| Jump Output           | A7.1    | Machines are not jump            |

### **6. MEMORY DESIGN**

Memory is used to store data. This stored information is related with which output sign will be store as, which shows input, and the structure of program necessary amount of memory. It stores special information parts, which is named as memory bit. 1 byte = 8 bit, 1024 byte = 1kbyte and the number of memory capacity is stated these units.

### a) I. Group Memories:

First group memories are Random Access Memory (RAM) and Read/Write (RIW). In these types memories if the energy is cut, the information is lost. If RAM is supplied program can be stored by battery that battery is in PLC device. When battery energy finishes, program will be erased.

### b) II Group Memories:

It is Read Only Memory (ROM). The type memory can be erased and programmable. It is divided four into groups;

6.1) PROM (Programmable Read-Only Memory): it is a special type of ROM.

PROM memory allows to writing of information in chip, these information are provided or there were at the beginning. The information can be written into ROM only one time.

The main disadvantage of PROM is no erasable and no Programmable. In PROM programming is doing as dissolve and pluck logic, for this reason, the erasing of erasable connections is process that there is no to turn back. For this reason, firstly all mistake control process must be finished.

6.2) EPROM (Erasable Programmable Read-Only Memory): this type is the memory *type* that is used in PLC devices. Written programmable firsfly, is store in EPROM memory and is sent central processing unit.

6.3) EAROM (Electrically Afterable Read-Only Memory): It is like EPROM memory, but to erase and ultraviolet light supply is not necessary. EAROM chip to clean by erasing, an eraser voltage is exercised to suitable pin. When chip erases one time, it can be programmed again.

# 6.4) EEPROM (Electrically Erasable Programmable Read-Only

**Memory):** In EEPROM memory type, when energy is cut, information cannot lose as EPROM. Special device is not necessary in writing and erasing processing. EEPROM or EPROM memories that are mounted to PLC make runs as stored program into records.

Data table stores information's, that are necessary to carry to the program, which includes information's such as output and input conditions, timers, and counter results and data records. Includes of table is divided two groups as conditions data and numbers (or codes) 0 and 1 conditions are ON/OFF conditions of information that records the place of bit. Data table is divided 3 sections. Input view table stores the condition of digital input that relations input interface circuits. As ON/OFF condition, in this unit results of input are stored as zero (0) or one (1).

Output view memory is order of bits that control the digital condition of devices which links interface of output. The logic conditions of output units are stored in this memory and it is taken from this logic level memory and transfers to output unit.

### **6.5. PROGRAMMING DEVICES**

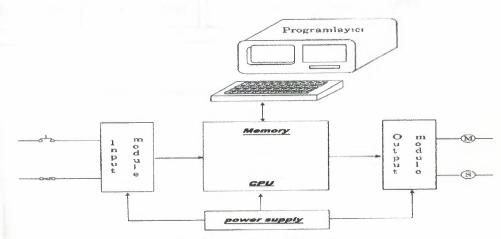

The most important one of features of programmable controller is to have programming elements, which are useflil. Programming device provides transformation between operator and circuit of controller (Fig. 7.3.1)

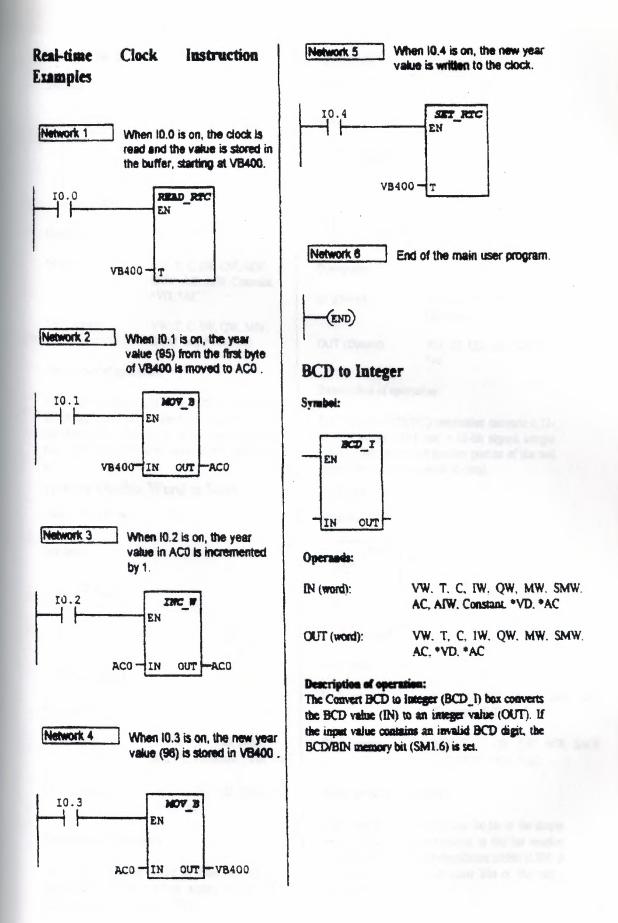

Figure.6.3.1. Transformation of pls circuits

Programming terminal relation between PLC memory and monitor. User sends programming device and PLC control program to device.

Generally, industrial CRT terminals in many devices are used for programmable controllers. These terminals include indicator units, keyboards and CPU and they provide to communcate necessary order.

The advantage of CRT is to check program is easily on monitor.

In small PLCs programming is used cheap, moveable, small and mini programmable devices. The momtor of this type of programming monitor is liquid crystal screen instead of CRT tube, which name LCD. On mini program there are LCD monitor program coding keys and special flinctions keys. FA2 of programming device DEC FA1 Junior module is shown at table 6.3.2.

| 963  | LOD | T 2 | 20  |          | PROG      | RAM LO    | ADER      |

|------|-----|-----|-----|----------|-----------|-----------|-----------|

| ADRS | TIM | CNT | SFR | MCS<br>7 | JMP<br>8  | PROM<br>9 | INST      |

| DELT | SET | RST | END | MCR<br>4 | JEND<br>5 | CMT<br>6  | ↓<br>VERI |

| MON  | OR  | SOT | OUT | F147     | F247<br>2 | 3         | Î<br>READ |

Figure. 6.3.2. Programming Device of DEC FA-1 PLC.

# 6.6 BASIC INSTRUCTION WORD

Instruction word list

a) Basic Instructions:

| Symbol | Name                 |

|--------|----------------------|

| LOD    | Load                 |

| AND    | AND                  |

| OR     | OR                   |

| OUT    | Output               |

| MCS    | Master Control Set   |

| MCR    | Master Control Reset |

| SOT    | Single Output        |

| TIM    | Timer                |

| CNT    | Counter              |

| SFR    | Shift Register       |

| END    | End                  |

| Set    | Set                  |

| RST    | Rese:                |

| JMP    | Jump                 |

| JEND   | Jump End             |

| NOT    | Not                  |

| FUN    | Function             |

### b) FUN (Function) Instructions:

We can divide the instructions into 2 parts. These are;

One - address instruction

Two - address instruction

There are 2 kinds of address instruction. Generally first address is the instruction word. In LOD, AND, OR, OUT, SET, RST, SOT instructions; there is a instruction word and number and addressing is obstructed with this that single addressed instruction.

Two addressed instructions; SPIt, SPIt NOT, TIM, CNT, FUN 100-146, FUN 200-246, TIM FUN, CNT FUN, FUN 147 and FUN 300. In this instructions first

addresses are give instruction word and instruction numbers ~xcept FUN 147, FUN 300). As for second addresses are present peculiarity according to instruction.

There are some deliver numbers that referenced by FAlJ at the below. c) Input:

0......7, 10......7, 20.....27, 30......37, 40......47, 50.......57,60.......67, 70.....77 are numbered like this. In here inputs are considered to OCTAL system which is between 0-77. If you attend 8,9,18,19,28,,29 78,79, numbers are not used. In octal there are 64 unit input number between 0-77 (except 8 and 9).

# d) Output:

200.....207, 210..... 217,220......227,230..... 237,240..... 247, 250......257, 260.....267 and 270 277 numbered. Like input there are 64 unit output numbers between 200-277 (except 8 and 9).

### e) Internal Relay:

| 400-407 | 490-497 | 580-587 |

|---------|---------|---------|

| 410-417 | 500-507 | 590-597 |

| 420-427 | 510-517 | 600-617 |

| 430-437 | 520-527 | 610-627 |

| 440-447 | 530-537 | 620-627 |

| 450-457 | 540-547 | 630-637 |

| 460-467 | 550-557 | 640-647 |

| 470-447 | 560-557 | 650-657 |

| 480-487 | 570-577 | 660-667 |

| 670-677 | 680-687 | 690-697 |

There are 240 units (30x8=240) internal relays between 400 and 697, we can appoint the TISNIER, COUNTER or FUN outputs to the any of 240 sensor and then can use of this sensor for take new data or count value.

### f) Special Internal Relay:

There are 16 units become 700-707 and 710-717. As an example of these, we can use the signal generator which produces 1 sec clock sign, that means we can use 1 Hz clock pulse sing ready.

We can use the signal generator which produces 0.1 sec clock sign that means 10 Hz clock pulse sign ready.

### g) Timer:

There are totally 80 unit timers between 0 and 79. If you attent you can use 8 ou can use any of TIMER that include 0 and 79. In there its enough to know for totally there are 80 unit TIMER that include 0-79.

### h) Counter:

Totally there are 45 unit counter between 0 and 44. If you attent you can use 8 and 9.

#### i)Reversible Counter:

It is counter which can be counted forward or review. While other counters can only count forward counters number 4546 can count forward or review. Counter 45 has up and down pulse input edge yet counter 46 is connected to only one input of up/down situation and when this edge is 1 up and when it be comes 0 it counts down.

### j) Shift Register:

There are 128 shift register between 0 and 27 including 8-9.

### k) Single Output:

We can use 96 SOT flinctions between 0 and 95 including 8-9.

### 1) Data Register:

Between DRO and DR99 and between 800 and 899, we have 100 data register.

# 6.7. FA1J SERIES ALLOCATION NUMBERS OF SPECIAL

### RELAYS

As known special relays are 700 and 717 relays except 708 and 704 from these numbers 700 and 705 are unused.

701 and 702 Stan Control: When input number 0, which used to start the program is on or if number 500 has been appointed to automatic start process. It starts to turn the program on. Special relays 701 and 702 are off the process of the program is stopped.

**703 All Output OFF:** All outputs between 200 and 277 are off when special relay 703 turns into ON.

**704 Initialize Pulse:** Special flag (1 scan time) 704 becomes on as much as the time equalling I scan time. When program FA1J started being processed.

**704 Numerical Value Error:** Is there an error in computing instructions results. 706 becomes on for example; if the result of a subtraction process is lower than -10.000, special relay 706 becomes on. They make sure that the program is correct from the point of view numerical process while they register the programs.

707 Curry and Borrow: It there is carry or borrow in the results at computing instructions. 707 is set for example; in a addition process the total of 2 numbers are higher than 9999,707 is on.

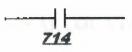

713 1 sec. Timer Reset: When 713 is on special relay 714 is always reset mode.

714 1 sec. Clock: It is possible to take signal generator producing clock sign for one second or clock pulse sign for 1 Hz from special relay 714.

17

715 100-msec. Clock: We can remove our clock pulse that is for 10 speed by using special relay output of 715 with this sign.

716 Timer/Counter Preset Value Changed: Special relay 716 becomes on when timer counter preset value has been changed into unit of FAIJ CPU. It is possible to delete 716 when pressed key of TR S, ENTR and ENTR. If a program is registered in memory.

717 In-operation Output: Relay 717 is always on while FA1J is operating of the program has ended this relay becomes off

# 7- TYPES OF PLC

The increasing demand from industry for programmable controllers that can be applied to different forms and sizes of control tasks has resulted in most manufacturers producing a range of PLCs with various levels of performance and facilities.

Typical rough definitions of PLC size are given in terms of program memory size and the maximum number of input/ output points the system can support. Table 8.1 gives an example of these categories.

| <br>PC size | Max I / O points | Use memory size |

|-------------|------------------|-----------------|

| Small       | 40 /40           | 1 K             |

| Medium      | 128 /128         | 4 K.            |

| Large       | > 128 / >128     | >4 K            |

# **Table 7.1 Categories of PLC**

However, to evaluate properly any programmable controller we must consider many additional features such as its processor, cycle time language facilities, functions, expansion capabilities.

A brief outline of the characteristics of small, medium of large programmable controller is given below, together with typical applications.

# 7.1 Small PLC s

In general, small and 'mini' PLC s (figure 8.2) are designed as robust, compact units which can be mounted on or beside the equipment to be controlled. They are mainly used the replaced hard – wired logic relays, timers, counters. That control individual items of plant or machinery, but can also be used to coordinate several machines working in conjunction with each other.

Small programmable controllers can normally have their total I / O expanded by adding one or two I / O modules, but if any further developments are required this will often mean replacement of the complete unit. This end of the market is very much concerned with non – specialist end – users, therefore ease of programming and a 'familiar' circuit format are desirable. Competition between manufacturers is extremely fierce in this field, as they vie to obtain a maximum share in this partially developed sector of the market.

A single processor is normally used, and programming facilities are kept at a fairly basic level, including conventional sequencing controls and simple standard functions: e.g. timers and counters. Programming of small PLC s is by way of logic instruction list(mnemonics) or relay ladder diagrams.

Program storage is by EPROM or battery – backed RAM. There is now a trend towards EEPROM memory with on – board programming facilities on several controllers.

# Table 7.2 Features of a typical small PLC – Mitsubishi F20

| 320 – step memory (CMOS battery – backed RAM)<br>Ladder logic or instruction set using hand – held or graphic LCD |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                   |  |  |  |

|                                                                                                                   |  |  |  |

|                                                                                                                   |  |  |  |

| 8,                                                                                                                |  |  |  |

|                                                                                                                   |  |  |  |

|                                                                                                                   |  |  |  |

| a of L                                                                                                            |  |  |  |

| f                                                                                                                 |  |  |  |

# 7. 2 Medium – sized PLC s

In this range modular construction predominates with plug - in modules based around the Euro card 19 inch rack format or another rack mounting system. This construction allows the simple upgrading or expansion of the system by fitting additional I / O cards in to the cards into the rack , since most rack systems have space for several extra function cards. Boards are usually ' rugged zed ' to allow reliable operation over a range of environments.

In general this type of PLC is applied to logic control tasks that cannot be met by small controllers due to insufficient I / O provision, or because the control task is likely to be extended in the future. This might require the replacement of a small PLC, where as a modular system can be expanded to a much greater extent, allowing for growth. A medium - sized PLC may therefore be financially more attractive in the long term.

20

Communications facilities are likely to provided, enabling the PLC to be including in a ' distributed control ' system.

Combinations of a single and multi – bit processor are likely within the CPU. For programming , standard instructions or ladder and logic diagrams are available. Programming is normally carried out via a small 'keypad or a VDU terminal.( If different sizes of PLC are purchased from a single manufacturer , it is likely that programs and programming panels will be compatible between the machines.

# 7.3 Large PLC'S

Where control of very large numbers of input and output points is necessary or complex control functions are required, a large programmable controller is the obvious choice. Large PLC s are designed for use in large plants or on large machines requiring continuous control. They are also employed as supervisory controllers to monitor and control several other PLC s or intelligent machines. e. g. CNC tools

Modular construction in Euro card format is standard, with a wide range of function cards available including analog input / output modules. There is a move towards 16 - bit processor, and also multi – processor usage in order to efficiently handle a large range of differing control tasks. For example;

• 16 – bit processor as main processor for digital arithmetic and text handling.

• Single – bit processor as co – or parallel processor for fast counting, storage etc.

• Peripheral processor for handling additional tasks which are time – dependent or

time - critical, such as:

Closed - loop (PID) control

**Position controls**

Floating – point numerical calculations

Diagnostics and monitoring

Communications for decentralized

**Process mimics**

Remote input / output racks.

This multi – processor solution optimizes the performance of the overall system as regards versatility and processing speed, allowing the PLC to handle very large programs of 100 K instructions or more. Memory cards can now provide several megabytes of CMOS RAM or EPROM storage.

### 7.4 Remote input / output

When large numbers of input / output points are located a considerable distance away from the programmable controller, it is uneconomic to run connecting cables to every point. A solution to this problem is to site a remote I / O unit near to the desired I / O points. This acts as a concentrator to monitor all inputs and transmit their status over a single serial communications link to the programmable controller. Once output signals have been produced by the PLC they are fed back along the communications cable to the remote I / O unit, which converts the serial data into the individual output signals to drive the process.

# 7.5 Programming large PLC s

Virtually any function can be programmed, using the familiar ladder symbols via a graphics terminal or personal computer. Parameters are passed to relevant modules either by incorporating constants in to the ladder, or via on – screen menus for that module.

There may in addition be computer – oriented languages which allow programming of function modules and subroutines.

There is progress towards standardization of programming languages, with programs becoming easier to over – view through improvement of text handling, hand improved documentation facilities. This is assisted by the application of personal computers as work stations.

## 7.6 Developments

Present trends include the integration of process data from a PLC into management data bases, etc. This allows immediate presentation of information to those involved in scheduling,

production and planning.

The need to pass process information between PC s, PLC sand other devices within an automated plant has resulted in the provision of a communications capability on all but the smallest controller. The development of local area networks (LAN) and in particular the recent MAP specification by General Motors (manufacturing automation protocol) provides the communication link to integrate all levels of control systems.

# 8 – PROGRAMMING OF PLC SYSTEMS

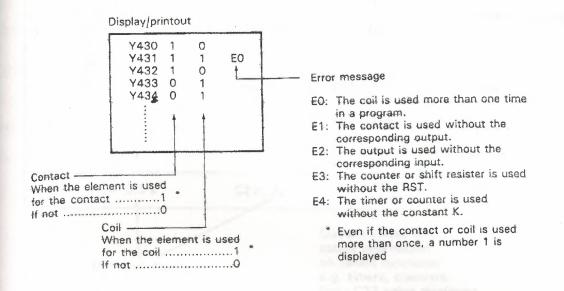

In the previous chapter we were introduced to logic instruction sets for programming PLC systems. The complete sets of basic logic instruction for two common programmable controllers are given below. Note the inclusion in these lists of additional instructions ORB and ANB to allow programming of more complex, multi branch circuits. The use of all these instructions and others is dealt with in this chapter. Some typical instruction sets for Texas instruments and Mitsubishi PLC s are given in table 8.1

| Texas Instruments |                     | Mitsubishi A series |                      |  |

|-------------------|---------------------|---------------------|----------------------|--|

| Mnemonic          | Action              | Mnem                | onic Action          |  |

| STR               | Store               | LD                  | Start rung           |  |

|                   |                     |                     | with an open contact |  |

| OUT               | Output              | OUT                 | Output               |  |

| AND               | Series components   | AND                 | Series elements      |  |

| OR                | Parallel components | OR                  | Parallel elements    |  |

| NOT               | Inverse action      | I                   | As for not           |  |

|                   |                     | ORB                 | Or together parallel |  |

|                   |                     |                     | branches             |  |

|                   |                     | ANB                 | And together series  |  |

|                   |                     |                     | circuit blocks       |  |

Table8.1 Typical logic instruction sets.

# 8.1 Logic instruction sets and graphic programming

In the last chapter we introduced logic instructions as the basic programming language for programmable controllers. Although logic instructions are relatively easy to learn and use , it can be extremely time – consuming to check and relate a large coded program to the actual circuit function.

In addition, logic instructions tend to vary between different types of PLC.

If a factory or plant is equipped with a range of different controllers ( a common situation ), confusion can result over differences in the instruction sets.

### RELAY LOGIC SYMBOLS: (MITSUBISHI PLC)

A preferable alternative is to use a graphic programmer, as available for several programmable controllers including the small Mitsubishi and Toshiba models from Japan. Graphic programming allows the user to enter his program as a symbolic ladder circuit layout, using standard logic symbols to represent input contacts, output coils, etc. as shown in the about figure. This approach is more user friendly than programming with mnemonic logic instructions, and can be considered as a higher – level form of language.

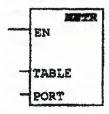

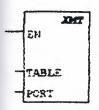

Special instruction circuit block

The programming panel translates or compiles these graphic symbols in to machine instructions that are stored in the PLC memory, relieving the user of this task.

Different types of graphic programmer are normally used for each family of programmable controller, but they all support similar graphic circuit conventions. Smaller, hand – held panels are common for the small to medium – sized PLCs

25

although the same programming panel is often used as a 'field programmer' for these and larger PLCs in the same family. However, the majority of graphic programming for larger systems is carried out on terminal – sized units. Some of these units are also semi portable, and may be operated alongside the PLC system under commissioning or test in – plant. In addition to screen displays, virtually all graphic programming stations can drive printers for hard copy of programs and \ or status information, plus program storage via battery – backed RAM or tape  $\$  floppy disk. The facility to load resident programs into EPROM IC s may be available on more expensive units.

## 8.1-1 Input /output numbering

It was previously stated that different PLC manufacturers use different numbering systems for input/output points and other functions within the controller.

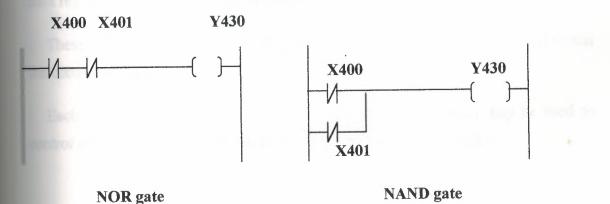

# 8.1-2 Negation – NAND and NOR gates

These logic functions can be produced in ladder form simply by replacing all contacts with their inverse, AND becomes ANI; OR becomes ORI; etc. this changes the function of the circuit.

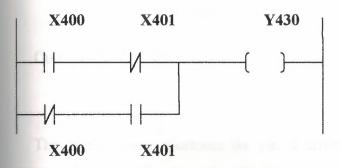

## 8.1-3 Exclusive – OR gate

This is different form the normal OR gates as it gives an output of 1 when either one input or the other is on , but not both. This is comparable to two parallel circuits , each with one make and one break contact in series as shown in exclusive OR gate figure.

**EXCLUSIVE – OR gate**

Note the use of an ORB instruction in this example. The programmable controller reads the first two instructions, then finds another rung start instruction before an OUT instruction has been executed. The CPU therefore realizes that a parallel form of circuit exists and reads the subsequent instructions until an ORB instruction is found.

## **8.2** Facilities

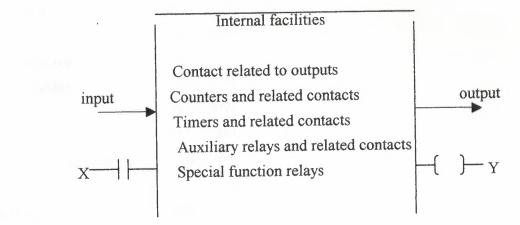

## **8.2-1 Standard PLC functions**

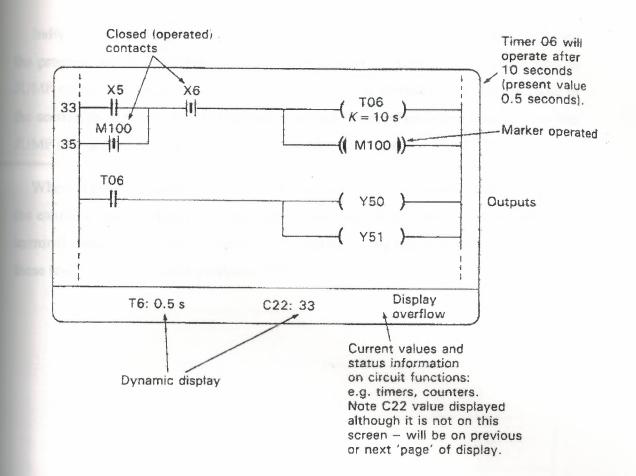

In addition to the series and parallel connection of input and output contacts, the majority of control tasks involve the use of time delays, event counting, storage of process status data, etc. All of these requirements can be met using standard features found on most programmable controllers. These include timers, counters, markers and shift registers, easily controlled using ladder diagrams or logic instructions.

These internal functions are not physical input or output. They are simulated within the controller.

Each function can be programmed with related contacts which may be used to control different elements in the program. As with physical inputs and

outputs, certain number ranges are allocated to each block of functions. The number range will depend both on the size of a PLC, and the manufacturer. For example, for the Mitsubishi F- 40 series, the details are as follows:

Timers T

450 - 457

550 - 557

Counters C

460 - 467

560 - 567

The information illustrates the use of different number ranges assigned to each supported function. For example, the timer circuits for this programmable controller are addressed from 450 to 457 and 550 to 557, a total of 16 timers. It is the specified number that identifies a function and its point to the PLC, not the prefix letter. This prefixes are included only to aid the operator.

The functions listed are provided on most programmable controllers, although the exact format will vary between manufacturers. Other functions may also exist, either as standard or by the selection and fitting of function modules to the PLC rack.

| PC (F40) I/O ASSIGN         | MENTS          |

|-----------------------------|----------------|

| Inputs: 24 points           | 400 - 407      |

| istro                       | 410 - 413      |

|                             |                |

|                             | 500 - 507      |

|                             | 510 - 513      |

|                             |                |

| Outputs: 16 points          | 430 - 437      |

| -                           | 530 - 537      |

|                             |                |

| Timers: 16 points           | 450 - 457      |

|                             | 550 - 557      |

|                             |                |

| Counters: 16 points         | 460 – 467      |

| In contained in the second  | 560 - 567      |

| Auxiliary control           | 100 - 107      |

| Relays:128 points           | 170 – 177      |

|                             | 200 - 207      |

|                             | 270 - 277      |

| Battery - backed:64 points  | } 300 - 307    |

| Special function            | )<br>370 – 377 |

|                             |                |

| Auxiliary relays ; 5 points |                |

| 70, 71, 72, 75 ,77          |                |

# Figure 8.2 Typical number assignments to internal functions

The operation and use of the listed standard functions is covered in the following sections.

## 8.2-2 Markers / auxiliary relays

Often termed control relays or flags, these provide general memory for the

programmer, plus associated contacts. They also form the basis for shift – register construction. Normally a group of markers with battery back-up is provided allowing process status information to be retained in the event of a power failure. These markers can be used to ensure safe startup \ shut down of process plant by including them as necessary in the logic sequence.

Referring, the Mitsubishi F40 has:

128 auxiliary (marker )relays

64 battery - backed markers

# 8.2-3 Ghost contacts

In certain cases it will be necessary to derive an output from the combined logic of several ladder rungs, due to the number of contacts involved. The straight forward way of providing this is to common – up the respective circuit rungs and drive an internal relay or marker(M). This acts in the same manner as a 'physical' relay, in that it can have associated contacts – except for the fact that it is simulated by software within the programmable controller, and has no external appearance whatsoever!

In common with other internal functions, auxiliary relays / marker can be programmed with as many associated contacts as desired. These contacts may be used anywhere in a ladder program as elements in a logic circuit or as control contacts driving output relays or other functions.

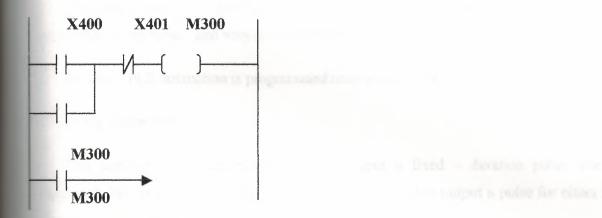

### 8.2-4 Retentive battery – backed relays

If power is cut of or interrupted whilst the programmable controller is operating, the output relays and all standard marker relays will be turned off. Thus when power is restored, all contacts associated with output relays and markers will be of possibly resulting in incorrect sequencing. When control tasks have to restart automatically after a power failure, the use of battery – backed markers is required. In the above

PLC, there are 64 retentive marker points, which can be programmed as for ordinary markers, only storing pre – power failure information that is available once the system is restarted.

In figure 8.3 retentive marker M300 is used to retain data in the event of a power failure. Once input X400 is closed to operate the M300 marker, M300 latches via it is associated contact.

#### Figure 8.3 Retentive marker used in a latch circuit

So even if X400 is opened due to a power failure, the circuit is holds on restart due to M300 retaining the operated status and placing its associated contacts in the operated positions.

Obviously X401 still controls the circuit, and if this input is likely to be energized (opened) by a power – failure situation, than a further stage of protection may be used.

#### 8.2-5 Optional functions on auxiliary relays

From the above text it is apparent that auxiliary relays constitute an important facility in any programmable controller. This is basically due to their ability to control large numbers of associated contacts and perform as intermediate switching elements in many different types of control circuit.

In addition, many PLC manufacturers have provided additional, programmable functions associated with these auxiliary relays, to further extend their usefulness. A very common example is a 'pulse' function that allows any designated marker to produce a fixed – duration pulse at its contacts when operated , rather than the normal d. c. level change.

This pulse output is irrespective of the duration of relay operation, thus providing a very useful tool for applications such as program triggering, setting / resetting of timers and counters etc.

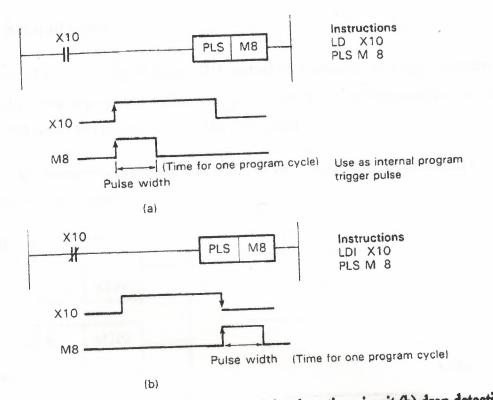

# **8.2-6** Pulse operation

The programming of this feature varies between controllers, but the general procedure is the same, and very straightforward.

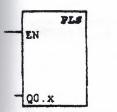

A pulse - PLS instruction is programmed onto an auxiliary relay number.

(in the figure 8.4)

This configures the designated relay to output a fixed – duration pulse when operated. The examples show how the relay may be used to output a pulse for either a positive or negative going input.

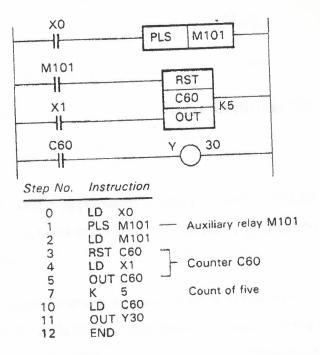

The circuit in figure 9.5 uses a PLS instruction on auxiliary relay 101 to provide a reset signal for a counter circuit C60. When input 0 is operated, a pulse is sent to relay 101, causing its contacts to pulse and reset counter C60. This is used here because counters and timers often require short duration resetting to allow the restart of the counting or timing

Figure 8.4 Pulse function on auxiliary relays (a)rise detection circuit (b) drop detection circuit

Figure 8.5 Providing a pulse input to a counter circuit

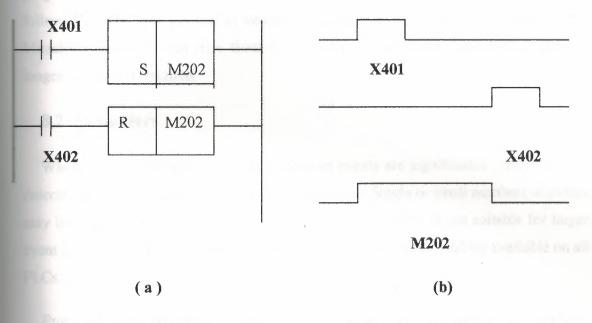

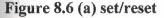

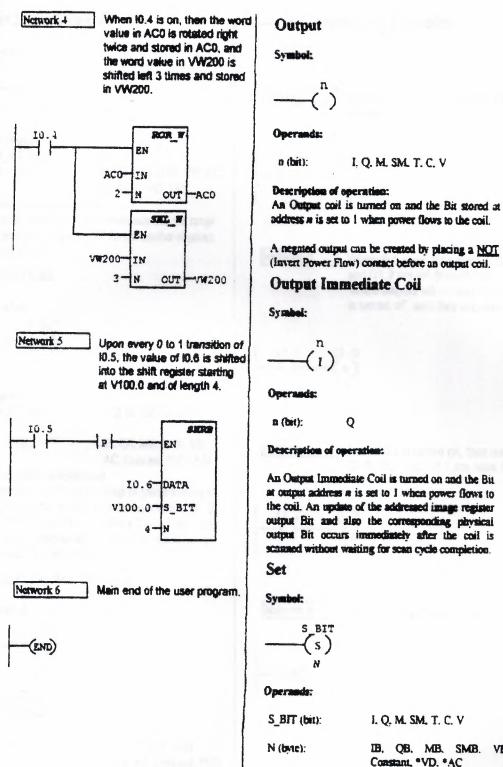

## 8.2-7 Set and reset

As with pulse – PLS, the ability to SET and RESET an auxiliary relay can often be produced by using appropriate instructions as in figure 8.6 These instructions are used to hold (latch) and reset the operation of the relay coils.

The S – set instruction causes the coil M202 to self – hold. This remains until a reset (R) instruction is activated.

Figure 8.6 (b) time chart

# 8.2-8 Timers

In a large proportion of control applications, there is a requirement for some aspect of timing control. PCs have software timer facilities that are very simple to program and use in a variety of situations.

The common method of programming a timer circuit is to specify the interval to be timed, and the conditions or events that are to start and / or stop the timer function. The initiating event may be produced by other internal or external signals to the controller. In this example the timer T450 is totally controlled by a contact related to output Y430. Thus, T450 begins timing only when Y430 is operated. This is caused by input X400 and not X401. Once activated, the timer will ' time – down' from its preset value – in this case 3.5 seconds – to zero, and then its associated contacts will operate.

As with any other PLC contact, the timer contacts may be used to drive succeeding stages of ladder circuitry. Here the T450 contact is controlling output Y431. The enabling path to a timer may also form the 'reset' path , causing the timer to reset to the preset value whenever the path is opened. This is the case with most small PCs. The enabling path may contain very involved logic, or only a single contact.

Techniques for programming the preset time value vary little between different programmable controllers ,usually requiring the entry of a constant (K) command followed by the time interval in seconds and tenths of a second. The timers on this Mitsubishi controller can time from 0.1 - 999.9 s , and can be cascaded to provide longer intervals if required.

## 8.2-9 Counters

Whenever the number of process actions or events are significance, they must be detected and stored in some manner by the controller. Single or small numbers of events may be remembered by using latched relay circuits, but this is not suitable for larger event counts. Here programmable counter circuits are desirable, and are available on all PLCs.

Provided as an internal function, counter circuits are programmed in a similar manner to the timer circuits covered above, but with the addition of a control path to signal event counts to the counter block. Most PLC counters work as subtraction or ' down' counters, as the current value is decremented from the programmed set value

## 8.2-10 Registers

From using a single internal or external relay as a memory device to store a single bit of information, other PLC facilities allow the storage of several bits of data at one time.

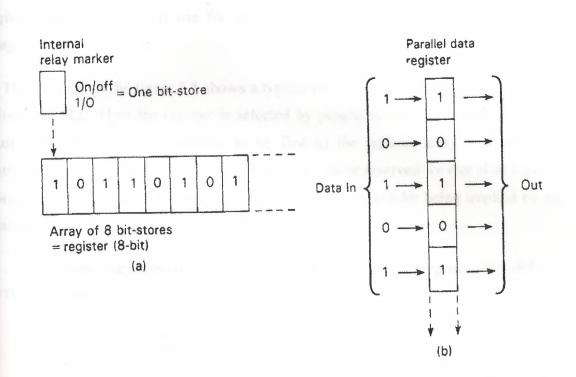

The device used to store the data is termed a register ,and commonly holds 8 or 16 bits of information. Registers can be thought of as arrays of individual bit – stores – in fact many programmable controllers form the data registers out of groups of auxiliary marker relays in the figure 8.7

Registers are very important for handling data that originates from sources than simple, single switches. Instead of binary data in one – bit – wide form, information in

a parallel data form may be read into and out of appropriately sized registers. Thus, data from devices such as thumbwheel switches, analog – to – digital converters, can be feed into appropriate PLC registers and used in later operations that will generate other bit – or byte – wide (8-bit) data to drive switched outputs or digital – to – analog conversion units.

Figure 8.7 Register storage concept (a) array of bit stores; (b) parallel data register

## 8.2-11 Shift registers

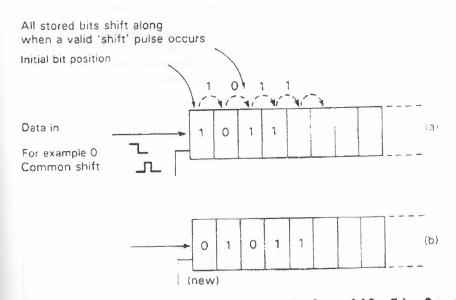

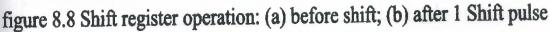

A shift register provides a storage area for a sequence of individual data bits that are offered in series to its input line. The data are moved through the register under control of a shift or clock line as in the figure 8.8. The effect of a valid shift pulse is to move all stored digits one bit further in to the register , entering any new data in to the 'freed' initial bit positions. Since a shift register will only be a certain size . for example 8 or 16 bits , then any data in the last bit of the register will be shifted out and lost.

The usefulness of a shift register (SR) lies in the ability to control other circuits or devices via associated SR contacts that are affected by the shifting data stream through the register. That is, as with marker relays, when a marker is ON any associated contacts are operated.

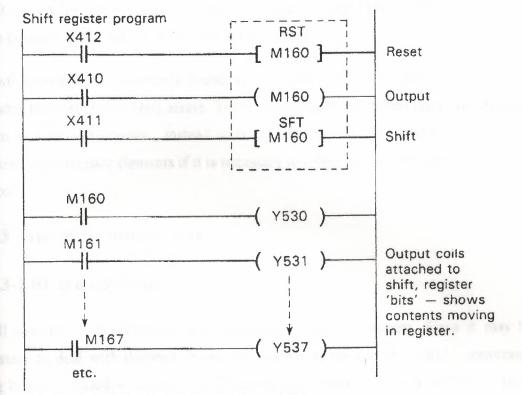

In programmable controllers, shift registers are commonly formed from groups of the auxiliary relays. This allocation is done automatically by the user programming

a 'shift – register function', which than reserves the chosen block of relays for that register and prohibits their use for any other function (including use as individual relays).

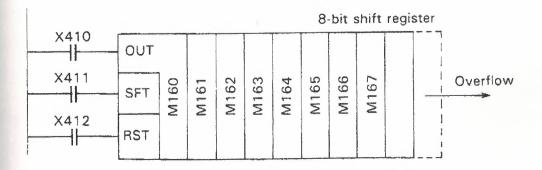

The example in the figure 8.8 shows a typical circuit for shift register operation on a Mitsubishi PLC. Here the register is selected by programming in the shift instruction against the auxiliary relay number to be first in the register array – M160. This instruction causes a block of relays – M160 – 167 – to be reserved for that shift register. Note that only the first relay had to be specified, the remainder being implied by the instructions.

This shows the controlling contacts on the input lines to the register – RESET. OUTPUT and SHIFT.

37

The auxiliary relays can be grouped in blocks of 8 to form 8- or 16-bit shift registers. This feature is programmed as shown below using M160–177 internal relays (only M160 is keyed in, the other bits being transparent).

The shift register contacts perform as follows:

RST – a pulse or closure resets SR contents to 0

OUT - logic level (0 or 1) offered to register on this rung.

SFT – pulse moves contents along one bit at a time (eventually contents are lost off the final bit memory).

Figure 8.9 Basic shift register circuit shift register Figure 8.10 Equivalent circuit of a

Note the M – contacts below the SR circuit that are used to drive output coils (M160 – 167 driving Y530 – 537).

It is easier to understand the function of the register if we look at an equivalent circuit in the figure 9.10. Here we can see the layout of other marker relays following M160. This helps us to visualize the shifting of data from bit to bit, affecting other parts of the circuitry as the data (1 or 0) in each bits change.

Shift registers are commonly found as 8 - bit or 16 - bit, and can usually be cascaded to create larger shift arrays. This allows data to be shifted out of one register and in to a second register, instead of being lost. Battery – backed markers can be selected as the register elements if it is necessary to retain register data through a power failure.

## **8.3 Arithmetic Instructions**

## 8.3-1 BCD numbering

All internal CPU operations are performed in binary numbers. Since it may be necessary to deal with decimal inputs and outputs in the outside world, conversion using binary – coded - decimal (BCD)numbering is provided on most PLCs. BCD numbering is briefly described in figure 9.11 Readers wanting further information are referred to the many texts dealing with number systems. When data is already in binary format, such as analog values, it is placed directly in registers for use by other instructions.

# (1) BIN (pure binary)

|             | X7  | X6 | X5    | X4     | X3      | X2      | X1 | XO | -           |  |

|-------------|-----|----|-------|--------|---------|---------|----|----|-------------|--|

| Upper digit | 1   | 1  | 0     | 1      | 0       | 0       | 1  | 1  | Lower digit |  |

| OFF. O      | 128 | 64 | 32    | 16     | 8       | 4       | 2  | 1  |             |  |

|             |     |    | 128 + | 64 + 1 | 6 + 2 + | 1 = 211 |    |    |             |  |

In the data made up of 8 bits from X0 to X7, the number 211 is expressed when X0, X1, X4, X6 and X7 are turned on (=1 in the above figure) and the others are turned off (=0 in the above figure).

# (2) BCD (binary-coded decimal)

|      |      |         | (800 | + 100} | + (40 +  | 20) + (4 | 4 + 2 + ' | 1) = 967 | r    |       |      |

|------|------|---------|------|--------|----------|----------|-----------|----------|------|-------|------|

|      | 100  | s digit |      | -      | 105      | digit    |           | 1        | 1 S  | digit |      |

| 800  | 400  | 200     | 100  | 80     | 40       | 20       | 10        | 8        | 4    | 2     | 1    |

| 1    | 0    | 0       | 1    | 0      | 1        | 1        | 0         | 0        |      |       |      |

| V113 | M112 | M111    | MITO | WITO/  | IVI I UU | T        | M104      |          | -    | 1     | 1    |

|      |      |         |      | 14107  | 1106     | M105     | M104      | M103     | MIUZ | MIUI  | MIOC |

----

BCD data is such that each digit of the decimal number is expressed in 4-bit binary. No digit will exceed 9.

E.g.: If both M103 and M102 are turned on (= 1) in the BCD data shown in the above figure it will result in an error.

The values of timers or counters may be treated as BCD

# Figure 8.11 (a) Binary and BCD number systems

# (b) Timer unit for data operations

# 8.3-2 Magnitude comparison

Magnitude comparison instructions are used to compare a digital value read from some input device or timer, etc., with a second value contained in a destination data register. Depending on the instruction - more than, less than, or equal - ,this will result in a further operation when the condition is met. For example, a temperature probe in a furnace returns an analog voltage representing the current internal temperature. This is converted in to a digital value by an analog – to – digital converter module on the PC, where it is read from input points by a data – transfer instruction and stored in data register D10. The process requires that if the temperature is less than 200 C, then the process must halt due to insufficient temperature.

If the temperature is greater than 200 C and less than 250 C, then the process operates at normal rate. If the temperature is between 250 and 280 C, than baking time is to be reduced to 3 minutes 25 seconds, and once temperature exceeds 280 C the process is to be suspended.

This the type of area where magnitude comparison can provide the necessary control, in conjunction with other circuitry to drive the plant equipment.

Other common applications include the checking of counter and timer values for action part – way through a counting sequence.

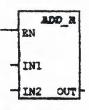

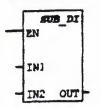

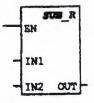

#### 8.3-3 Addition and subtraction instructions

These instructions are used to alter the value of data held in data registers by a certain amount. This may be used simply to add / subtract an offset to an input value before it is processed by other instructions. For example, when two different sensors are passing values to the controller and one sensor signal has to be compared against the other, but is a fundamentally smaller signal with a narrower output swing. It may be possible to add an offset to the smaller signal to bring it up near to the level of the larger one, thus allowing comparison to take place. The alternative would be to use signal conditioning units to raise the sensor output before the PLC - an expensive option.

Other uses of + and - include the alteration of counter and timer presets by programmed increments when certain conditions occur.

# 9 - LADDER PROGRAM DEVELOPMENT

# 9.1 Software Design

When ladder programs are being developed to control simple actions or equipment, the amount of planning and actual design work for these short programs is minimal, mainly because there is no requirement to link with other actions or sections within the program. The ladder networks involved are small enough to be easily understood in terms of circuit representation and operation. In practice, of course, circuits are not limited to AND or OR gates, often involving mixed logic functions together with the many other programmable functions provided by modern programmable controllers.

When larger and more complex control operations have to be performed, it quickly becomes apparent that an informal and unstructured approach to software design will only result in programs that are difficult to understand, modify, troubleshoot and document. The originator of such software may posses an understanding of its

operation, but this knowledge is unlikely to remain after even a short period of time away from that system.

In terms of design methodology, than, ladder programming is no different from conventional computer programming. Thus, considerable attention must be given to :

- \* Task definition / specification

- \* Software design techniques

- \* Documentation

- \* Program testing

# 9.1-1 System functions

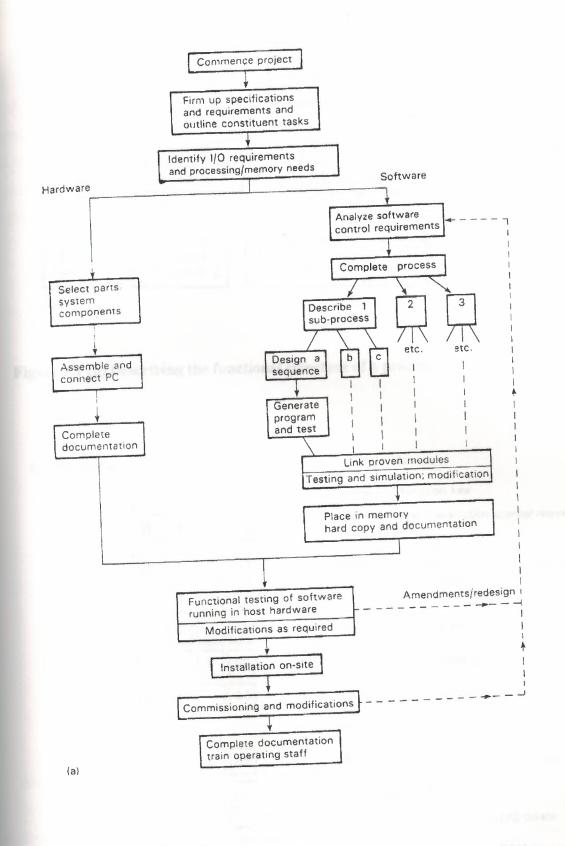

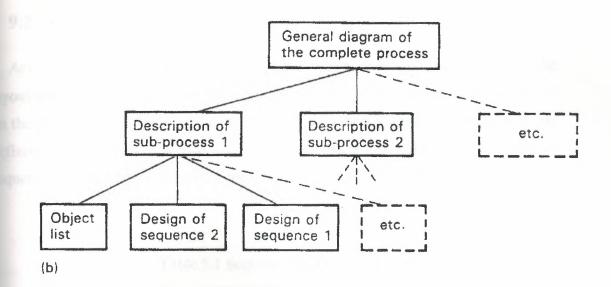

Most industrial control systems may be considered as a set of functional areas or blocks, in order to aid the understanding of how the total system operates. For example, each machine in a plant unit can be treated as a separate sub – process. Each machine process is then broken down in to blocks that may be described in terms of basic sequences and operations in the figure 10.1 illustrates this approach.

A functional block could for example, consist of all actions required to control a certain machine in the process.

Block 1 Block 2 Block 3

The division of programming tasks in to functional blocks is an important part of software design.

In logic programming, there are two different types of network that may be used to implement the function of a given block:

• Interlocks or combinational logic, where the output is purely dependent on the combination of the inputs at any instant in time.

• Sequential networks where the output is dependent not only on the actual inputs but on the sequence of the previous inputs and outputs.

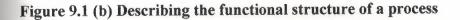

Figure 9.1 (a ) PC system design procedure

Figure 9.2 Graphic programming

45

# 9.2 Program Structure

At this stage in the investigation of design techniques, it is appropriate to discuss the layout and structure of PLC programs. It is sound practice to base any program layout on the general operating structure of all process – control systems. This means having definite sections dealing with operating modes, basic functions, process chain or sequence, signal outputs and status display, as indicated in Table 9.1.

Table 9.1 Sections of a PLC program

Start

**Operating modes and basic functions**

starting (basic) position

**Enabling / reset conditions**

**Process operation / sequence logic**

Signal outputs

**Status / indicator output**

Finish

#### a- Operating modes

**Basic position:** The controlled equipment is likely to have a basic or normal position, for example when all actuators are off and all limit switches are open. All these elements can be combined logically to signify and initialize a basic position, which may be programmed as a step in a sequential process.

*Enabling / reset conditions:* Most industrial processes have manual start and stop controls that may be incorporated in to the PLC program structure at this point. These would be included as enabling and reset contacts, having overall control of the PLC in terms of run or stop. There may also be a manual switch to enable the system outputs, which would allow the program to run without driving the physical outputs connected to the PLC a test function.

#### b- Process operation / sequence

This is the main topic of this chapter, involving the design and programming of combinational and sequential networks as necessary. The resultant outputs do not normally drive actuators directly, but instead are used to operate intermediate marker relays.

#### c- Signal output

Output signals to process actuators are formed by interlocking the resulting operation sequence outputs (markers) with any enabling conditions that exist in (a) above.

#### d- Status / indicator outputs

Process status is often displayed using indicator lambs or alarms, etc. Such elements are programmed in this section of the software.

By adopting this systematic approach to program structure, we can create reliable, easily understood software, which will allow rapid fault location and result in short process down times. The program that are developed in this chapter deal mainly with the topic of process operation, but will be structured in this manner where possible.

# 9.3 Further Sequential Control Techniques

In many practical applications, a control system has to deal with a process sequence that requires the concurrent operation and control of more than one step. Also, steps in sequence may require a time delay or event count as entry criteria for a succeeding step. To describe the different types of parallel operation, we use the conventions

In figure , actions B OR C are taken , depending on the result of test A2. Either action will allow entry to action D. In the figure shows the format for a process where

two actions A AND B are initialized once test A is true; also both tests B AND C must be true before progression to action D.

The equivalent function chart descriptions are illustrated. The number of parallel activities may be extended via the branching and converging rails. The chart in figure shows the tests that allow entry to steps B OR C, and also the individual tests or conditions that will allow resetting of the chosen step (test n and m). Notice the OR signs at each branch rail.

In figure the AND ing of steps is signified by the double connecting rails after test A and before test n. This means that all parallel steps (in this case B and C) are set once state A is active and test A is fulfilled.

# 9.4 Limitation of Ladder Programming

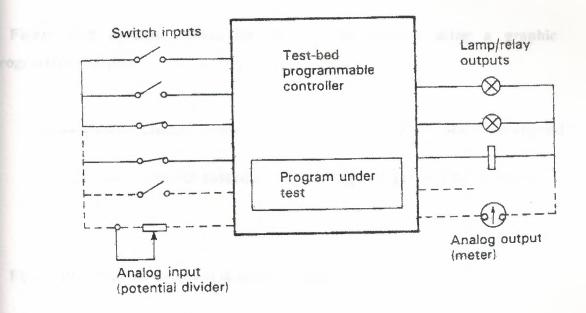

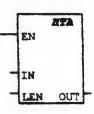

1 - Ladder programs are ideal for combinational / interlock tasks and simple sequential tasks.