# NEAR EAST UNIVERSITY

# **Faculty Of Engineering**

## **Department Of Computer Engineering**

**UART TRANSMITTER**

Graduating Project COM 400

Student:

Nadeem Hassan 20034377

Supervisor :

Mehmet Kadir Özakman MSc., P.Eng.

Nicosia 2008

#### ACKNOWLEDGEMENTS

First, I feel very hounded proud to pay my special regards to my project supervisor

#### 'Mehmet Kadir Ozkman',

Who always gave me courage me up to do something which could ever though about. He is the one gave me a hand in any all conditions of mine. He delivered me and did his best of efforts to make me able to complete my project.

One looks back with appreciation to the brilliant teachers, but with gratitude to those who touched our human feelings. The curriculum is so much necessary raw material, but warmth is the vital element for the growing plant and for the soul of the child.

#### Carl Jung

1875-1961, Swiss Psychiatrist

Secondly I want to pay special regards to my parents and especially humble affection teaching of ammi, and great support of abu whose enduring support just unforgettable and supporting me in all my life till today. I am nothing without their supports. They also encouraged me in nomatter what so ever the situation. I shall never forget their sacrifices for my education so that I can enjoy my successful life not only as well educated but also well mannered, respuctful human being. At the end once again I am thankful to all my siblings & friends of mine who helped me out and kept waiting for this moment of my life or even encouraged me to complete my graduation Computer Engineer.

#### ABSTRACT

All computer operating systems in use today support serial ports, because serial ports have been around for decades. Parallel ports are a more recent invention and are much faster than serial ports. USB ports are only a few years old, and will likely replace both serial and parallel ports completely over the next several years.

The name "serial" comes from the fact that a serial port "serializes" data. That is, it takes a byte of data and transmits the 8 bits in the byte one at a time. The advantage is that a serial port needs only one wire to transmit the 8 bits (while a parallel port needs 8). The disadvantage is that it takes 8 times longer to transmit the data than it would if there were 8 wires. Serial ports lower cable costs and make cables smaller.

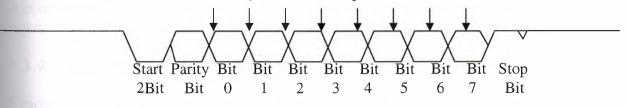

Before each byte of data, a serial port sends a start bit, which is a single bit with a value of 0. After each byte of data, it sends a stop bit to signal that the byte is complete. It may also send a parity bit.

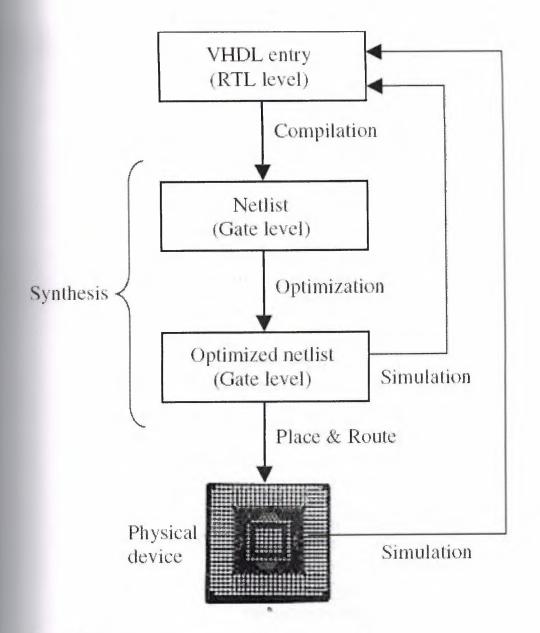

The synthesizer that generates the design taking the consideration of the Xilinx FPGA device that we specified at the top level design. Each programmable chips have own characteristic. The same VHDL code is portable and can be synthesized to different FPGA programmable devices. We used Xilinx development system and Xilinx programmable devices because each vendor's tools are developed its on programmable devices.

# TABLE OF CONTENTS

| TABLE OF CONTE             | NTS                                               | 1  |

|----------------------------|---------------------------------------------------|----|

| LIST OF ABBREVI            | ATIONS                                            |    |

|                            |                                                   |    |

|                            |                                                   |    |

|                            |                                                   |    |

|                            | TER                                               |    |

| 1. DEFINING THE            | FUNCTION.                                         | 5  |

|                            | OES                                               |    |

| 1.1.1 Specij               | fications:                                        | 5  |

|                            | y bit                                             |    |

| 1.1.3 Contr<br>1.1.4 Synch | ol word                                           | 6  |

| 1.1.4 Synch<br>1.1.5 Async | pronous Serial Transmission                       | 6  |

| 1.1.6 Inputs               | chronous Serial Transmission<br>s & Outputs       | 0  |

|                            | 2ge                                               |    |

|                            | age Body                                          |    |

|                            |                                                   |    |

|                            | DW                                                |    |

| <b>UART DESIGN FLO</b>     | )W                                                |    |

| <b>PROCEDURE STEP</b>      | °S                                                |    |

|                            | CODE OF UART TRANSMITTER                          |    |

|                            | ESIS                                              |    |

|                            | Test Bench                                        |    |

|                            | ng                                                |    |

|                            | 0                                                 |    |

|                            |                                                   |    |

| XILINX-ISE                 | ··········                                        | 40 |

| 2.1. ISE GENERAL I         | NFORMATION                                        |    |

| 2.1.1. Xilinx ISE          | Overview                                          |    |

|                            | ntry                                              |    |

|                            |                                                   |    |

|                            | tation                                            |    |

|                            | on                                                |    |

| 2.1.6. Device Co           | nfiguration                                       | 41 |

| 2.1.7. Architectu          | ire Support                                       |    |

|                            | Г NAVIGATOR                                       |    |

| 2.2.1. Project No          | avigator Overview                                 |    |

| 2.2.2. Project No          | avigator Main Window                              |    |

| 2.2.3. Using the           | Sources Window<br>Processes Window                |    |

|                            | ypes                                              |    |

| 2.2.5. Process St          | tatus                                             |    |

| 2.2.7. Running P           | Processes                                         | 40 |

| 2.2.8. Setting Pro         | ocess Properties                                  | 48 |

| 2.2.9. Using the           | Workspace                                         |    |

| 2.2.10. Using the          | e Transcript Window                               |    |

| 2.2.11. Using the          | e Toolbars                                        |    |

| 2.3. WORKING WITH          | PROJECTS                                          |    |

| 2.3.1. Creating a          | a Project                                         |    |

| 2.3.2. Working w           | vith Snapshots                                    |    |

|                            | PROJECTS SOURCE FILE                              |    |

|                            | a Source File                                     |    |

| 2.4.2. Source Fil          | le Types                                          | 59 |

| 2.4.3. Adding a S          | Source File to a Project                          | 64 |

|                            |                                                   |    |

| 2.4.4. Adding a (          | Copy of a Source File to a Project<br>Source File |    |

| 2.4.6. Removing Files from a Project                         |    |

|--------------------------------------------------------------|----|

| 2.4.7. Working with VHDL Libraries                           | 68 |

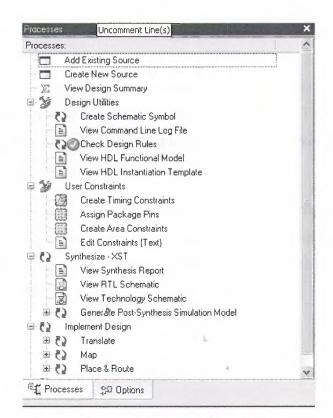

| 2.5. WORKING WITH PROCESSES                                  |    |

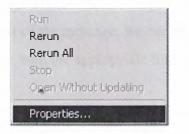

| 2.5.1. Running and Stopping Processes                        | 69 |

| 2.5.2. Setting Process Properties                            |    |

| 2.5.3. Setting Command Line Options using Process Properties |    |

| 2.6. WORKING WITH REPORTED DATA                              | 74 |

| 2.6.1. Reviewing Reports                                     | 74 |

| 2.6.2. Using the Design Summary for FPGAs.                   |    |

| 2.6.3. Using Message Filters                                 |    |

| CONCLUSION                                                   | 83 |

| REFERENCES                                                   |    |

|                                                              |    |

÷.

.

.

## List of Abbreviations.

- HDL Hardware description Language

- VHSIC Very High Speed Integrated Circuit

- ASIC Application Specific Integrated Circuits

- RAM Random Access Memory

- RTL Register transfer level

- FPGAQ Field Programmable Gate Arrays

- CLB configurable logic blocks

- PLD Programmable Logic Devices

- IEEE The Institute of Electrical and Electronics Engineers (read eye-

triple-e)

- IC Integrated circuits

- Ada Name of Programming Language

- UART Universal Asynchronous Receiver/Transmitter

## INTRODUCTION

The aim of this project is to design UART Transmitter. The project consists of two chapters with introduction in the beginning and conclusion at the end.

Chapter one presents is the design description of UART Transmitter and describing its main functions including ground realities in VHDL with its basic concepts.

Chapter two is about the Tool description of the Project in which detailed explanations about the Xilinx-ISE as well as description of the usage of project Navigator in VHDL and its basic concepts, function, design, syntaxes, language codes and different rule of statements which I used in my project.

Finally, the conclusion section presents the important results obtained within the project, references used in the whole task.

## CHAPTER 1

### UART Transmitter

#### DESIGN.

#### 1. Defining the Function.

#### 1.1 What it does:

UART stands for Universal Asynchronous Receiver and Transmitter. It is a protocol used in many places often including connecting terminals to computers. We'll look at the transmitter part of a UART.

#### 1.1.1 Specifications:

Data will be sent bit serially (one bit at a time) through a single line. The bit rate will be xx KHz. That means xx00 bits will arrive each second. (This is actually the rate for a MIDI UART communication. Computers generally run at 115.2 KHz). In each UART byte, there will be a start bit, the 8-bits of actually data, and a stop bit. This is shown below:

We do have parity bit present in here beside start bit. Therefore totally number of bit we have at the end is 12.

#### Total No of Bit to send = 12bits

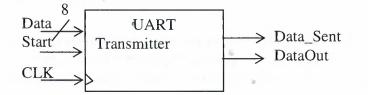

The transmitter's job is to get 8-bits of data (in parallel) and send each bit one at a time (DataOut) when it sees a Start signal. When our transmitter finishes transmitting, it tells us using a single bit output, Data\_Sent. Here's the transmitter's block's I/O:

The clock we will use in our circuit is a 16MHz clock.

Now let's build the STD for the transmitter. Here's some pseudo-code for our STD:

- 1) Wait for Start signal

- 2) Grab data (and adding a START bit and END bit for a total of 10-bits.)

- 3) For 10 bits:

- a. Put data bit to be sent on output (DataOut)

- b. Keep sending it until time to send next piece of data

c. Go to a.

Go to 1.

4)

Here we see that there are states that wait time, and a state that counts how many times we've passed through it. Few other complexities are control word and parity check.

#### 1.1.2 Parity bit.

A parity bit is a binary digit that is added to ensure that the number of bits with value of one in a given set of bits is always even or odd. Parity bits are used as the simplest error detecting code.

There are two variants of parity bits: even parity bit and odd parity bit. An even parity bit is set to 1 if the number of ones in a given set of bits is odd (making the *total* number of ones, including the parity bit, even). An odd parity bit is set to 1 if the number of ones in a given set of bits is even (making the *total* number of ones, including the parity bit, odd).

#### 1.1.3 Control word.

A control word figures out the number of bits to be send if they are less than 8 bit or not, that is just to recognize the number of bits to be send.

#### 1.1.4 Synchronous Serial Transmission.

Synchronous serial transmission requires that the sender and receiver share a clock with one another, or that the sender provide a strobe or other timing signal so that the receiver knows when to "read" the next bit of the data. In most forms of serial Synchronous communication, if there is no data available at a given instant to transmit, a fill character must be sent instead so that data is always being transmitted. Synchronous communication is usually more efficient because only data bits are transmitted between sender and receiver, and synchronous communication can be more costly if extra wiring and circuits are required to share a clock signal between the sender and receiver.

#### 1.1.5 Asynchronous Serial Transmission.

Asynchronous transmission allows data to be transmitted without the sender having to send a clock signal to the receiver. Instead, the sender and receiver must agree on timing parameters in advance and special bits are added to each word which are used to synchronize the sending and receiving units.

When a word is given to the UART for Asynchronous transmissions, a bit called the "Start Bit" is added to the beginning of each word that is to be transmitted. The Start Bit is used to alert the receiver that a word of data is about to be sent, and to force the clock in the receiver into synchronization with the clock in the transmitter.

#### 1.1.6 Inputs & Outputs

In my project here I use the following design,

| CTRL WORD= | Controls the number of bits    |

|------------|--------------------------------|

| TBR =      | Parallel Data                  |

| CRL=       | Load the control word          |

| MR=        | Master Rest                    |

| SFD=       | Controls the Output by TBRE    |

| TBRL=      | Parallel Data Load             |

| TRC=       | Transmit Clock                 |

| TBRE=      | Output controlled by SFD input |

| TRE=       | Transmit Error                 |

| TRO=       | Transmit Output                |

I used a pakage in the design.

1.1.7 Package.

A package is the physical packaging of a chip, for example, PG84, VQ100, and PC48. Where we define the functions. In the project of I have been defining the fuction of parity which is a standard logic vector input carring 0-7 bits totally 8 and returns the output. Package is simply nothing but a fuction of parity.

Code.

package my\_package is

FUNCTION parity(inputs: std\_logic\_vector(7 downto 0)) RETURN std\_logic;

end my\_package;

7

#### 1.1.8 Package Body.

The complete task for a package to be done in that particular package.

```

Code.

PACKAGE body my_package is

```

FUNCTION parity(inputs: std\_logic\_vector(7 downto 0)) RETURN std\_logic is variable temp: std\_logic;

```

begin

temp:='0';

for i in 7 downto 0 loop

temp:=temp xor inputs(i);

end loop;

return temp;

end parity;

```

end my\_package;

### Baud Rate.

Baud Rate represents the number of bits that are actually being sent over the media.

#### Data rate.

The amount of data that is actually moves from one medium to medium.

Modern high speed modems (2400, 9600, 14,400, and 19,200bps)

$10^{6}/19200$  bps\* = 52.083 µ sec

For each bit of data required to be sent= 16 clocks

So in 52.083µsec I have 16 clocks

Therefore,

52.083/16= 3.255125 µsec

- Clock High Time: 1.6276 μsec.

- Clock Low Time: 1.6276 µsec.

- Input Setup Time: 0 μsec.

- Output V

- $\downarrow$  Delay or Wait time: 10 µsec.

- Offset: 0 µsec

- Global Signals: GSR (FPGA)

Total clock Time =  $3.255125\mu$ sec

To calculate the clock frequency,

f=1/T $= \frac{1}{3.256 \times 10^{-6}}$  $= 10^3 10^3 / 3.256$

## f=307.125kHz

# $3.255125\mu sec = 307.125kHz$

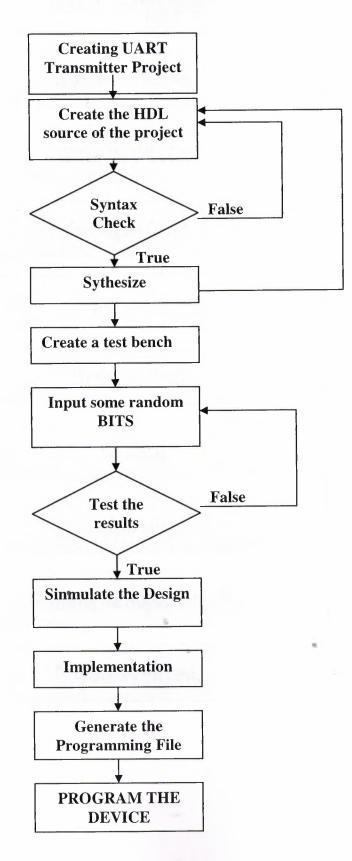

## VHDL DESIGN FLOW

Figure 1.1 Summary of VHDL design flow.

## UART DESIGN FLOW

# PROCEDURE STEPS

Defining Inputs/Outputs

**Defining the Function**

Writing the VHDL Code

**Entering the Design**

Synthesizing

Writing Test Bench

Simulating

Implementing

Generating the Programming File

**Programming the Device**

I use the xilinx – ISE integrated software environment to create the UART Transmitter Project and enter the VHDL code.

&

1.2.1 Create a New Project.

Create a new ISE project which will target the FPGA device on the SPARTAN-3E

## **New Project**

|                                                                            | rocess Window Help<br>X 1991 2 多文エチ 2 2 2 音目日日 チャ 2 43 36 日日日 日本 2 4 2 4 3 4 4 日日日 日本 2 4 2 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 |                       |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Open Project                                                               |                                                                                                                             |                       |

|                                                                            | 外後の後、118-21 1 高かす)間目 41 き x1 1000 「ns 「                                                                                     |                       |

| Close Project<br>Save Project As                                           | 1                                                                                                                           |                       |

| New Ctri+N<br>Open Ctri+O h<br>Close br                                    | 4 Create Date: 09:16:59 02/19/2008 6 Design Name: 7 Module Name: wert_transmitter - Behavioral                              | 6                     |

| Save As                                                                    | 8 Project Mane:<br>9 Target Devices:<br>10 Tool versions:<br>11 Description:<br>12                                          |                       |

| Print Preview Print Ctrl+P Recent Files                                    | 14 Dependencies:<br>15 Revision:<br>16 Revision 0.01 - File Created                                                         |                       |

| Recent Projects                                                            | 19 Additional Commence:<br>18<br>19                                                                                         |                       |

|                                                                            | 21 UART Transmitter Model (behavior modeling)<br>22<br>23<br>24                                                             |                       |

|                                                                            | 27                                                                                                                          | ,                     |

| Processes Sim Hierarchy - (                                                | 22 Design Summary 🔯 uari_transmitter which 🔯 uset_transmitter_tib which 🔯 Simulation                                        |                       |

| This is a Lite version<br>Simulator is doing cin<br>Finished circuit init: | cuit initialization process.                                                                                                |                       |

| Console Strong W                                                           | arnings 🔯 Tol Shell 🙀 Find in Files 🔯 Sin Console - uan_transmitter_b_vfr.d                                                 | Y<br>S NUM SCRI, VHDL |

| Enter a Name and Location for the Proje<br>Project Name: | Project Location                           |

|----------------------------------------------------------|--------------------------------------------|

| uart_Transmitter                                         | C:\V\$ilinx91i\Myprojects\uart_Transmitter |

|                                                          |                                            |

| Select the Type of Top-Level Source fo                   | r the Project                              |

| Top-Level Source Type:                                   |                                            |

| HDL                                                      | •                                          |

|                                                          |                                            |

|                                                          |                                            |

|                                                          |                                            |

|                                                          |                                            |

|                                                          |                                            |

|                                                          |                                            |

|                                                          |                                            |

|                                                          |                                            |

|                                                          |                                            |

|                                                          |                                            |

When the table is complete, your project properties will look like the following:

| Property Name                  | Value                        |   |

|--------------------------------|------------------------------|---|

| Product Category               | Ali                          | - |

| Family                         | Spartan 3E                   | - |

| Device                         | XC3S500E                     | - |

| Package                        | FG320                        | - |

| Speed                          | -5                           | - |

|                                |                              |   |

| Top-Level Source Type          | HDL                          | - |

| Synthesis Tool                 | XST (VHDL/Verilog)           | - |

| Simulator                      | ISE Simulator (VHDL/Verilog) | - |

| Preferred Language             | VHDL                         | • |

| Enable Enhanced Design Summary |                              | _ |

| Enable Message Filtering       |                              | - |

| Display Incremental Messages   |                              |   |

# Select Source Type.

| BMM File<br>IP (Coregen & Architecture Wizard)<br>MEM File<br>Schematic<br>Implementation Constraints File<br>State Diagram<br>Test Bench WaveForm<br>User Document<br>Verilog Module<br>Verilog Test Fixture<br>VHDL Module<br>VHDL Library<br>VHDL Package<br>VHDL Test Bench | File name:<br>UART_TRANSMITTER<br>Location:<br>C:\Users\zooper\Desktop\My Project\uart_transmitte |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| More Info                                                                                                                                                                                                                                                                       | < Back Next > Cancel                                                                              |

# Defining the Module.

|                             | rt_transmitter |   |     |     | 1111/1111.001/111110011111001111100011111000011100000110000 |     |   |

|-----------------------------|----------------|---|-----|-----|-------------------------------------------------------------|-----|---|

| Achitecture Name Behavioral |                |   |     |     |                                                             |     |   |

| tor Name                    | Direction      |   | Bus | MSB |                                                             | LSB |   |

| LWORD                       | in             | - |     |     | 4                                                           |     | 0 |

|                             | in             | • | 7   |     | 8                                                           |     | 0 |

| 91                          | in             | - |     |     |                                                             |     | 7 |

| IR.                         | in             | - |     |     |                                                             |     |   |

| IFD                         | in             | - |     |     |                                                             |     |   |

| TERL                        | in             | - |     |     |                                                             |     |   |

| RC                          | in             | - |     |     |                                                             |     |   |

| TERE                        | out            | - |     |     |                                                             |     | L |

| -2                          | out            | - |     |     |                                                             |     |   |

| 70                          | out            | - |     |     |                                                             |     |   |

# UART Transmitter Project in ISE.

| - ISE - C./Users\zooper\Desktap\My Project\uart_t        | ansmitter/uart_transmitter.ise - [uart_transmitter_tblvhd]                           | - ā X              |

|----------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------|

| Edit View Project Source Process Window He               | •                                                                                    | <b>.0</b> 8        |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

| ×                                                        | 29 LIBRARY leee;                                                                     | ٨                  |

| The Parameter Simulation                                 | 30 USE ieee.std_logic_l164.ALL;<br>31 USE ieee.std_logic_unsigned.all;               |                    |

| Let_transmitter<br>C no.lu500a-5fg320                    | 32 USE ieee.numeric_std.ALL;                                                         |                    |

| - Quart_transmitter_tb_vhd - behavior uart_transmitter_t |                                                                                      |                    |

| Uut - trans - behv (uart_transmitter.vhd)                | 34 ENTITY uart_transmitter_tb_vhd 15<br>35 END uart_transmitter_tb_vhd;              |                    |

| •                                                        | 36                                                                                   |                    |

| Shapehots Dubraries                                      | 37 ARCHITECTURE behavior OF uart_transmitter_tb_vhd IS<br>38                         |                    |

| ×                                                        | 39 Component Declaration for the Unit Under Test (UUT)                               |                    |

| cí uari_transmitler_tb_vhd:                              | 40 COMPONENT trans                                                                   | Ð                  |

| transmitter_tb_vhd - uari_transmitter_tb_vhd - beh       | <pre>41 PORT( 42 TRC : IN std logic;</pre>                                           |                    |

|                                                          | 43 MR : IN and lagio;                                                                |                    |

|                                                          | 44 IBRL : IN std_logic;                                                              |                    |

|                                                          | 45 SFD: IN std_logic;<br>46 CRL: IN std_logic;                                       |                    |

|                                                          | <pre>{6 CRL : IN std_logic;<br/>{? CIRLWORD : IN std_logic_vector(4 downto 0);</pre> |                    |

|                                                          | <pre>f8 TBR : IN std logic vector (? downto 0);</pre>                                |                    |

|                                                          | 49 IRE: CUT std logic;<br>50 IERE: OUT std logic;                                    |                    |

|                                                          | Si TRO: OUI std abgic;                                                               |                    |

|                                                          | 52 );                                                                                |                    |

|                                                          | 53 END COMPONENT;<br>54                                                              |                    |

|                                                          | 55 Inputs                                                                            |                    |

|                                                          | 56 SIGNAL TRC : std_logic := '0';                                                    |                    |

|                                                          | 57 SIGNAL MR : std logic := '1';<br>58 SIGNAL TBRL : std logic := '0';               |                    |

|                                                          | SO                                                                                   | ~                  |

| Sim Hierarchy - uant_transmi                             |                                                                                      | 1                  |

|                                                          | 😰 Design Summary 🛛 🔯 Sinu/ation 🔹 uart_transmitter_tb.vhd                            |                    |

| • THE 1000 ns                                            |                                                                                      | ٨.                 |

| run 1000 ns                                              |                                                                                      |                    |

| 1000 113                                                 |                                                                                      | G                  |

|                                                          |                                                                                      |                    |

| Console CEnors Warnings Td Shel                          | 🙀 Find in Files 📲 Sim Console - uait_transmitter_tb_vhid                             |                    |

|                                                          |                                                                                      | S NUM SCRU VHOL    |

|                                                          |                                                                                      | 10 (1) 203 PM      |

| Ximr-SE-C                                                |                                                                                      | YEI LIK NVI 203 PM |

|                                                          | Project in ISE                                                                       |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

|                                                          |                                                                                      |                    |

## 1.2 VHDL CODE OF UART TRANSMITTER.

| <ul> <li>Company: Near East University</li> <li>Engineer: Nadeem Hassan</li> </ul> |

|------------------------------------------------------------------------------------|

|                                                                                    |

| <ul> <li>Create Date: 09:16:59 02/19/2008</li> <li>Design Name:</li> </ul>         |

| - Module Name: uart_transmitter - Behavioral                                       |

| <ul> <li>Project Name:</li> <li>Target Devices:</li> </ul>                         |

| - Tool versions:                                                                   |

| – Description:                                                                     |

| – Dependencies:                                                                    |

| - Revision:                                                                        |

| <ul> <li>Revision 0.01 - File Created</li> <li>Additional Comments:</li> </ul>     |

| _                                                                                  |

|                                                                                    |

| - UART Transmitter Model (behavior modeling)                                       |

| -                                                                                  |

| library ieee;                                                                      |

| use ieee.std_logic_1164.all;                                                       |

| package my_package is                                                              |

| EUNCTION perity/inpute: std_logie_vector(7 downto 0)) PETUPN std_logie:            |

| FUNCTION parity(inputs: std_logic_vector(7 downto 0)) RETURN std_logic;            |

| end my_package;                                                                    |

| PACKAGE body my_package is                                                         |

| FUNCTION parity(inputs: std_logic_vector(7 downto 0)) RETURN std_logic is          |

| variable temp: std_logic;                                                          |

| begin<br>temp:='0';                                                                |

| for i in 7 downto 0 loop                                                           |

| temp:=temp xor inputs(i);<br>end loop;                                             |

| return temp;                                                                       |

| end parity;                                                                        |

| end my_package;                                                                    |

|                                                                                    |

|                                                                                    |

brary ieee; se ieee.std\_logic\_1164.all; se ieee.std\_logic\_arith.all; se ieee.std\_logic\_unsigned.all; se work.my\_package.all;

entity trans is

po

| 1    |          |                                   |

|------|----------|-----------------------------------|

| ort( | TRC:     | in std_logic;                     |

|      | MR:      | in std_logic;                     |

|      | TBRL:    | in std_logic;                     |

|      | SFD:     | in std_logic;                     |

|      | CRL:     | in std_logic;                     |

|      | CTRLWORD | :in std_logic_vector(4 downto 0); |

|      | TBR:     | in std_logic_vector(7 downto 0);  |

|      | TRE:     | out std_logic;                    |

|      | TBRE:    | out std_logic;                    |

|      | TRO:     | out std_logic                     |

|      |          |                                   |

6

end trans;

chitecture behv of trans is

constant C0: unsigned(4 downto 0):="00001"; constant CI: unsigned(4 downto 0):="01000"; constant CM: unsigned(4 downto 0):="10000"; constant MM: unsigned(3 downto 0):="1111"; signal trans\_reg: std\_logic\_vector(11 downto 0); signal trans\_reg\_temp: std\_logic\_vector(11 downto 0); signal TBR\_sig: std\_logic\_vector(7 downto 0); signal old\_tbr\_sig: std\_logic\_vector(7 downto 0); signal delay: std\_logic\_vector(0 downto 0); signal go: std\_logic; signal t\_pari: std\_logic; signal clk: std\_logic; signal i: unsigned(3 downto 0); signal ctrl\_word: std\_logic\_vector(4 downto 0);

#### regin

| -PO: process(MR,TRC,i,TBR) |                                  | generate 16* clock |

|----------------------------|----------------------------------|--------------------|

| -begi                      | n                                |                    |

| -                          | if MR='1' then                   |                    |

| -                          | i<="00000";                      |                    |

| -                          | elsif TRC='1' and TRC'event then |                    |

| -                          | i<=i+C0;                         |                    |

| ~                          | if i=CI then                     |                    |

| -                          | clk<='1';                        |                    |

| -                          | elsif i=CM then                  |                    |

| -                          | i<="00000";                      |                    |

| ~                          | clk<='0';                        |                    |

| -                          | end if;                          |                    |

|                            |                                  |                    |

```

end if;

- d process;

-- load control word here

begin

if CRL='1' then

ctrl_word<=CTRLWORD;

end if;

end process;

- this process make out the transmit register according to control word.

process(clk,ctrl_word,MR,TBR,TBRL,TBR_sig,t_pari)

regin

if (MR='1') then

TBR_sig<="111111111";

t_{pari} \le '0';

trans_reg_temp <= "1111" & TBR_sig;</pre>

else

if TBRL='0' then

TBR_sig <= TBR;

t_pari <= parity(TBR); -- call function and compute the parity

end if;

case ctrl_word is

when "00000" | "00001" =>

if t_pari='0' then

-- odd parity

trans_reg_temp <= "111" & "11" & '1' & TBR_sig(4 downto 0) & '0';

elsif t_pari='1' then

-- even parity

trans_reg_temp <= "111" & "11" & '0' & TBR_sig(4 downto 0) & '0';

end if;

when "00010"|"00011" =>

if t_pari='0' then

-- odd parity

trans reg temp \leq = "111" \& "11" \& '0' \& TBR_sig(4 downto 0) \& '0';

elsif t_pari='1' then

-- even parity

trans_reg_temp <= "111" & "11" & '1' & TBR_sig(4 downto 0) & '0';

end if;

when "00100" | "00110" | "00101" | "00111" => -- no parity

trans reg temp \leq  "1111" & "11" & TBR sig(4 downto 0) & '0';

when "01000" | "01001" =>

if t_pari='0' then

-- odd parity

trans_reg_temp <= "11" & "11" & '1' & TBR_sig(5 downto 0) & '0';

elsif t_pari='1' then

-- even parity

trans_reg_temp <= "11" & "11" & '0' & TBR_sig(5 downto 0) & '0';

end if;

when "01010"|"01011" =>

-- odd parity

if t_pari='0' then

trans_reg_temp <= "11" & "11" & '0' & TBR_sig(5 downto 0) & '0';

```

```

-- even parity

elsif t pari='1' then

trans_reg_temp <= "11" & "11" & '1' & TBR_sig(5 downto 0) & '0';

end if:

when "01100"|"01110"|"01101"|"01111" =>

-- no parity

trans_reg_temp <= "111" & "11" & TBR_sig(5 downto 0) & '0';

when "10000"|"10001" =>

-- odd parity

if t_pari='0' then

trans_reg_temp <= '1' & "11" & '1' & TBR_sig(6 downto 0) & '0';

-- even parity

elsif t pari='1' then

trans_reg_temp <= '1' & "11" & '0' & TBR_sig(6 downto 0) & '0';

end if;

when "10010"|"10011" =>

if t_pari='0' then

-- odd parity

trans_reg_temp <= '1' & "11" & '0' & TBR_sig(6 downto 0) & '0';

-- even parity

elsif t pari='1' then

trans_reg_temp <= '1' & "11" & '1' & TBR_sig(6 downto 0) & '0';

end if:

when "10100"|"10110"|"10101"|"10111" =>

-- no parity

trans_reg_temp <= "11" & "11" & TBR_sig(6 downto 0) & '0';

when "11000" | "11001" =>

-- odd parity

if t pari='0' then

trans_reg_temp <= "11" & '1' & TBR_sig(7 downto 0) & '0';

-- even parity

elsif t_pari='1' then

trans_reg_temp <= "11" & '0' & TBR_sig(7 downto 0) & '0';

end if;

when "11010" |"11011" =>

-- odd parity

if t_pari='0' then

trans_reg_temp <= "11" & '0' & TBR_sig(7 downto 0) & '0';

-- even parity

elsif t_pari='1' then

trans_reg_temp <= "11" & '1' & TBR_sig(7 downto 0) & '0';

end if;

-- no parity

when others =>

trans_reg_temp <= '1' & "11" & TBR_sig(7 downto 0) & '0';

end case;

end if:

end process;

- P3 describes the whole transmission procedure

P3: process

variable cnt: integer range 0 to 12;

variable cnt limit: integer range 0 to 12;

begin

wait until TRC'event and TRC='1';

if MR='1' then

old_tbr_sig <= "111111111";

delay<="0";

go<='0';

```

```

20

```

```

i <= "0000";

else

if (i=MM) then

i<="0000";

if(go='0') then

delay<="0";

cnt := 12;

TRE <= '1':

if (old_tbr_sig=TBR_sig) then

go <= '0';

elsif (old_tbr_sig/=TBR_sig) then

go <='1';

end if;

trans_reg <= "1111111111111";

elsif (go='1' and delay="0") then

go<='1';

cnt:=0;

delay<=delay+1;

TRE <= '1';

trans_reg <= "1111111111111";

elsif (go='1' and delay="1" and cnt=0) then

go <= '1';

cnt:=cnt+1;

delay<=delay+0;

old_tbr_sig<=TBR_sig;

TRE<='0';

trans_reg <= trans_reg_temp;</pre>

elsif (go='1' and delay="1" and cnt/=0) then

trans_reg <= '1' & trans_reg(11 downto 1);

case ctrl_word(4 downto 2) is

when "000" =>

if ctrl_word(0)='0' then

cnt\_limit := 8;

elsif ctrl word(0)='1' then

cnt_limit :=9;

end if;

when "001" =>

if ctrl word(0)='0' then

cnt\_limit := 7;

elsif ctrl_word(0)='1' then

cnt_limit :=8;

end if;

when "010" =>

if ctrl_word(0)=0' then

cnt\_limit := 9;

elsif ctrl_word(0)='1' then

cnt_limit :=10;

end if:

when "011" =>

if ctrl_word(0)=0' then

cnt\_limit := 8;

elsif ctrl_word(0)='1' then

cnt_limit :=9;

end if;

when "100" =>

if ctrl_word(0)='0' then

```

```

cnt limit := 10;

elsif ctrl_word(0)='1' then

cnt_limit :=11;

end if:

when "101" =>

if ctrl_word(0)='0' then

cnt_limit := 9;

elsif ctrl_word(0)='1' then

cnt_limit :=10;

end if;

when "110" =>

if ctrl_word(0)='0' then

cnt_limit :=11;

elsif ctrl_word(0)='1' then

cnt_limit :=12;

end if;

when "111" =>

if ctrl_word(0)='0' then

cnt_limit :=10;

elsif ctrl_word(0)='1' then

cnt_limit :=11;

end if;

when others =>

end case;

if cnt/=cnt_limit then

go <= '1';

delay<=delay+0;

cnt:=cnt+1;

TRE<='0';

elsif cnt=cnt_limit then

go <= '0';

delay<="0";

TRE<='1';

end if;

end if;

if SFD='1' then

TBRE <= 'Z';

elsif SFD='0' then

if (cnt=0 or cnt=1) then

TBRE <= '0';

else

TBRE <= '1';

end if;

end if;

else

i<=i+1;

end if;

end if;

```

end process;

-- this cocurrent statement handles the serial output of Transmitter tro <= trans\_reg(0);</p>

end behv;

<< .....>>>

#### 1.3 SYNTHESIS

I use the Xilinx-ISE- 'synthesis tool' to synthesize the code.

The synthesis Report goes as follows

- Synthesis Options Summary

- HDL Compilation

- Design Hierarchy Analysis

- HDL Analysis

- HDL Synthesis

- Advanced HDL Synthesis

- Low Level Synthesis

- Partition Report

- Final Report

The synthesize result is shown below:

Release 9.1.02i - xst J.32 Copyright (c) 1995-2007 Xilinx, Inc. All rights reserved. --> Parameter TMPDIR set to ./xst/projnav.tmp CPU : 0.00 / 1.73 s | Elapsed : 0.00 / 2.00 s

--> Parameter xsthdpdir set to ./xst CPU : 0.00 / 1.73 s | Elapsed : 0.00 / 2.00 s

--> Reading design: trans.prj

- TABLE OF CONTENTS

- 1) Synthesis Options Summary

- 2) HDL Compilation

- 3) Design Hierarchy Analysis

- 4) HDL Analysis

5) HDL Synthesis 5.1) HDL Synthesis Report 6) Advanced HDL Synthesis 6.1) Advanced HDL Synthesis Report 7) Low Level Synthesis 8) Partition Report 9) Final Report 9.1) Device utilization summary 9.2) Partition Resource Summary 9.3) TIMING REPORT Synthesis Options Summary \* ====== ---- Source Parameters Input File Name : "trans.prj" Input Format : mixed Ignore Synthesis Constraint File : NO ---- Target Parameters Output File Name : "trans" Output Format : NGC Target Device : xc3s500e-5-fg320 ---- Source Options Top Module Name : trans Automatic FSM Extraction : YES . : Auto FSM Encoding Algorithm Safe Implementation : No FSM Style : lut **RAM** Extraction : Yes RAM Style : Auto **ROM** Extraction : Yes Mux Style : Auto Decoder Extraction : YES Priority Encoder Extraction : YES : YES Shift Register Extraction Logical Shifter Extraction : YES XOR Collapsing : YES **ROM Style** : Auto Mux Extraction : YES **Resource Sharing** : YES Asynchronous To Synchronous : NO Multiplier Style : auto Automatic Register Balancing : No ---- Target Options Add IO Buffers : YES

Global Maximum Fanout : 500 Add Generic Clock Buffer(BUFG) :24 **Register Duplication** : YES Slice Packing : YES Optimize Instantiated Primitives : NO Use Clock Enable : Yes Use Synchronous Set : Yes Use Synchronous Reset : Yes Pack IO Registers into IOBs : auto Equivalent register Removal : YES

| General Options               |                |

|-------------------------------|----------------|

| Optimization Goal             | : Speed        |

| Optimization Effort           | : 1            |

| Library Search Order          | : trans.lso    |

| Keep Hierarchy                | : NO           |

| RTL Output                    | : Yes          |

| <b>Global Optimization</b>    | : AllClockNets |

| Read Cores                    | : YES          |

| Write Timing Constraints      | : NO           |

| Cross Clock Analysis          | : NO           |

| Hierarchy Separator           | :/             |

| Bus Delimiter                 | : <>           |

| Case Specifier                | : maintain     |

| Slice Utilization Ratio       | : 100          |

| <b>BRAM</b> Utilization Ratio | : 100          |

| Verilog 2001                  | : YES          |

| Auto BRAM Packing             | : NO           |

| Slice Utilization Ratio Del   | ta : 5         |

|                               |                |

#### HDL Compilation

=====

=====

\_\_\_\_\_

Compiling vhdl file "C:/Xilinx91i/xilinx/myprojects/uart\_transmitter/uart\_transmitter.vhd" in Library work.

\*

\*

Package <my\_package> compiled.

Package body <my\_package> compiled.

Entity <trans> compiled.

Entity <trans> (Architecture <behv>) compiled.

\_\_\_\_\_

×

Design Hierarchy Analysis

\_\_\_\_\_\_ ======

calyzing hierarchy for entity <trans> in library <work> (architecture <behv>).

HDL Analysis

\*

Ilyzing Entity <trans> in library <work> (Architecture <behv>).

Ity <trans> analyzed. Unit <trans> generated.

HDL Synthesis

\*

HDL Synthesis

\*

Inthesizing Unit <trans>.

Related source file is

C:/Xilinx91i/xilinx/myprojects/uart\_transmitter/uart\_transmitter.vhd".

ARNING:Xst:1780 - Signal <clk> is never used or assigned.

ARNING:Xst:737 - Found 8-bit latch for signal <TBR\_sig>.

ARNING:Xst:737 - Found 1-bit latch for signal <t\_pari>.

ARNING:Xst:737 - Found 5-bit latch for signal <ctrl\_word>.

ARNING:Xst - Property "use\_dsp48" is not applicable for this technology.

Found 1-bit register for signal <TRE>.

Found 1-bit tristate buffer for signal <TBRE>.

Found 4-bit register for signal <cnt>.

Found 4-bit adder for signal <cnt\$add0000> created at line 272.

Found 4-bit comparator equal for signal <cnt\$cmp\_eq0001> created at line 269.

Found 4-bit comparator not equal for signal <cnt\$cmp\_ne0000> created at line 269.

Found 4-bit 8-to-1 multiplexer for signal <cnt\_limit\$mux0001> created at line 225.

Found 1-bit register for signal <delay<0>>.

Found 1-bit register for signal <go>.

Found 8-bit comparator equal for signal <go\$cmp\_eq0001> created at line 204.

Found 4-bit up counter for signal <i>.

Found 1-bit register for signal <Mtridata\_TBRE> created at line 282.

Found 1-bit register for signal <Mtrien\_TBRE> created at line 282.

Found 8-bit register for signal <old\_tbr\_sig>.

Found 1-bit xor8 for signal <t\_pari\$xor0001> created at line 41.

Found 12-bit register for signal <trans\_reg>.

Summary:

inferred 1 Counter(s).

inferred 29 D-type flip-flop(s).

inferred 1 Adder/Subtractor(s).

inferred 3 Comparator(s).

inferred 4 Multiplexer(s).

inferred 1 Xor(s).

inferred 1 Tristate(s). Unit <trans> synthesized.

#### \_\_\_\_\_

HDL Synthesis Report

| Macro Statistics                        |           |   |          |

|-----------------------------------------|-----------|---|----------|

| # Adders/Subtractors                    | : 1       |   |          |

| 4-bit adder                             | : 1       |   |          |

| # Counters                              | : 1       |   |          |

| 4-bit up counter                        | : 1       |   |          |

| # Registers                             | : 8       |   |          |

| 1-bit register                          | : 5       |   |          |

| 12-bit register                         | : 1       |   |          |

| 4-bit register                          | : 1       |   |          |

| 8-bit register                          | : 1       |   |          |

| # Latches                               | : 3       |   |          |

| 1-bit latch                             | : 1       |   |          |

| 5-bit latch                             | : 1       |   |          |

| 8-bit latch                             | : 1       |   |          |

| # Comparators                           | : 3       |   |          |

| 4-bit comparator equal                  | : 1       |   |          |

| 4-bit comparator not equal              | : 1       |   |          |

| 8-bit comparator equal                  | : 1       |   |          |

| # Multiplexers                          | : 1       |   |          |

| 4-bit 8-to-1 multiplexer                | : 1       |   |          |

| # Tristates                             | : 1       |   |          |

| 1-bit tristate buffer                   | : 1       |   |          |

| # Xors                                  | :1        |   |          |

| 1-bit xor8                              | : 1       |   |          |

|                                         |           |   |          |

| ======================================= |           |   | <br>==== |

| =====                                   |           |   |          |

|                                         |           |   |          |

|                                         | *         |   |          |

| * Advanced HDI                          | Sunthesis | * |          |

|                                         |           |   | <br>     |

|                                         |           | 8 |          |

|                                         |           |   |          |

| T 1' 1 ' C 1' '                         |           |   | <br>     |

Loading device for application Rf\_Device from file '3s500e.nph' in environment C:\Xilinx91i.

Advanced HDL Synthesis Report

Macro Statistics # Adders/Subtractors 4-bit adder

:1 :1

| # Counters                 | : 1  |

|----------------------------|------|

| 4-bit up counter           | : 1  |

| # Registers                | : 29 |

| Flip-Flops                 | : 29 |

| # Latches                  | : 3  |

| 1-bit latch                | : 1  |

| 5-bit latch                | : 1  |

| 8-bit latch                | : 1  |

| # Comparators              | : 3  |

| 4-bit comparator equal     | : 1  |

| 4-bit comparator not equal | : 1  |

| 8-bit comparator equal     | : 1  |

| # Multiplexers             | : 1  |

| 4-bit 8-to-1 multiplexer   | : 1  |

| # Xors                     | : 1  |

| 1-bit xor8                 | : 1  |

|                            |      |

#### ======

Low Level Synthesis

\*

Optimizing unit <trans> ...

WARNING:Xst:1710 - FF/Latch <trans\_reg\_11> (without init value) has a constant value of

1 in block <trans>.

WARNING:Xst:1710 - FF/Latch <trans\_reg\_10> (without init value) has a constant value of

1 in block <trans>.

WARNING:Xst:1710 - FF/Latch <trans\_reg\_10> (without init value) has a constant value of

1 in block <trans>.

WARNING:Xst:1710 - FF/Latch <trans\_reg\_10> (without init value) has a constant value of

1 in block <trans>.

WARNING:Xst:1710 - FF/Latch <trans\_reg\_10> (without init value) has a constant value of

1 in block <trans>.

Mapping all equations... Building and optimizing final netlist ... Found area constraint ratio of 100 (+ 5) on block trans, actual ratio is 1.

Final Macro Processing ...

#### ======

Final Register Report

| Macro Statistics |      |

|------------------|------|

| # Registers      | : 31 |

| Flip-Flops       | : 31 |

| ======================================= |                |             |   |             |  |

|-----------------------------------------|----------------|-------------|---|-------------|--|

|                                         |                |             |   |             |  |

|                                         |                |             |   |             |  |

|                                         |                |             |   |             |  |

|                                         |                |             |   |             |  |

|                                         |                |             |   |             |  |

|                                         | ========       |             |   | =========== |  |

| ======                                  |                |             |   |             |  |

| * Partitio                              | on Report      |             | * |             |  |

| ======================================= |                |             |   |             |  |

| ======                                  |                |             |   |             |  |

|                                         |                |             |   |             |  |

| Partition Implementation                | n Status       |             |   |             |  |

| 1                                       |                |             |   |             |  |

|                                         |                |             |   |             |  |

| No Partitions were four                 | nd in this des | sign.       |   |             |  |

|                                         |                | 0           |   |             |  |

|                                         |                |             |   |             |  |

|                                         |                |             |   |             |  |

|                                         |                |             |   |             |  |

|                                         |                |             |   |             |  |

| * Final                                 | Report         |             | * |             |  |

|                                         | ============   |             |   |             |  |

|                                         |                |             |   |             |  |

| Final Results                           |                |             |   |             |  |

| RTL Top Level Output I                  | File Name      | · trans nor |   |             |  |

| Top Level Output File N                 |                |             |   |             |  |

|                                         | : NGC          | 14115       |   |             |  |

| Optimization Goal                       |                | 4           |   |             |  |

|                                         |                | u           |   |             |  |

| Keep Hierarchy                          | : NO           |             |   |             |  |

| Destau Cretistics                       |                |             |   |             |  |

| Design Statistics                       | 01             |             |   |             |  |

| # IOs                                   | : 21           |             |   |             |  |

|                                         |                |             |   |             |  |

| Cell Usage :                            | 0.6            |             |   |             |  |

| # BELS                                  | : 96           |             |   |             |  |

| # INV                                   | : 1            |             |   |             |  |

| # LUT2                                  | : 8            | •           |   |             |  |

| # LUT2_D                                | : 1            |             |   |             |  |

| # LUT3                                  | : 15           |             |   |             |  |

| # LUT3_D                                | :1             |             | 2 |             |  |

| # LUT4                                  | : 51           |             |   |             |  |

| # LUT4_D                                | : 5            |             |   |             |  |

| # LUT4_L                                | : 8            |             |   |             |  |

| # MUXF5                                 | : 6            |             |   |             |  |

| # FlipFlops/Latches                     | : 45           |             |   |             |  |

| # FDE                                   | : 13           |             |   |             |  |

| # FDR                                   | : 4            |             |   |             |  |

| # FDRE                                  | : 6            |             |   |             |  |

| # FDSE                                  | : 8            |             |   |             |  |

|                                         |                |             |   |             |  |

| LD       : 5         LDC_1       : 1         LDP_1       : 8         Clock Buffers       : 3         BUFGP       : 3         IO Buffers       : 1         IBUF       : 15         OBUF       : 2         OBUFT       : 1 | 8                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                          |                                                                                                                                                                       |

| Device utilization summary:                                                                                                                                                                                              |                                                                                                                                                                       |

| Selected Device : 3s500efg32                                                                                                                                                                                             | :0-5                                                                                                                                                                  |

| Number of Slices:<br>Number of Slice Flip Flops:<br>Number of 4 input LUTs:<br>Number of IOs:<br>Number of bonded IOBs:<br>IOB Flip Flops:<br>Number of GCLKs:                                                           | <ul> <li>49 out of 4656 1%</li> <li>40 out of 9312 0%</li> <li>90 out of 9312 0%</li> <li>21</li> <li>21 out of 232 9%</li> <li>5</li> <li>3 out of 24 12%</li> </ul> |

| Partition Resource Summary:<br>                                                                                                                                                                                          |                                                                                                                                                                       |

|                                                                                                                                                                                                                          | UMBERS ARE ONLY A SYNTHESIS ESTIMATE.<br>NG INFORMATION PLEASE REFER TO THE TRACE<br>PLACE-and-ROUTE.                                                                 |

| Clock Information:                                                                                                                                                                                                       |                                                                                                                                                                       |

|                                                                                                                                                                                                                          | ++                                                                                                                                                                    |

| Clock Signal                                                                                                                                                                                                             | Clock buffer(FF name)   Load  <br>++                                                                                                                                  |

|                                                                                                                                                                                                                          | JFGP  31  <br>UFGP  9  <br>30                                                                                                                                         |

|                                                                                                                                                                                                                          |                                                                                                                                                                       |

| CRL | BUFGP | 5 |

|-----|-------|---|

|     |       | + |

Asynchronous Control Signals Information:

|                |          |          | ++   |

|----------------|----------|----------|------|

| Control Signal | Buffer(F | FF name) | Load |

|                | ++       |          | ++   |

| MR             | IBUF     | 9        |      |

|                |          |          | ++   |

Timing Summary:

Speed Grade: -5

Minimum period: 5.686ns (Maximum Frequency: 175.858MHz) Minimum input arrival time before clock: 5.787ns Maximum output required time after clock: 4.040ns Maximum combinational path delay: No path found

Detail:

and values displayed in nanoseconds (ns)

| Clock period: 5.                                                                    | Example 2 Constraints for Clock 'TRC'<br>686ns (frequency: 175.858MHz)<br>9 paths / destination ports: 480 / 57 | == |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----|

| Source: i<br>Destination:<br>Source Clock:<br>Destination Cloc<br>Data Path: i_1 to | cnt_0 (FF)<br>TRC rising<br>ck: TRC rising                                                                      |    |

| FDR:C->Q<br>LUT4:I1->O<br>LUT2:I1->O<br>LUT4:I3->O<br>FDRE:R<br>Total               | 5 0.612 0.607 old_tbr_sig_not000111 (go_cmp_eq0000)<br>15 0.612 0.867 cnt_and000011 (trans reg_not0001)         |    |

| Total number of                                              | Default OFFSET IN BEFORE for Clock 'TRC'<br>paths / destination ports: 67 / 50                                                                                                                                                                                                                                                                                                                     | ==== |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Offset: 5.7<br>Source: S<br>Destination:<br>Destination Cloc | ent_2 (FF)                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Data Path: SFD<br>Cell:in->out                               | o cnt_2<br>Gate Net<br>fanout Delay Delay Logical Name (Net Name)                                                                                                                                                                                                                                                                                                                                  |      |

| LUT4:I3->0<br>LUT4:I1->0<br>LUT4:I3->0<br>LUT4:I3->0         | 11       1.106       0.796       SFD_IBUF (SFD_IBUF)         1       0.612       0.426       cnt_cmp_ne0000199_SW0_SW0 (N626)         2       0.612       0.383       cnt_cmp_ne0000199_SW0 (N606)         1       0.612       0.360       cnt_mux0001<1>29 (cnt_mux0001<1>_map10)         1       0.612       0.000       cnt_mux0001<1>65 (cnt_mux0001<1>)         0.268       cnt_2       cnt_2 | )    |

| ======================================                       | <ul> <li>5.787ns (3.822ns logic, 1.965ns route)<br/>(66.0% logic, 34.0% route)</li> <li>: Default OFFSET IN BEFORE for Clock 'TBRL'</li> </ul>                                                                                                                                                                                                                                                     |      |

| Total number of<br>Offset: 3.<br>Source: 7                   | paths / destination ports: 16 / 9<br>639ns (Levels of Logic = 3)<br>BR<3> (PAD)<br>t_pari (LATCH)<br>ck: TBRL rising                                                                                                                                                                                                                                                                               |      |

| LUT4:I0->O                                                   | 2 1.106 0.532 TBR_3_IBUF (TBR_3_IBUF)<br>1 0.612 0.509 t_pari_xor000112 (t_pari_xor0001_map6)<br>1 0.612 0.000 t_pari_xor000126 (t_pari_xor0001)<br>0.268 t_pari                                                                                                                                                                                                                                   |      |

| Total                                                        | 3.639ns (2.598ns logic, 1.041ns route)<br>(71.4% logic, 28.6% route)                                                                                                                                                                                                                                                                                                                               |      |

Timing constraint: Default OFFSET IN BEFORE for Clock 'CRL' Total number of paths / destination ports: 5 / 5

\_\_\_\_

| Offset:1.731ns (Levels of Logic = 1)Source:CTRLWORD<0> (PAD)Destination:ctrl_word_0 (LATCH)Destination Clock:CRL falling                   |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| Data Path: CTRLWORD<0> to ctrl_word_0<br>Gate Net<br>Cell:in->out fanout Delay Delay Logical Name (Net Name)                               |

| IBUF:I->O         1         1.106         0.357         CTRLWORD_0_IBUF (CTRLWORD_0_IBUF)           LD:D         0.268         ctrl_word_0 |

| Total         1.731ns (1.374ns logic, 0.357ns route)<br>(79.4% logic, 20.6% route)                                                         |

| Total number of paths / destination ports: 4 / 3                                                                                           |

| Offset:4.040ns (Levels of Logic = 1)Source:TRE (FF)Destination:TRE (PAD)Source Clock:TRC rising                                            |

| Path: TRE to TRE<br>Gate Net<br>Cell:in->out fanout Delay Delay Logical Name (Net Name)                                                    |

| FDE:C->Q         1         0.514         0.357         TRE (TRE_OBUF)           OBUF:I->O         3.169         TRE_OBUF (TRE)             |

| 4.040ns (3.683ns logic, 0.357ns route)<br>(91.2% logic, 8.8% route)                                                                        |

| CRC : 17.72 / 19.72 s   Elapsed : 18.00 / 20.00 s                                                                                          |

|                                                                                                                                            |

| memory usage is 160540 kilobytes                                                                                                           |

| <pre>deferrors : 0 ( 0 filtered)</pre>                                                                                                     |

| <<>>                                                                                                                                       |

|                                                                                                                                            |

Xilinx synthesis tool created the following design. Top level block diagram.

Block Diagram

# 1.4 Writing Test Bench.

In the test bench generated 160 MHz. I wrote in the data in to the UART Transmitter and read **t** back to verify data can be written and read correctly. The simulation result is shown below.

| BMM File<br>IP (Coregen & Architecture Wizard)<br>MEM File<br>Schematic<br>Implementation Constraints File<br>State Diagram | File name:              |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|

| ▲ Test Bench WaveForm<br>■ User Document                                                                                    | uart_transmitter_tb.vhd |  |  |  |  |