# NEAR EAST UNIVERSITY

# **Faculty of Engineering**

### **Department of Computer Engineering**

### SIXTY COUNTER

Graduation Project COM-400

Student : Hakan Şahin(20033641)

Supervisor : Mehmet Kadir Özakman

Nicosia-2008

### ACKNOWLEDGEMENTS

"First, I would like to thank my supervisor Mehmet Kadir Özakman for his Invaluable advice and belief in my work and myself over the course of this Graduation Project..

Second, I would like to Express my gratitude to Near East University for the scholarship that made the work possible.

Third, I thank my family for their constant encouragement and support during the preparation of this project.

Finally, I would also like to thank all my friends for their advice and support."

in.

#### ABSTRACT

We will design sixty counter in this project . Sixty counter is an electronic desgin. We are using sixty counter in different areas as digital watch .

The xilinx ise 9.1i software will be used for to create the sixty counter design. We have selected this program because is very useful for to do this elecronic design. We can design many things that we want using xilinx ise software.

We will explain briefly why xilinx ise software is useful and suitable for us. Assume that you have a company you are working IT(information technology) sector . You can do many specific solutions , one day if you need a 32 bit processor for example. You are calling xilinx company and then you are saying 'we want a 32 bit processor'. Then they are sending a spesific FPGA (field programmable logic gate)chip kit(virtex,spartan etc..) as special for your request . Then you are taking the kit and connecting the internet at where you are . They are loading a 32 bit processor software your kit using the internet . So you have a 32 bit processor.

It's very useful for the companies because if you want you can change your proccessor to ram or rom etc.. You can convert so many things . If you have a kit on your hand you can create many things using this kit and xilinx software.

So we hope this technology will grow up and there will be so many vacany therefore we want to learn this technology and we used this software.

### TABLE OF CONTENTS

|                                              | ÷     |

|----------------------------------------------|-------|

| ACKNOWLEDGMENT                               | İ<br> |

| ABSTRACT                                     | İİ    |

| TABLE OF CONTENTS                            | İİİ   |

| LIST OF ABBREVIATIONS                        | İV    |

| INTRODUCTION                                 | 1     |

| CHAPTER ONE : DESIGN                         | 3     |

| 1.1)DESIGN DECRIPTION                        | 3     |

| 1.2) 1.2)ABOUT THE DESIGN                    | 5     |

| CHAPTER TWO : DESIGN STEPS                   | 7     |

| 2.1)ENTER THE DESIGN                         | 7     |

| 2.2)CREATING a VHDL SOURCE                   | 8     |

| 2.3)GENERATING a CODE                        | 11    |

| 2.4)SYNTHESİZE                               | 17    |

| 2.5)WRITING a TEST BENCH                     | 30    |

| 2.6)SIMULATING                               | 34    |

| 2.7) EXPLANATION OF MY SIXTY COUNTER PROGRAM | 36    |

| CODES                                        |       |

| CHAPTER THREE :SPARTAN                       | 40    |

| 3.1)OVERVIEW                                 | 40    |

| 3.2)CAPABILITIES                             | 41    |

| 3.2.1)DUAL POWER MANAGEMENT                  | 41    |

| 3.2.2)MULTIPLE LEVELS OF SECURITY            | 42    |

| 3.2.3)INTEGRATED FLASH MEMORY                | 42    |

| 3.2.4)XtremeDSP DSP 48A SLICE                | 43    |

| 3.2.5) EMBEDDED PROCESSING                   | 43    |

|     | 3.2.6)FOUR LEVEL MEMORY ARCHITECTURE                                | 44 |

|-----|---------------------------------------------------------------------|----|

|     | 3.2.7) LEADING CONNECTIVITY PLATFORM                                | 45 |

|     | 3.2.8)CONFIGURABLE LOGIC BLOCKS                                     | 46 |

|     | 3.2.9)PRECISE CLOCK MANAGEMENT RESOURCES                            | 46 |

|     | 3.2.10) COMPREHENSIVE CONFIGURATION                                 | 46 |

|     | CAPABILITIES                                                        |    |

|     | 3.3)ADVANTAGES                                                      | 47 |

| CHA | PTER FOUR:HISTORY                                                   | 50 |

|     | 4.1) WHAT DOES XILINX MEAN ?                                        | 50 |

|     | 4.2) WHAT DOES XILINX NAME REPRESENT?                               | 50 |

|     | 4.3)HOW XILINX BEGAN ?                                              | 53 |

|     | 4.3.1)NEV TECHNOLOGY                                                | 53 |

|     | 4.3.2)EFFECTIVE PARTNERSHIPS                                        | 54 |

|     | 4.3.3)INSPIRED EMPLOYEES                                            | 54 |

| •   | 4.4)BUSINESS                                                        | 55 |

|     | 4.4.1)LEARN ABOUT THE XILINX TECHNOLOGY,HOW and WHY TO PURPOSE IT ? | 55 |

|     | 4.4.2)PROGRAMMABLE LOGIC IS XİLİNX'S BUSINESS                       | 55 |

|     | 4.4.3) USES FOR PROGRAMMABLE LOGIC                                  | 56 |

| 4.4.4) MULTIPLE PRODUCT LINES WITH      | 56 |

|-----------------------------------------|----|

| SUPERLATIVE SOFTWARE SUPPORT            |    |

| 4.4.5)HIGH-PROFILE WORLDWIDE CUSTOMER   | 56 |

| and PARTNER BASE                        |    |

| 4.4.6)XILINX'S VISION FOR THE FUTURE    | 57 |

| 4.5)GETTIN STARTED WITH FPGAs           | 57 |

| 4.5.1) WHAT ARE FPGAs?                  | 57 |

| 4.5.2)COMMON FPGA FEATURES              | 59 |

| 4.5.3) FPGA SOLUTIONS, APPLICATIONS and | 60 |

| END- MARKETS                            |    |

| 4.6)XILINX's SUCCEES                    | 62 |

| 4.6.1)THE SYNERGY OF TECHNOLOGY,        | 62 |

| PARTNERSHIP, and LEADERSHIP             |    |

| 4.6.2)XILINX's PARTNERS                 | 62 |

| 4.6.3)XILINX's TECHNOLOGY               | 63 |

| 4.6.4)XILINX's EMPLOYEES                | 63 |

| 4.7)XILINX's VALUES                     | 64 |

| 4.7.1)HOW XILINX WORK WITH ONE          | 64 |

| ANOTHER AND XILINX'S PARTNERS,          |    |

| WHAT DO VALUES MEAN TO XILINX?          |    |

| 4.7.2)HOW DID XILINX CLEARLY DEFINE  | 64 |

|--------------------------------------|----|

| IT's VALUES ?                        |    |

| 4.7.3)HOW DO XILINX KEEP IT's VALUES | 65 |

| VISIBLE and VIABLE IN THE COMPANY ?  |    |

| CONCLUSION                           | 67 |

| REFERENCES                           | 69 |

di,

21

1

.

# LIST OF ABBREVIATIONS

| ISE  | Integrated Software Environment                                  |

|------|------------------------------------------------------------------|

| FPGA | Field Programmable Gate Array                                    |

| VHDL | Very high speed integrated circuit Hardware Description Language |

| DCM  | Digital Clock Manager                                            |

| RPM  | Relationally Placed Macro                                        |

| DUT  | Design Under Test                                                |

| UUT  | Unit Under Test                                                  |

#### INTRODUCTION

About the project, we will create a sixty counter. Sixty counter is a counter and when we run it, it counts up to sixty.

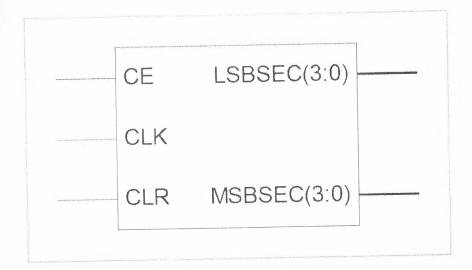

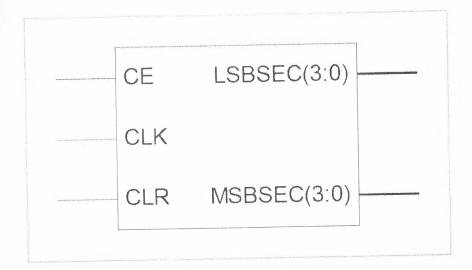

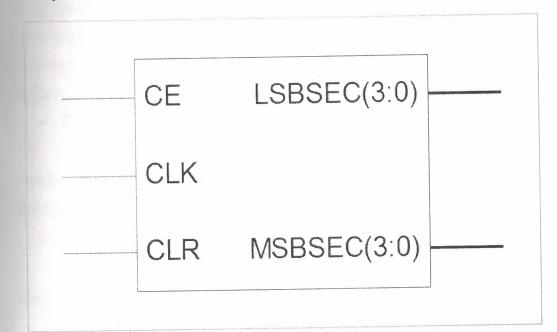

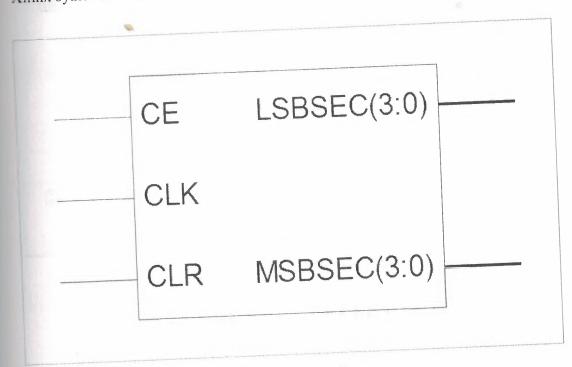

Block diagram of the Project looks like this .

.

#### Figure1. block diagram

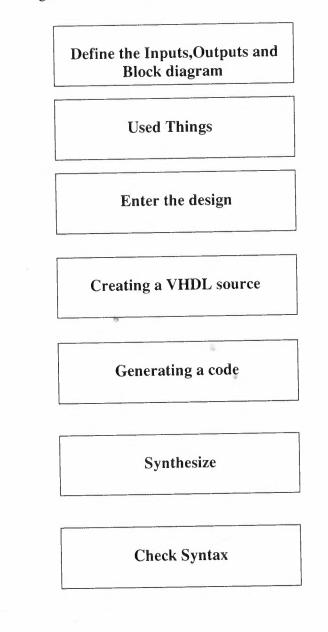

In the first chapter block diagram of the Project will be given and inputs and outputs from the block diagram will be defined. After that information about which language we used to create the project and what we used in software and hardware will be given. Then we will explain the Xilinx ISE 9.1. In this chapter lastly we will show the design flow .

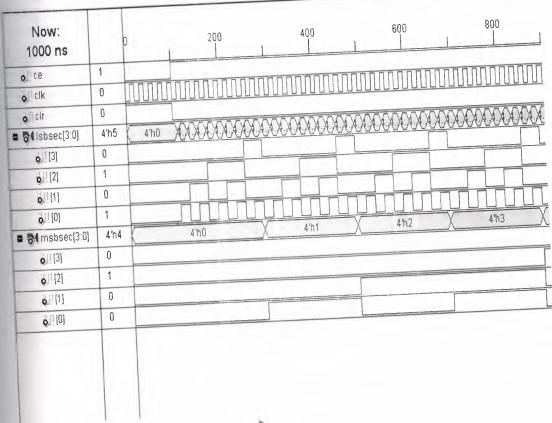

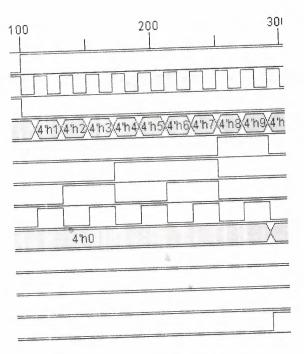

In the second chapter we will follow the steps which we gave at the end of chapter one . In the first step we will enter the design , the name of the project and directory of Project will be given by us .We will select a project device properties . Second step is creating a VHDL source . After creating a source we generate the codes . Then we check the generated codes from check syntax , to bu sure if we have mistakes or not . Then we create a test bench . After creating test bench we get simulation to see the output of the project . In this chapter lastly we will give an information about the project .

In chapter three an information will be given by us about the spartan. We will give an overview and capabilities and advantages of spartan.

In chapter four we will talk about xilinx . We will explain the mean of xilinx , and what the name of xilinx represents . In business what xilinx represents .

As you see last two chapter is general information about the xilinx and spartan. But the first two chapter is about the project.

## CHAPTER one DESIGN 1.1)DESIGN DECRIPTION

The design is sixty counter. We are going to do a Sixty counter which counts up to sixty.

#### Figure2. Sixty counter block diagram

Inputs :

CLK CLR CE

The counter counts the clock cycles . If the clock cycle is 1second conter will count up to 1minute . If the clock cycle is 1minute counter will count up to 60minute . Clear is clears all the values . Clock enable is enables counter to count .

Outputs :

LSBSEC

#### MSBSEC

Lsbsec is counts from 0 to 9. Msbsec is counts from 0-5.

**Used things :** To create the project VHDL programming language will be used and there will be a some hardware and software requirements . We will use in software Xilinx ISE and hardware Spartan3E.

The briefly explanation of Xilinx ISE : The Integrated Software Environment  $(ISE^{TM})$  is the Xilinx® design software suite that allows that , take the design from design entry through Xilinx device programming. The ISE Project Navigator manages and processes the designs through the following steps in the ISE design flow .

#### DESIGN ENTRY

Design entry is the first step in the ISE design flow. During design entry, we can create our source files based on design objectives. We can create your top-level design file using a Hardware Description Language (HDL), such as VHDL, Verilog, or ABEL, or using a schematic. We can use multiple formats for the lower-level source files in the design.

#### SYNTHESIS

After design entry and optional simulation, we run synthesis. During this step, VHDL, Verilog, or mixed language designs become netlist files that are accepted as input to the implementation step.

#### CREATE TEST BENCH

The results of the works during all the program is displayed in this process. Also in this process some values is given to get the outputs.

#### IMPLEMENTATION

After synthesis, we run design implementation, which converts the logical design into a physical file format that can be downloaded to the selected target device. From Project Navigator, we can run the implementation process in one step, or we can run each of the implementation processes separately. Implementation processes vary depending on whether we are targeting a Field Programmable Gate Array (FPGA) or a Complex Programmable Logic Device (CPLD).

#### VERİFİCATİON

We can verify the functionality of our design at several points in the design flow. We can use simulator software to verify the functionality and timing of our design or a portion of our design. The simulator interprets VHDL or Verilog code into circuit functionality and displays logical results of the described HDL to determine correct circuit operation. Simulation allows us to create and verify complex functions in a relatively small amount of time. We can also run in-circuit verification after programming our device.

### DEVICE CONFIGURATION

After generating a programming file, we configure our device. During configuration, we generate configuration files and download the programming files from a host computer to a Xilinx device.

#### **1.2)ABOUT THE DESIGN**

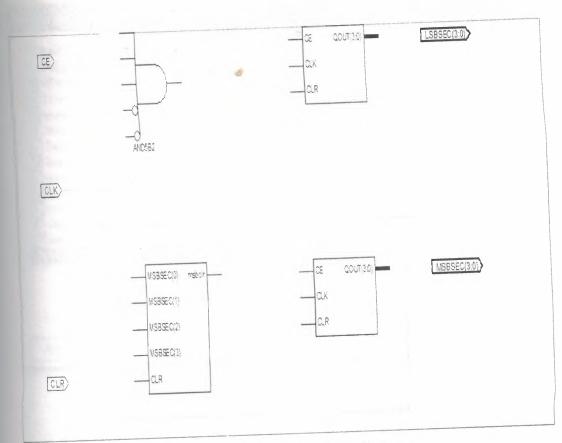

In this project we we have created a count sixty counter . This counter will count up to sixty . To create the counter we need two counter and the counters will work together . First counter will count from 0-9 and when the first counter comes nine it will add one to the second counter . By this way first counter will count the six times and the counter will reach the sixty .

Sixty counter can be used in digital watch .

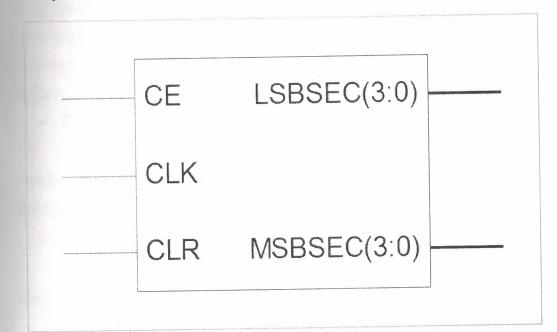

The design flow lookslike this :

## Creating a test bench

### Simulating

Explaining project

Figure3. design flow

# CHAPTER two DESIGN STEPS 2.1)ENTER THE DESIGN

In the first step we will create the Project basically. To do this firstly we must setup the XİLİNX ISE 9.11. After the installation of the program we open the program and then we have some steps to create the program as follows :

1. Select File > New Project... The New Project Wizard appears.

2. Type SİXTY in the Project Name field.

3. Enter or browse to a location (directory path) for the new project. The works subdirectory is created automatically.

| Enter a Name and Location fo<br>Project Name:<br>sixty |                        | Project Location<br>C:\Xilinx91i\myproject\sixty                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|--------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                                        |                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| Select the Type of Top-Leve                            | Source for the Project |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| Top-Level Source Type:                                 |                        | and a second second second second second second second second second second second second second second second | (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) (0,) | ~                 |

| HDL                                                    |                        |                                                                                                                | 10 F. T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | annau Shaannannan |

|                                                        |                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|                                                        |                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|                                                        |                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|                                                        |                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|                                                        |                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|                                                        |                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|                                                        |                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|                                                        |                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

#### Figure4.Project name

- 4. Verify that HDL is selected from the Top-Level Source Type list.

- 5. Click Next to move to the device properties page.

- 6. Fill in the properties in the table as shown below:

Product Category: All

Family: Spartan3E

Device: XC3S100E

Package: VQ100

Speed Grade: -5

Top-Level Source Type: HDL

Synthesis Tool: XST (VHDL/Verilog)

Simulator: ISE Simulator (VHDL/Verilog)

Preferred Language: VHDL

Verify that Enable Enhanced Design Summary is selected.

| Property Name                  | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                 |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Product Category               | All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                                                                                               |

| Family                         | Spartan3E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                 |

| Device                         | XC35100E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                 |

| Package                        | VQ100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                 |

| Speed                          | -5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                 |

| Top-Level Source Type          | НСЛ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | energi yanan sanadaran andaran angangan andalada<br>Tanan angan angangan ang kangangan angangan |

| Synthesis Tool                 | XST (VHDL/Verilog)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                 |

| Simulator                      | ISE Simulator (VHDL/Verilog)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                               |

| Preferred Language             | The state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the s |                                                                                                 |

| Enable Enhanced Design Summary | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                 |

| Enable Message Filtering       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                 |

| Display Incremental Messages   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                 |

Figure 5. Project Device Properties

Leave the default values in the remaining fields.

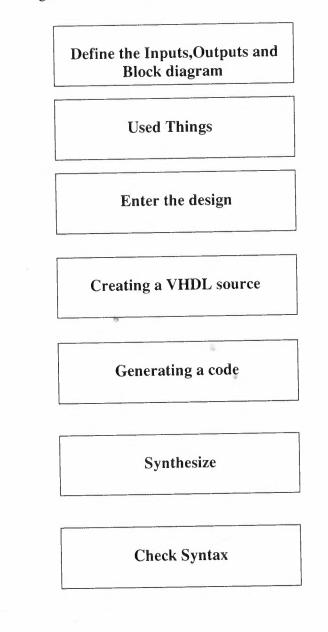

### 2.2) CREATING a VHDL SOURCE

Create a VHDL source file for the project as follows:

- 1. Click the New Source button in the New Project Wizard.

- 2. Select VHDL Module as the source type.

3. Type in the file name CNT60.

| BMM File<br>P (Coregen & Architecture Wizard)<br>MEM File<br>Schematic<br>Implementation Constraints File<br>State Diagram<br>Test Bench WaveForm<br>User Document<br>Verilog Module<br>Verilog Test Fixture<br>VHDL Module<br>VHDL Library<br>VHDL Package<br>VHDL Test Bench | File name:<br>cnt60<br>Location:<br>C: \Xilinx91 i\myproject\sixty |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                | Add to project                                                     |  |

Figure6.Adding source

4. Verify that the Add to project checkbox is selected.

5. Click Next.

6. Declare the ports for the counter design by filling in the port information as

shown below:

| Entity Name<br>rchitecture Name |           |                        |     | 2   |   |

|---------------------------------|-----------|------------------------|-----|-----|---|

| Port Name                       | Direction | Bus                    | MSB | LSB | A |

| CE                              | in        | · · □                  |     |     |   |

| CLK                             | in        | ¥ []                   | ÷   |     |   |

| CLR                             | in        | ~                      |     |     |   |

| SBSEC                           | out       | <ul> <li>✓ </li> </ul> | 2   | 3   | 0 |

| MSBSEC                          | out       | * 🗹                    |     | 3   | 0 |

|                                 | in        | ¥ 🗌                    |     |     |   |

|                                 | in        | ~                      |     |     |   |

|                                 | in        | ~                      |     |     |   |

|                                 | in        | ~ 🗌                    |     |     |   |

|                                 | in        | ¥ 🗌                    |     |     | V |

Figure7. Define Module

7. Click Next, then Finish in the New Source Wizard - Summary dialog box to complete the new source file template.

8. Click Next, then Next, then Finish.

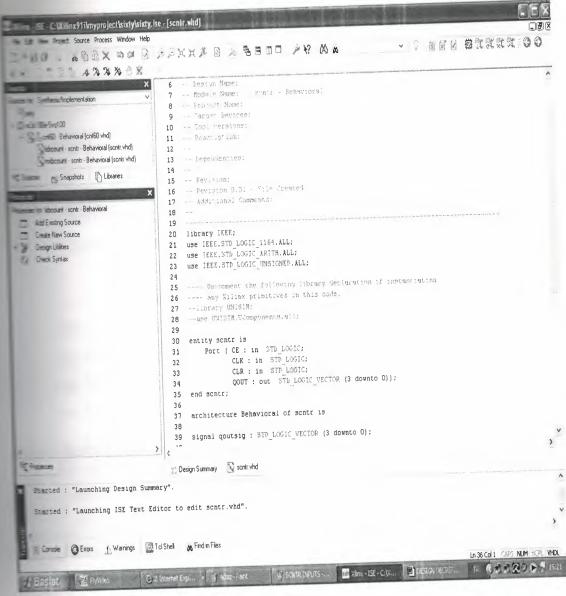

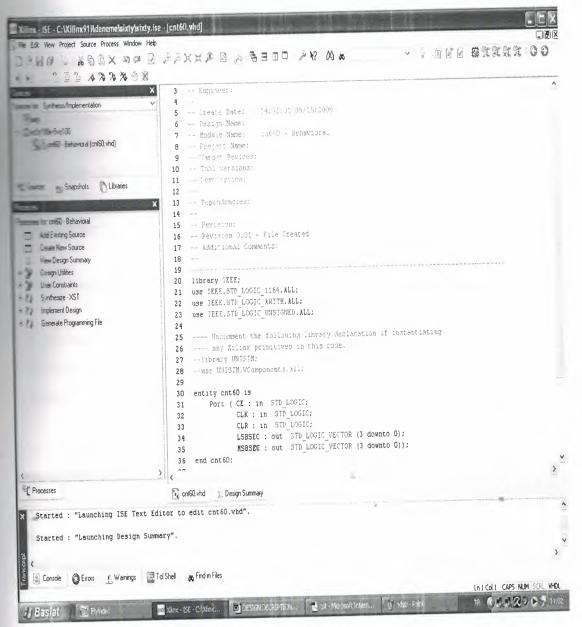

The source file containing the entity/architecture pair displays in the Workspace, and the counter displays in the Source tab, as shown below:

in.

Figure8.Program

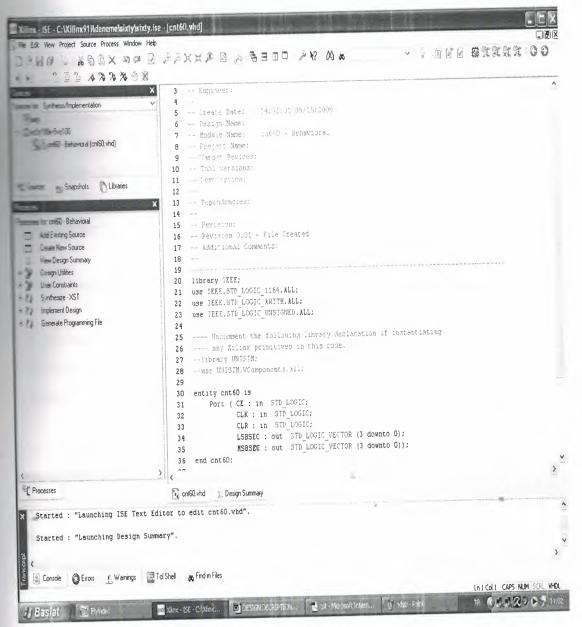

## **2.3)GENERATING a CODE**

- Company:

- Engineer:

- -

- Create Date: 12:38:22 05/08/2008

- Design Name:

- Module Name: cnt60 Behavioral

- Project Name:

- Target Devices:

- Tool versions:

- Description:

- -

- Dependencies:

- ---

- -- Revision:

- -- Revision 0.01 File Created

- -- Additional Comments:

- --

library IEEE;

use IEEE.STD\_LOGIC\_1164.ALL;

use IEEE.STD\_LOGIC\_ARITH.ALL;

use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity cnt60 is

8

Port CE: in STD\_LOGIC;

CLK: in STD\_LOGIC;

CLR: in STD\_LOGIC;

LSBSEC : out STD\_LOGIC\_VECTOR (3 downto 0);

MSBSEC : out STD\_LOGIC\_VECTOR (3 downto 0));

end cnt60;

mentecture Behavioral of cnt60 is

component scntr

pon (CE : in STD\_LOGIC ;

CLK : in STD\_LOGIC ;

CLR : in STD\_LOGIC ;

QOUT : out STD\_LOGIC\_VECTOR ( 3 downto 0 ));

end component;

signal lsbout : STD\_LOGIC\_VECTOR (3 downto 0) ;

signal msbout : STD\_LOGIC\_VECTOR (3 downto 0);

signal msbce : STD\_LOGIC ;

signal lsbtc : STD\_LOGIC ;

signal msbclr : STD\_LOGIC ;

signal msbtc : STD\_LOGIC ;

begin

lsbcount : scntr port map (CE => CE , CLK => CLK , CLR => CLR , QOUT =>

lsbout);

msbcount : scntr port map (CE => msbce ,CLK => CLK,CLR=> msbclr,

QOUT=>msbout);

process (lsbout)

begin

if (lsbout="1001") then

lsbtc <= '1';

else

lsbtc<='0';

end if;

end process;

process (msbout)

begin

is sbout="0110")then

\_\_\_\_\_\_;

cise

<=0';

end if ;

end process;

msbce<=CE and lsbtc;

msbclr <= CLR or msbtc;

LSBSEC <= lsbout;

MSBSEC <= msbout ;

end Behavioral;

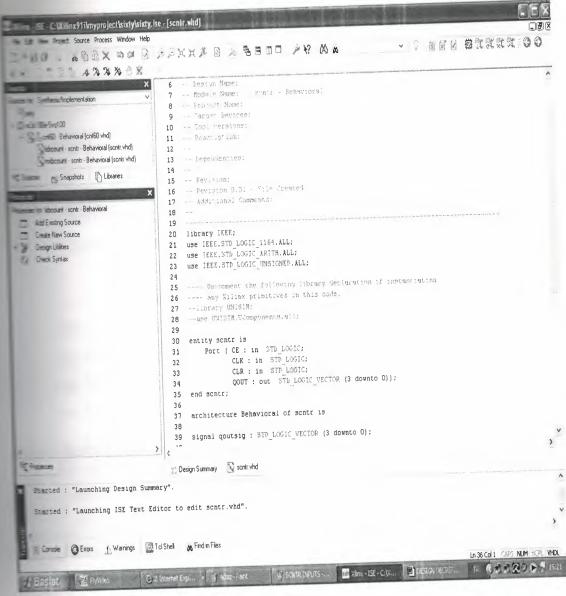

Now one more process must be created . Because we have two counter in this program so second counter we are adding a other source as following :

- 1. Click the New Source button in the New Project Wizard.

- 2. Select VHDL Module as the source type.

- 3. Type in the file name SCNTR.

| BMM File<br>IP (Coregen & Architecture Wizard)<br>MEM File<br>Schematic<br>Implementation Constraints File<br>State Diagram | File name:                   |   |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------------|---|

| <ul> <li>Test Bench WaveForm</li> <li>■ User Document</li> </ul>                                                            | scntr                        |   |

| v Verilog Module                                                                                                            | Location:                    |   |

| V Verilog Test Fixture                                                                                                      | C:\Xilinx91i\myproject\sixty | ) |

| VHDL Module<br>VHDL Library<br>VHDL Package<br>W VHDL Test Bench                                                            |                              |   |

|                                                                                                                             | Add to project               |   |

- Figure9.Adding source

- 4. Verify that the Add to project checkbox is selected.

- 5. Click Next.

Declare the ports for the counter design by filling in the port information as

| Entity Name     | sentr      | - The same reconstruction of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state of the second state |     |          |

|-----------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|

| chilecture Name | Behavioral | wanter and the second second second second second second second second second second second second second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |          |

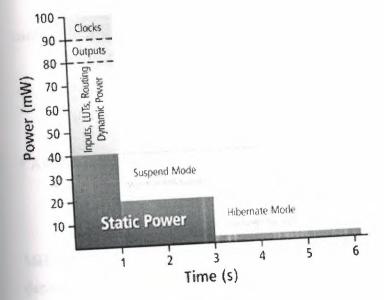

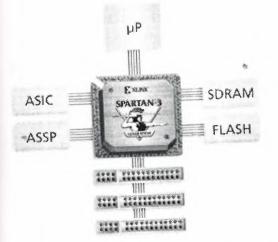

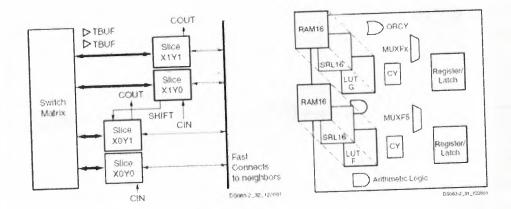

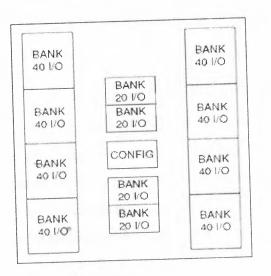

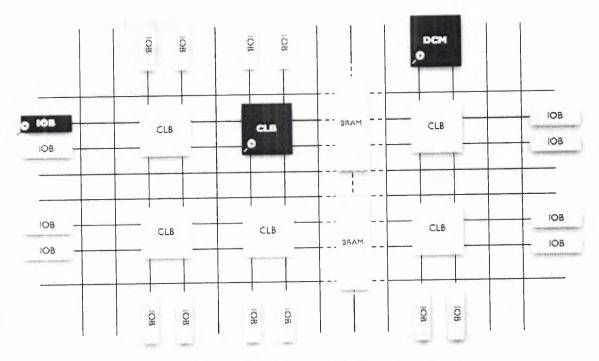

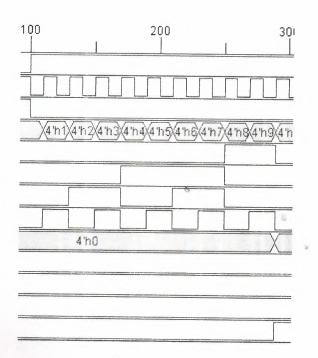

| Purt Name       | Direction  | Bus MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LSB | <u>^</u> |