## A NOVEL MULTILEVEL INVERTER BASED DYNAMIC VOLTAGE RESTORER DESIGN FOR MITIGATING THE VOLTAGE DISTURBANCES ON SENSITIVE LOADS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF APPLIED SCIENCES OF NEAR EAST UNIVERSITY

#### By SAMUEL NII TACKIE

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical and Electronic Engineering

NICOSIA, 2021

### Samuel Nii Tackie: A Novel Multilevel Inverter Based Dynamic Voltage Restorer Design for Mitigating Voltage Disturbances on Sensitive Loads.

#### Approval of Director of the Institute of Graduate School

#### Prof. Dr. K. Hüsnü Can BAŞER

We certify this thesis is satisfactory for the award of the degree of Doctor of Philosophy in Electrical and Electronic Engineering

#### **Examining Committee in Charge:**

Prof. Dr. Senol Bektas

Prof. Dr. Sezai Dincer

Prof. Dr. Hasan Komurcugil

Assoc. Prof. Dr. Samet Biricik

Prof. Dr. Ebrahim Babaei

Committee Chairman, Department of Electrical and Electronic Engineering.

Near East University.

Department of Electrical and

Electronic Engineering. Near East

University.

Department of Computer Engineering.

Eastern Mediterranean University.

Department of Electrical and

Electronic Engineering. European

University of Lefke.

Supervisor, Faculty of Electrical and

Computer Engineering, University of

Tabriz.

I hereby declare that all information contained in this document has been collected and presented

in compliance with academic legislation and ethical standards. I also declare that, as provided

by these Rules and Conduct, all materials and findings that are not original to this work have

been thoroughly cited and referenced.

Name, Surname: Samuel Nii Tackie

Signature:

Date: 8<sup>th</sup> February 2021

#### **ACKNOWLEDGMENT**

I would like to sincerely thank my supervisor Prof. Dr. Ebrahim Babaei for his understanding, patience, and guidance throughout my graduate studies at Near East University. His supervision was paramount in providing a well-rounded experience in projecting my long-term career goals. He encouraged me to be confident in everything I do. I graciously thank you for all you have done for me Prof. Dr. Ebrahim Babaei.

I would also like to thank Prof. Dr. Bulent Bilgehan, Dean and Chairman of Electrical and Electronic Engineering Department, my course Advisor Assist. Prof. Dr. Ali Serener, Thesis monitoring jury members; Prof. Dr. Senol Bektas and Prof. Dr. Sezai Dincer, all the lecturers in Electrical and Electronic Engineering Department and Faculty of Engineering at large for their immense guidance and attention.

Furthermore, I would like to thank my mom Theresa Ansah for her immense love, support and continuous prayer. Lastly, I want to thank all friends and colleagues for their consistent support.

#### **ABSTRACT**

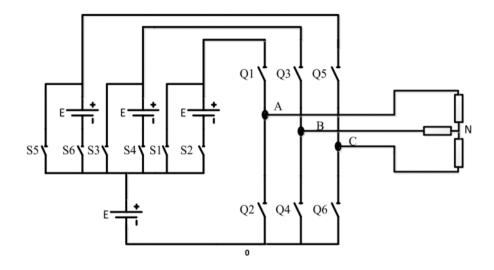

An improved three-phase multilevel inverter, developed from H-bridge is proposed by this thesis. 13-level line voltage and phase voltage of 7-level are generated by the proposed inverter. The proposed three-phase multilevel inverter is made-up of less component count; 18 semiconductor switches of lower voltage ratings, 4 dc-source voltage and 18 driver circuits. Galvanic isolation is enabled when 3 single-phase transformers are incorporated. This makes the proposed inverter suitable for application in three-phase power systems such as dynamic voltage restorer (DVR). The proposed three-phase inverter is simple to control using fundamental frequency control technique and less complex structurally. Comparative investigation of the proposed three-phase inverter and other recently published three-phase multilevel inverters regarding total component quantity, dc voltage count, standing voltage, output voltage level count and driver circuit count is analyzed. Comprehensive explanation of the applied control technique is provided. Lastly, functionality of proposed three-phase multilevel inverter is validated by experimental prototype and EMTDC/PSCAD software based simulation.

*Keywords:* Three-phase multilevel inverter, standing voltage, multilevel inverter, component count, three-phase inverter, dynamic voltage restorer.

#### ÖZET

Bu tezde, H-köprüsünden geliştirilen üç fazlı çok seviyeli evirici önerilmiştir.Önerilen evirici tarafından 13 seviyeli hat gerilimi ve 7 seviyeli faz gerilimi üretilir.Önerilen üç fazlı çok seviyeli evirici, daha az bileşen sayısından oluşmaktadır; Daha düşük gerilim değerlerine sahip 18 adet yarı iletken anahtar, 4 adet doğru akım kaynak gerilimi ve 18 adet sürücü devresi.Üç tek fazlı transformatör dahil edildiğinde galvanik izolasyon etkinleştirilir.Bu, önerilen eviriciyi, dinamik gerilim yenileyici (DVR) gibi üç fazlı güç sistemlerinde uygulamanması için uygun hale getirmektedir.Önerilen üç fazlı evirici, temel frekans kontrol tekniğini kullanarak kontrol etmek basittir ve yapısal olarak daha az karmaşıktır.Önerilen üç faz evirici ile diğer son yayınlanan üç fazlı çok seviyeli eviricilerin, toplam bileşen miktarı, doğru akım gerilim sayısı, sabit gerilim, çıkış gerilim seviyesi sayısı ve sürücü devre sayısı ile ilgili karşılaştırmalı incelemesi analiz edilir.Uygulanan kontrol tekniğinin kapsamlı açıklaması verilmiştir. Son olarak, önerilen üç fazlı çok seviyeli eviricinin işlevselliği deneysel prototip ve EMTDC / PSCAD yazılım tabanlı simülasyon ile doğrulanır.

Anahtar Kelimeler: Üç fazlı çok seviyeli evirici, sabit gerilim, çok seviyeli evirici, bileşen sayısı, üç faz evirici, dinamik gerilim yenileyici.

#### TABLE OF CONTENTS

| ACKNOWLEDGMENT                                               | i    |

|--------------------------------------------------------------|------|

| ABSTRACT                                                     | ii   |

| ÖZET                                                         | iii  |

| TABLE OF CONTENTS                                            | iv   |

| LIST OF FIGURES                                              | viii |

| LIST OF TABLES.                                              | xii  |

|                                                              |      |

| CHAPTER 1: INTRODUCTION                                      |      |

| 1.1 Overview                                                 | 1    |

| 1.2 Problem Statement                                        | 5    |

| 1.3 The Aim of the Thesis                                    | 6    |

| 1.4 The Importance of the Thesis                             | 6    |

| 1.5 Limitation of the Study                                  | 7    |

| 1.6 Overview of the Thesis                                   | 7    |

|                                                              |      |

| CHAPTER 2: LITERATURE REVIEW OF MULTILEVEL INVERTER          |      |

| 2.1 Introduction                                             | 9    |

| 2.2 Cascaded H-Bridge                                        | 9    |

| 2.2.1 Symmetrical and Asymmetrical CHB                       | 12   |

| 2.3 Flying Capacitor Multilevel Inverter                     | 15   |

| 2.4 Neutral Point Clamped Multilevel Inverter                | 17   |

| 2.5 Comparative Analysis of Cascaded HB and Flying Capacitor | 20   |

| 2.6 Comparative Analysis of Cascaded HB and NPC                             | 22  |

|-----------------------------------------------------------------------------|-----|

| 2.7 Application of Multilevel Inverters                                     | 23  |

| 2.8 Cascaded MLI Topologies                                                 | 24  |

| 2.8.1 Single Phase Cascaded MLI Topologies                                  | 25  |

| 2.8.2 Three-phase Cascaded MLI Topologies                                   | 37  |

| 2.9 Multilevel Inverter Control Techniques                                  | 45  |

| 2.10 Conclusion                                                             | 46  |

| CHAPTER 3: INVESTIGATION OF MULTILEVEL INVERTER BASED DYNA VOLTAGE RESTORER | MIC |

| 3.1 Introduction                                                            | 48  |

| 3.2 DVR Components                                                          | 51  |

| 3.3 DVR Operational Range                                                   | 53  |

| 3.4 DVR Classification                                                      | 54  |

| 3.5 DVR Control System                                                      | 59  |

| 3.6 Application of DVR                                                      | 63  |

| 3.7 DVR Topologies                                                          | 64  |

| 3.8 Conclusion                                                              | 74  |

|                                                                             |     |

| CHAPTER 4: PROPOSED THREE-PHASE MLI BASED DYNAMIC VOLTAGE RESTORER          | Ē   |

| 4.1 Proposed Three-Phase MLI                                                | 75  |

| 4.2 Proposed MLI Control                                                    | 84  |

| 4.3 Blocking Voltage                                                        | 86  |

| 4.4 Calculation of Inverter Losses                                          | 87  |

| 4.4.1 Conduction Power Losses                                        | 87  |

|----------------------------------------------------------------------|-----|

| 4.4.2 Switching Power Losses                                         | 88  |

| 4.5 Comparative Investigation                                        | 89  |

| 4.6 Total Harmonic Distortion of Proposed MLI                        | 94  |

| 4.7 Proposed Three-phase MLI based DVR                               | 96  |

| 4.8 Limitation of Proposed MLI Based DVR                             | 97  |

| 4.9 Conclusion                                                       | 99  |

|                                                                      |     |

| CHAPTER 5: SIMULATION AND EXPERIMENTAL RESULTS                       |     |

| 5.1 Introduction                                                     | 101 |

| 5.2 Simulation Results                                               | 101 |

| 5.3 Experimental Results                                             | 111 |

| 5.4 Multilevel Inverter Based DVR Simulation                         | 114 |

| 5.5 DVR Simulation Results with Varying Voltage Sag and Swell Values | 119 |

| 5.6 DVR Simulation under Varying Fault Conditions                    | 126 |

| 5.7 Conclusion                                                       | 150 |

|                                                                      |     |

| CHAPTER 6: CONCLUSION                                                | 151 |

| 6.1 Futurework                                                       | 152 |

|                                                                      |     |

| REFERENCES                                                           | 153 |

|                                                                      |     |

| APPENDICES                                                           |     |

| APPENDIX 1: Implementation of Proposed MLI in PSCAD Software         | 167 |

| APPENDIX 2: Implementation of Proposed MLI DVR in PSCAD Software | 171 |

|------------------------------------------------------------------|-----|

| APPENDIX 3: Comparison Based References                          | 172 |

| APPENDIX 4: Curriculum Vitae                                     | 174 |

| APPENDIX 5: Ethical Approval Report                              | 177 |

| APPENDIX 6: Similarity Report                                    | 178 |

#### LIST OF FIGURES

| Figure 1.1: Classification of multilevel inverters                       | 3  |

|--------------------------------------------------------------------------|----|

| Figure 2.1: 5-levels Cascaded H bridge inverter                          | 10 |

| Figure 2.2: n-level cascaded H-Bridge converter                          | 12 |

| Figure 2.3: Five level flying capacitor converter                        | 16 |

| Figure 2.4: Neutral point clamped inverter                               | 18 |

| Figure 2.5: (a) NPC (b) ANPC (c) T-type NPC                              | 18 |

| Figure 2.6: Single phase NPC- PWM inverter                               | 20 |

| Figure 2.7: H-bridge MLI                                                 | 26 |

| Figure 2.8: H-bridge based cascaded MLI                                  | 26 |

| Figure 2.9: Basic unit of positive16-level MLI                           | 27 |

| Figure 2.10: 31-level cascaded MLI                                       | 28 |

| Figure 2.11: Positive 10-levels inverter                                 | 29 |

| Figure 2.12: Cascaded multilevel inverter.                               | 30 |

| Figure 2.13: Bidirectional and unidirectional switch based MLI.          | 31 |

| Figure 2.14: Switching states of presented MLI                           | 32 |

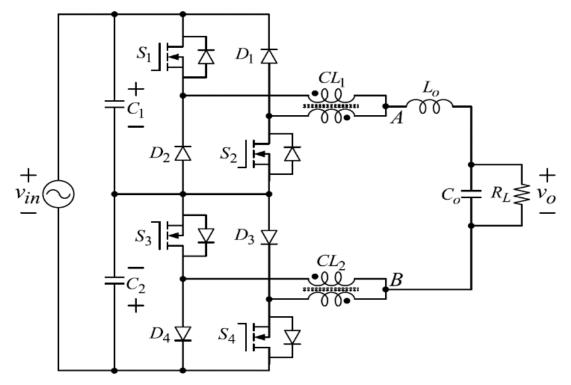

| Figure 2.15: Hybrid coupled inductor MLI.                                | 33 |

| Figure 2.16: Cascaded hybrid coupled inductor MLI                        | 33 |

| <b>Figure 2.17:</b> 15-levels H-bridge inverter                          | 34 |

| <b>Figure 2.18:</b> 71-levels H-bridge inverter                          | 34 |

| Figure 2.19: Fundamental multilevel inverter topology                    | 35 |

| Figure 2.20: 31-levels and 127-level developed H-bridge                  | 35 |

| <b>Figure 2.21:</b> 17-levels single-phase inverter                      | 36 |

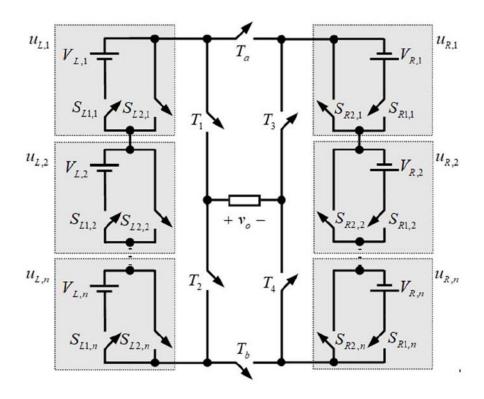

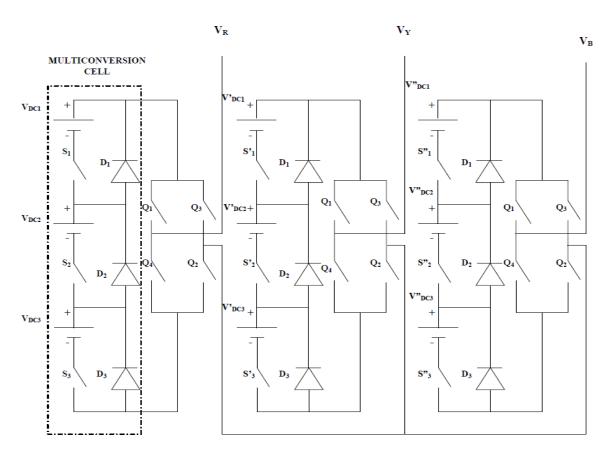

| Figure 2.22: Three-phase cascaded H-bridge MLI                           | 37 |

| Figure 2.23: Three-phase NPC MLI.                                        | 38 |

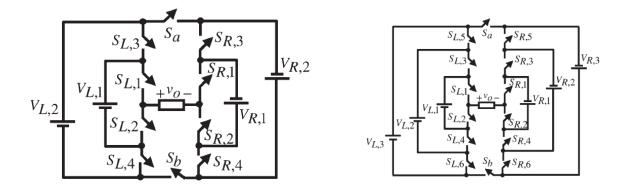

| Figure 2.24: Full and Half H-bridge three-phase MLI                      | 39 |

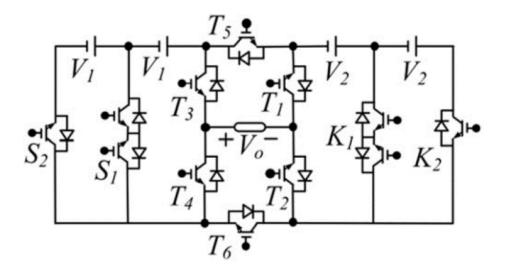

| Figure 2.25: T-type ZS MLI                                               | 40 |

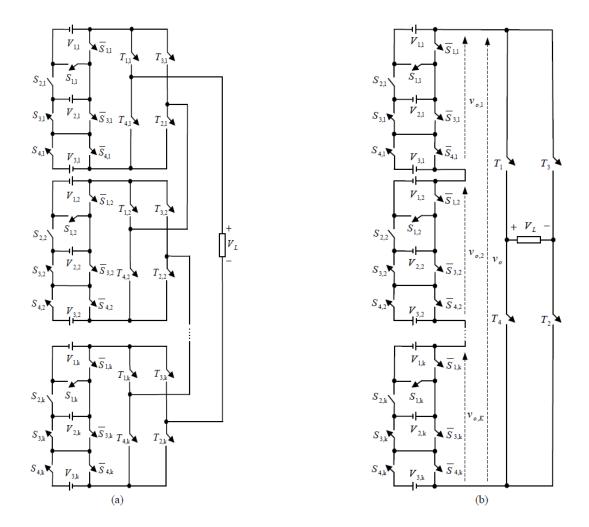

| Figure 2.26: Three-phase cascaded inverter                               | 41 |

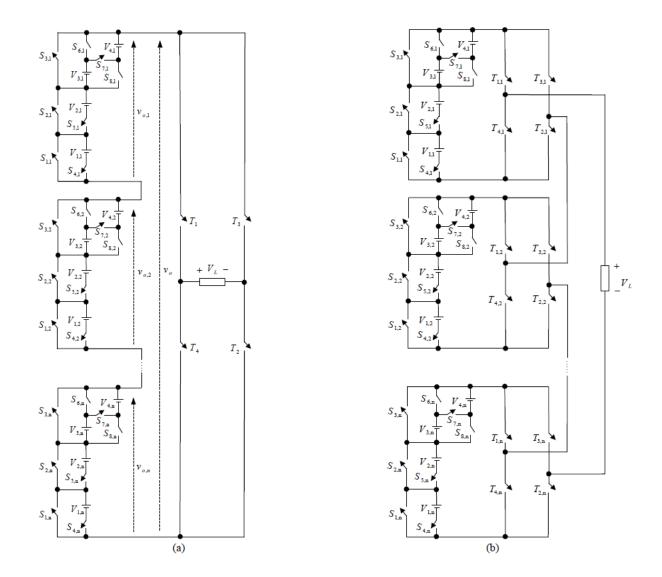

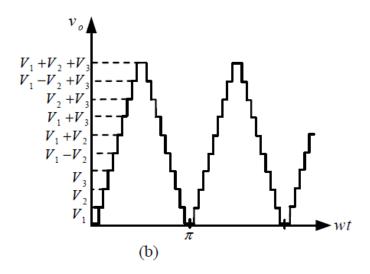

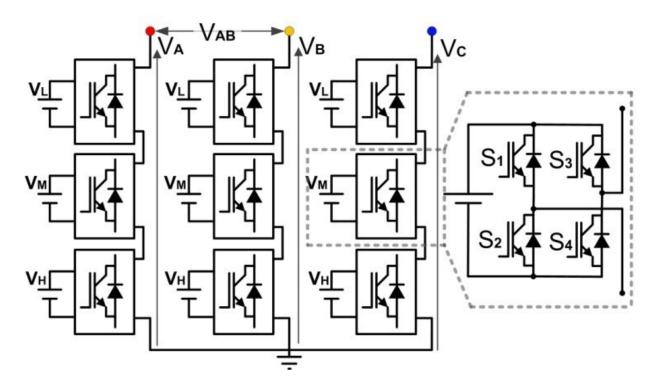

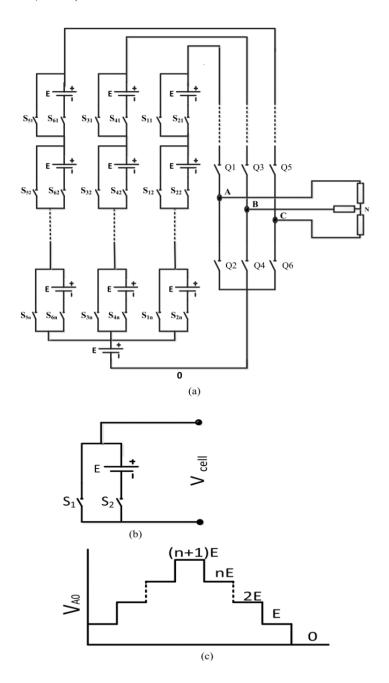

| Figure 2.27: (a) Cascaded modular MLI (b) Basic unit (c) Output waveform | 42 |

| Figure 2.28: Three-phase modular MLI                               | 43 |

|--------------------------------------------------------------------|----|

| Figure 2.29: Modular multilevel inverter                           | 43 |

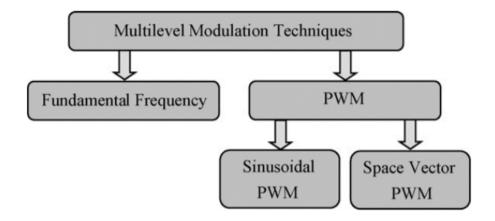

| Figure 2.30: MLI modulation classifications                        | 45 |

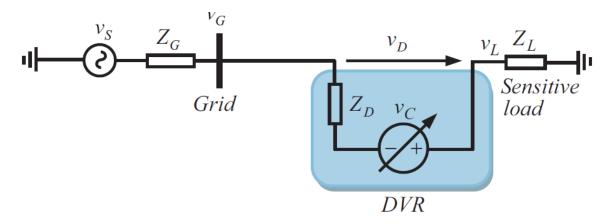

| Figure 3.1: DVR equivalent circuit                                 | 50 |

| Figure 3.2: DVR location and mode of operation                     | 51 |

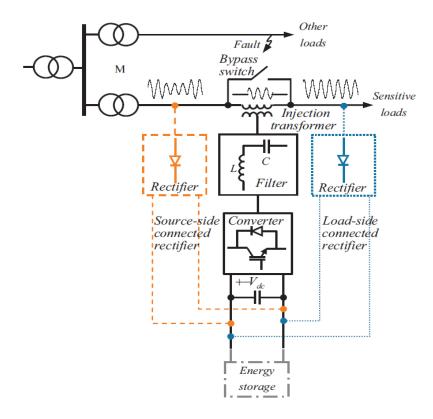

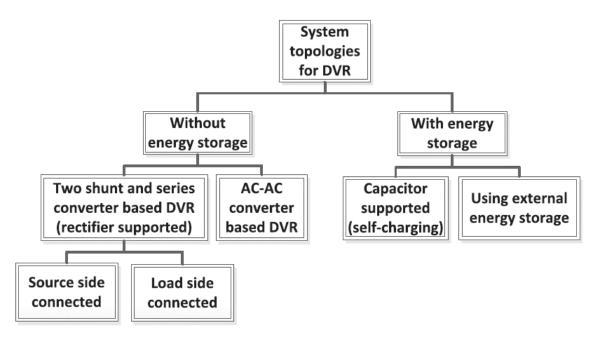

| Figure 3.3: DVR classification based on ESS                        | 55 |

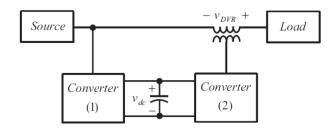

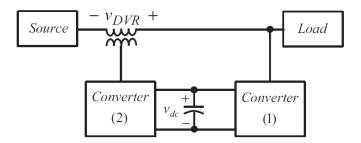

| Figure 3.4: DVR without ESS connected at supply end                | 56 |

| Figure 3.5: DVR without ESS connected at load end                  | 56 |

| Figure 3.6: DVR with a dc-link                                     | 56 |

| Figure 3.7: DVR with ESS                                           | 57 |

| Figure 3.8: Cascaded H-Bridge based DVR                            | 58 |

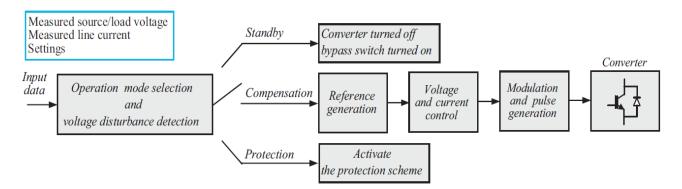

| Figure 3.9: DVR control block diagram                              | 59 |

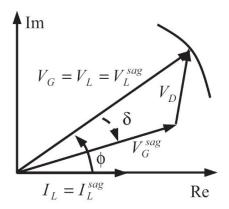

| Figure 3.10: Pre-sag compensation                                  | 61 |

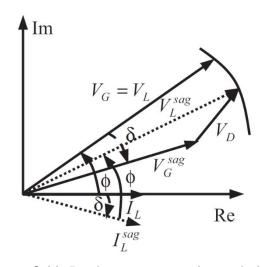

| Figure 3.11: In-phase compensation technique                       | 62 |

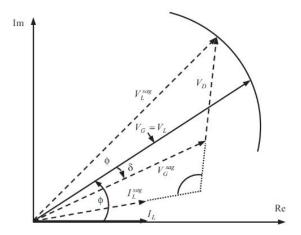

| Figure 3.12: Minimum energy compensation technique                 | 63 |

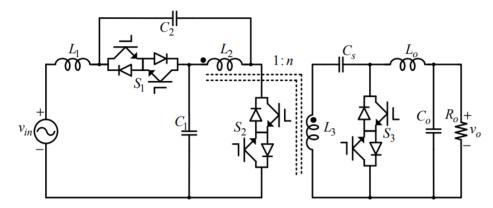

| Figure 3.13: Quasi DVR topology with HFT                           | 64 |

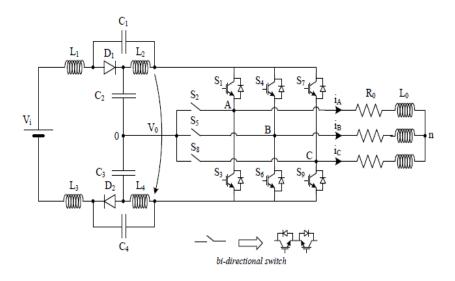

| Figure 3.14: Half-Bridge ZS converter                              | 65 |

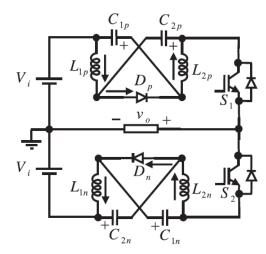

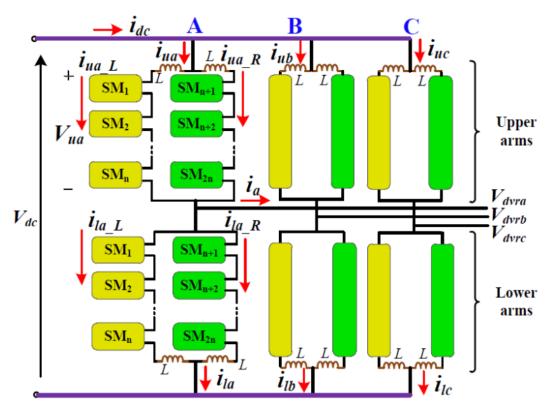

| Figure 3.15: Parallel MMC                                          | 66 |

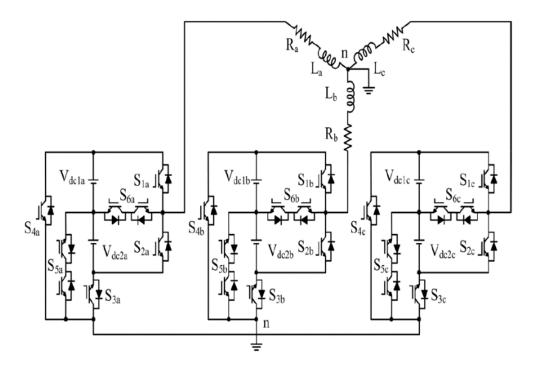

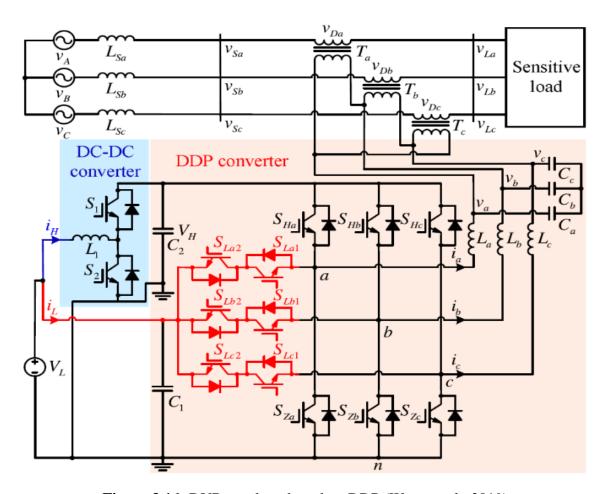

| Figure 3.16: DVR topology based on DDP                             | 67 |

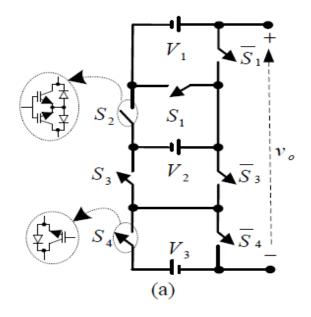

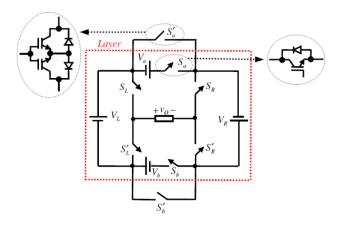

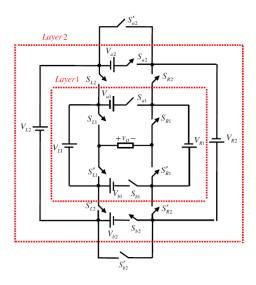

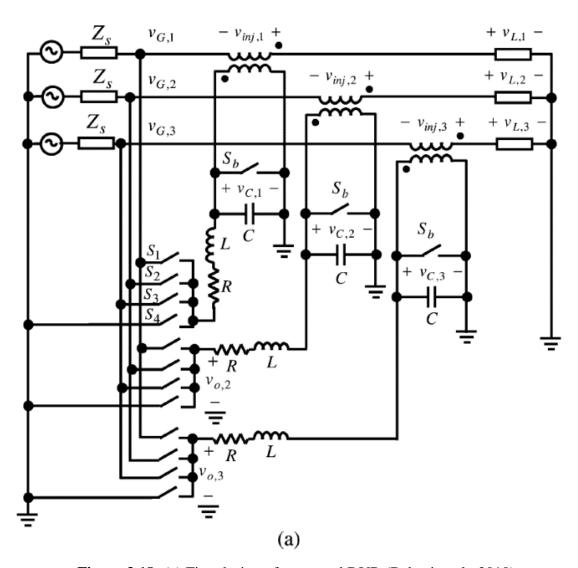

| Figure 3.17: Phase one of switching cell MLI                       | 68 |

| Figure 3.18: First and second design of the proposed DVR           | 69 |

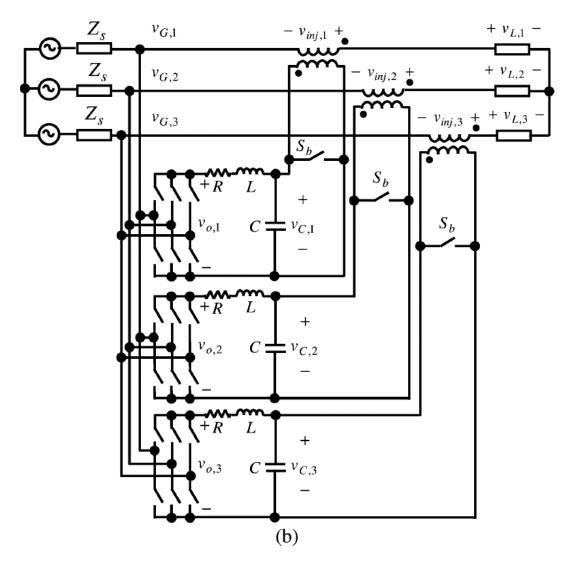

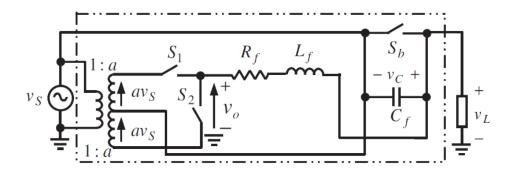

| Figure 3.19: Single-phase DVR                                      | 71 |

| Figure 3.20: Single-phase ac-ac converter DVR waveform             | 72 |

| Figure 3.21: Single-phase ac-ac converter DVR waveform             | 73 |

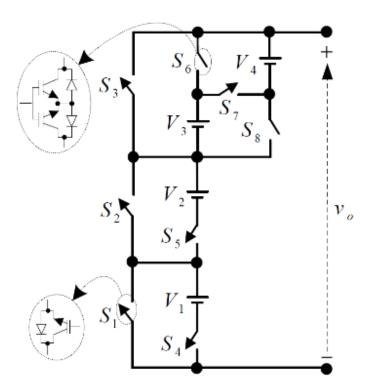

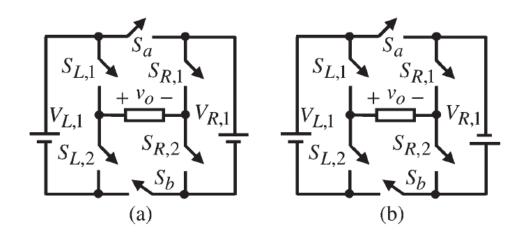

| Figure 4.1: Conventional H-bridge MLI                              | 76 |

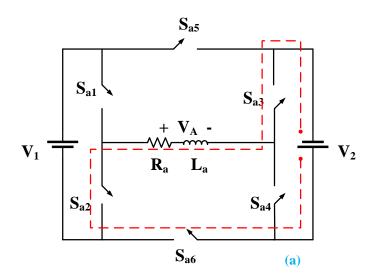

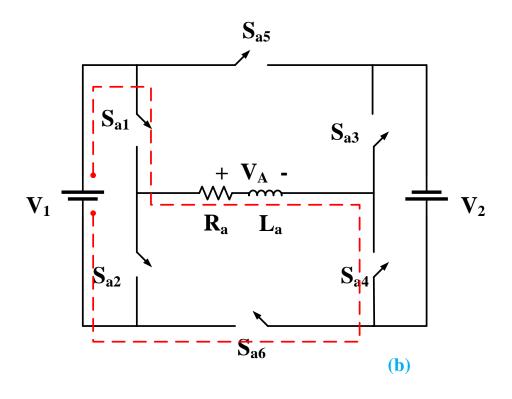

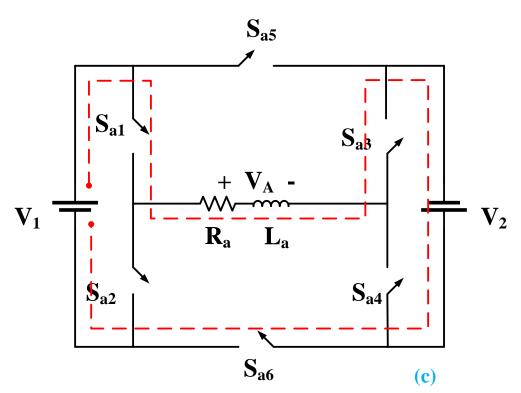

| Figure 4.2: Single-phase structure of proposed MLI                 | 76 |

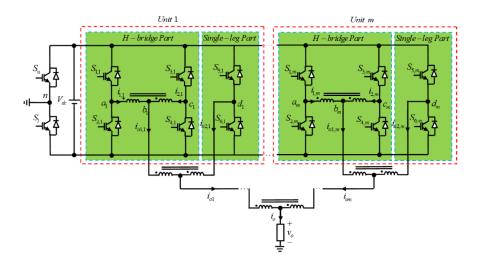

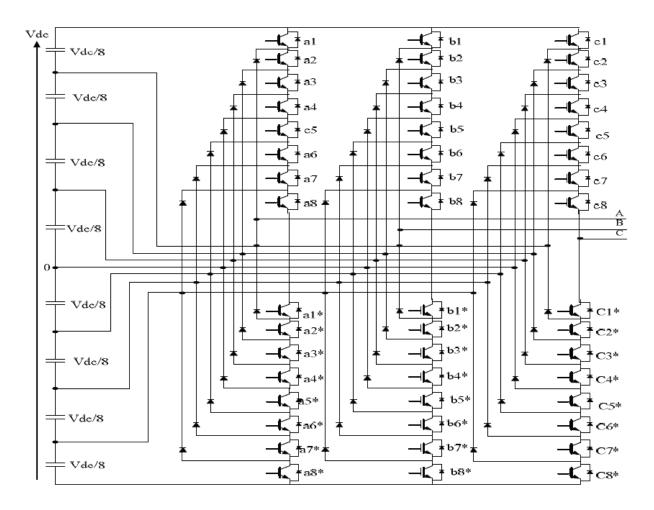

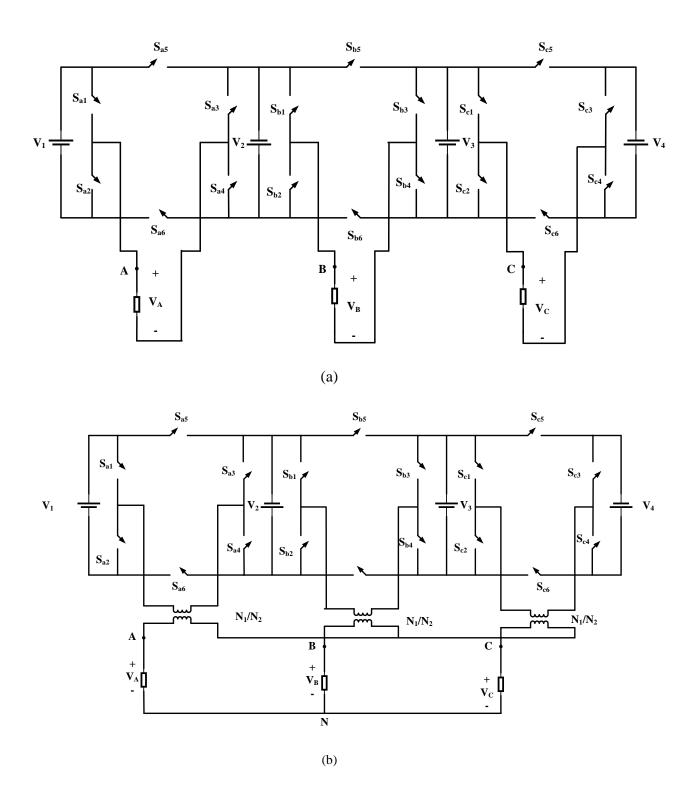

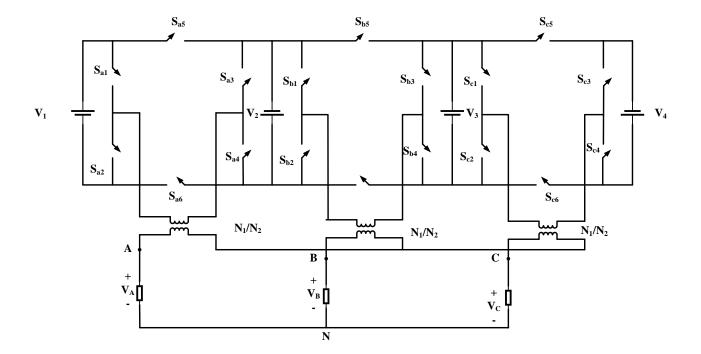

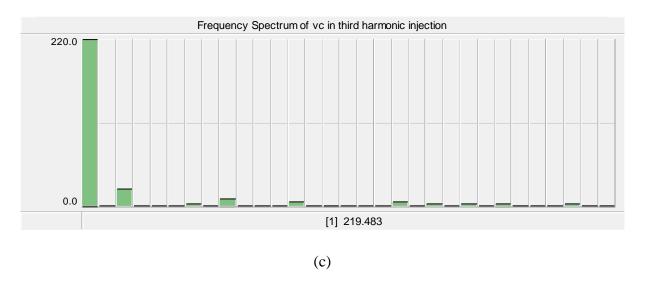

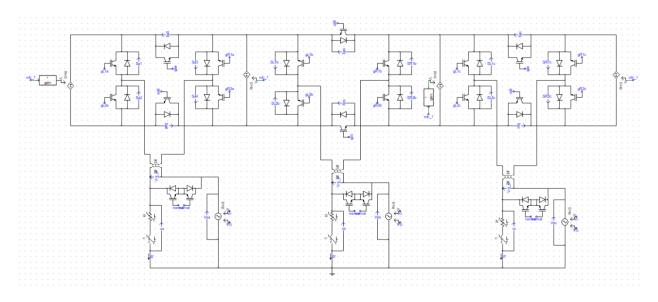

| Figure 4.3: Proposed three-phase multilevel inverter               | 77 |

| Figure 4.4: Conducting switches in each switching state in phase A | 84 |

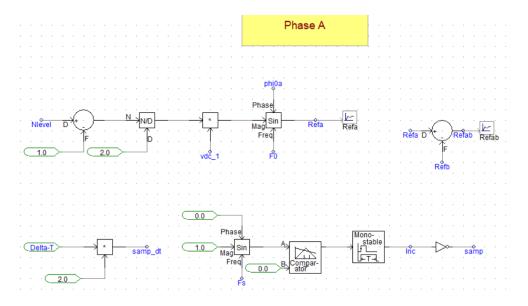

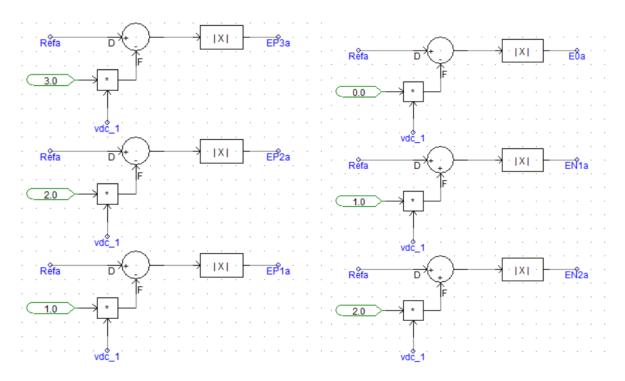

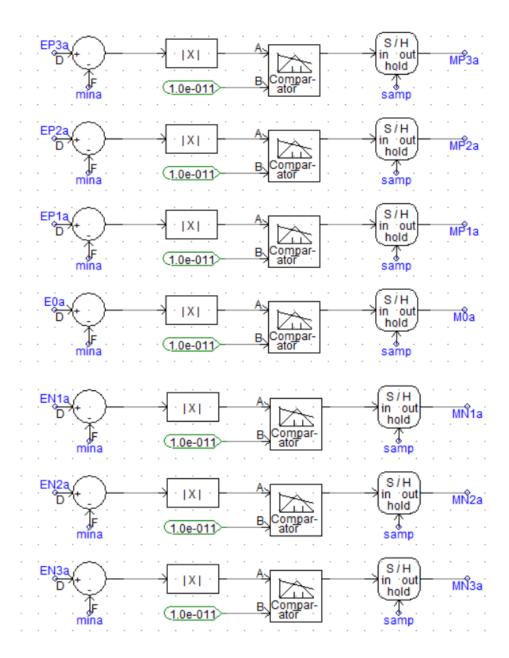

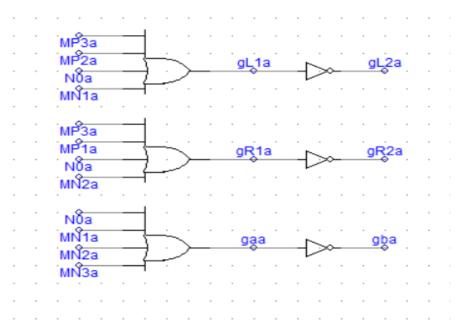

| Figure 4.5: Fundamental frequency control method (FFCM             | 85 |

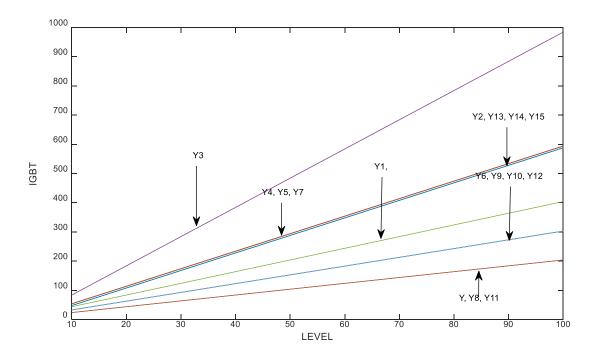

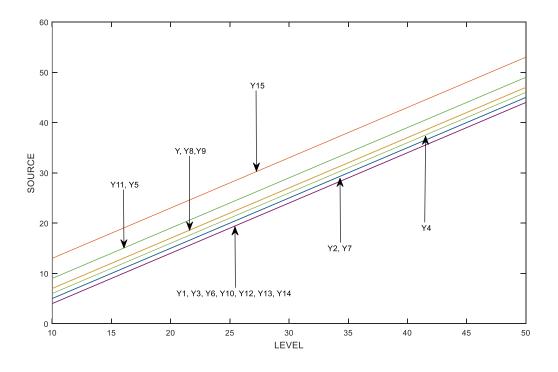

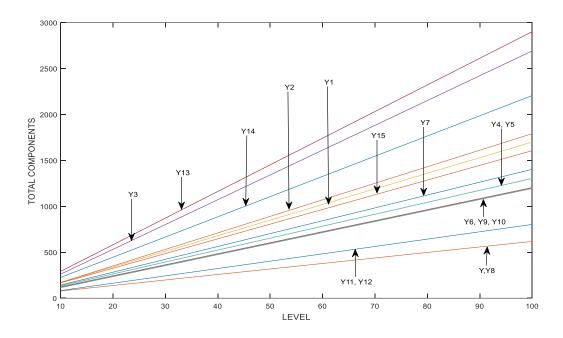

| Figure 4.6: Graph of Nigbt versus NLEVEL                           | 92 |

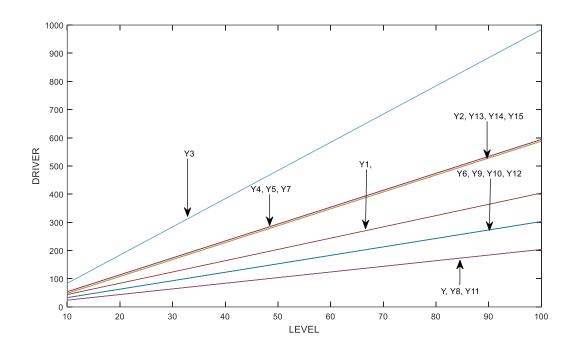

| Figure 4.7: Graph of N <sub>DRIVER</sub> versus N <sub>LEVEL</sub>                  | 93  |

|-------------------------------------------------------------------------------------|-----|

| Figure 4.8: Graph of N <sub>DC-SOURCE</sub> versus N <sub>LEVEL</sub>               | 93  |

| Figure 4.9: Graph of N <sub>TOTAL</sub> versus N <sub>LEVEL</sub>                   | 94  |

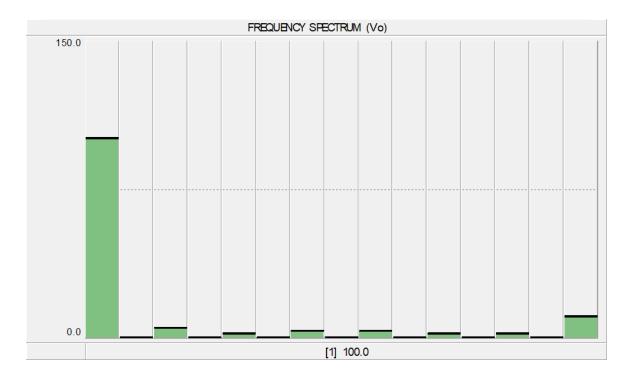

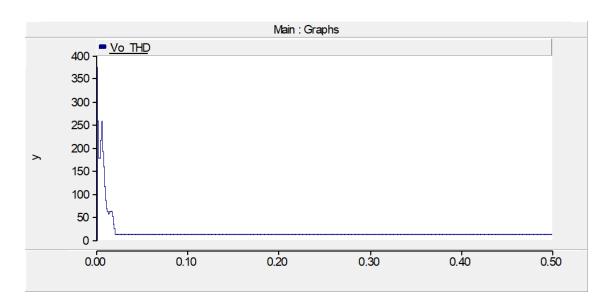

| Figure 4.10: Frequency spectrum                                                     | 95  |

| Figure 4.11: THD waveform of output voltage                                         | 96  |

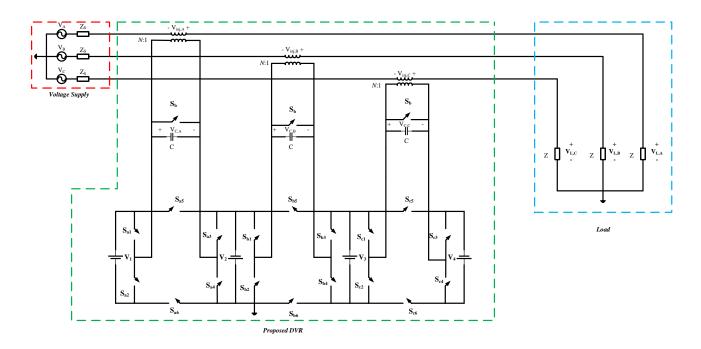

| Figure 4.12: Proposed MLI based DVR                                                 | 97  |

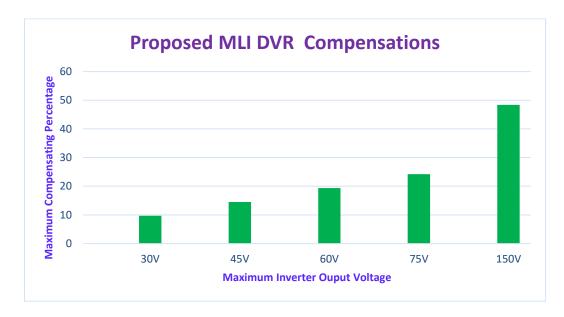

| Figure 4.13: Compensation percentage of proposed DVR                                | 99  |

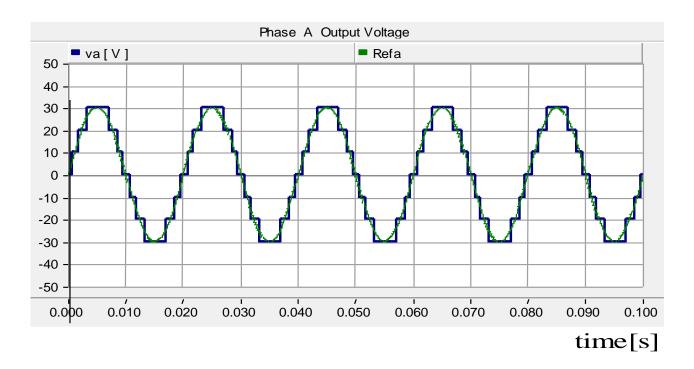

| Figure 5.1: Proposed three-phase MLI load connected in Y configuration              | 102 |

| Figure 5.2: Phase A load voltage and reference signal                               | 103 |

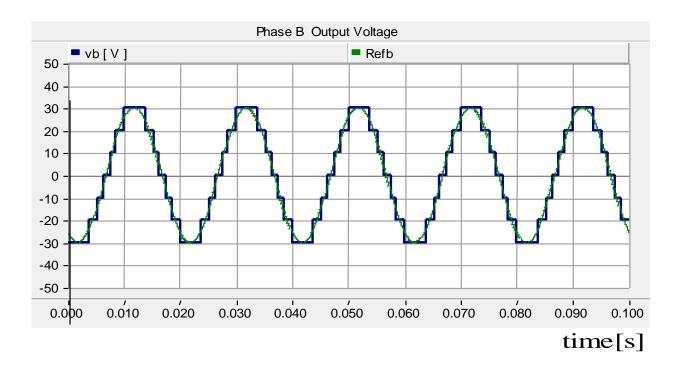

| Figure 5.3: Phase B load voltage and reference signal                               | 104 |

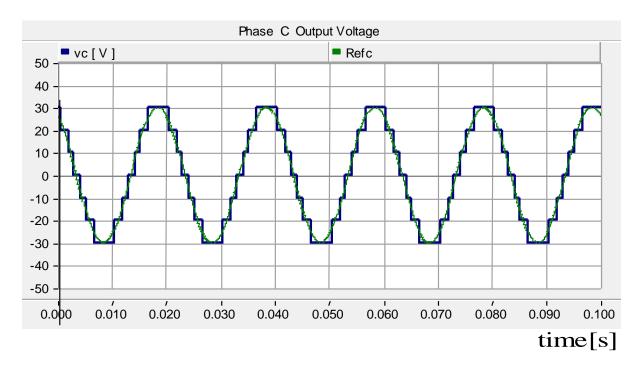

| Figure 5.4: Phase C load voltage and reference signal                               | 104 |

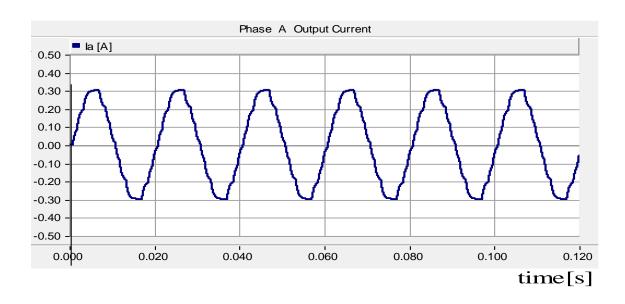

| Figure 5.5: Phase A load current waveform                                           | 105 |

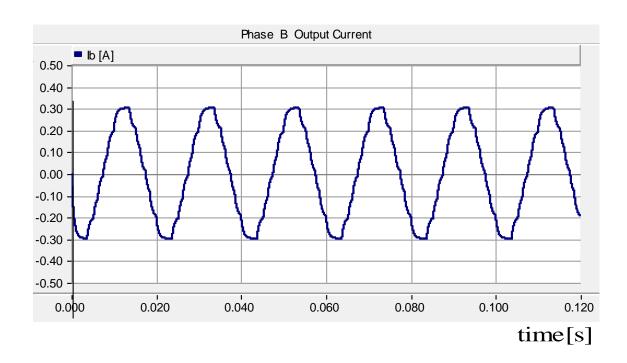

| Figure 5.6: Phase B load current waveform                                           | 105 |

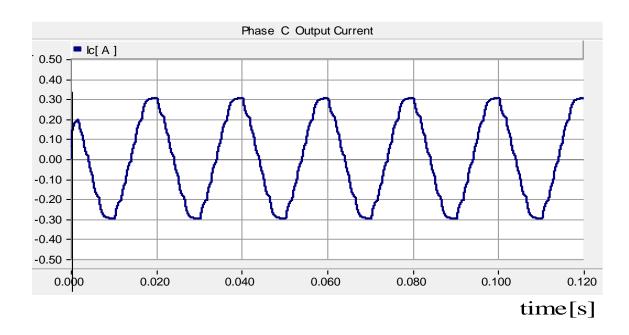

| Figure 5.7: Phase C load current waveform                                           | 106 |

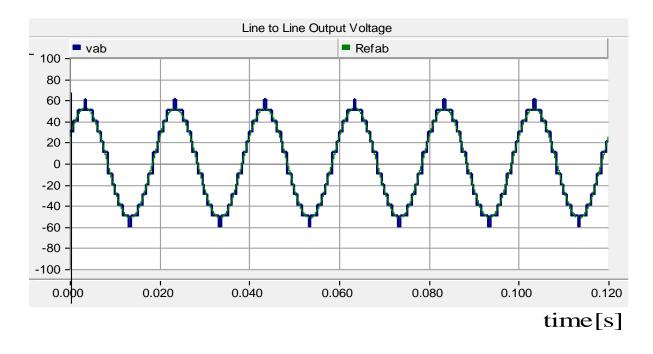

| Figure 5.8: Phase AB line-to-line load voltage waveform                             | 106 |

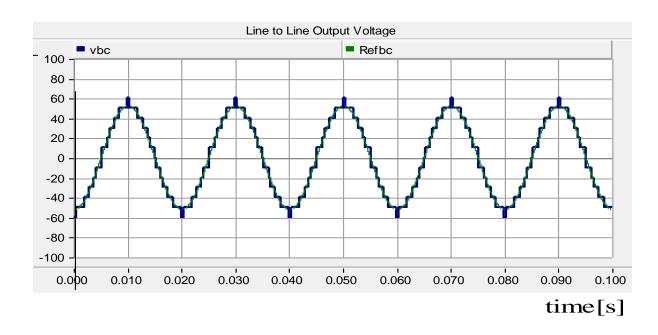

| Figure 5.9: Phase BC line-to-line load voltage waveform                             | 107 |

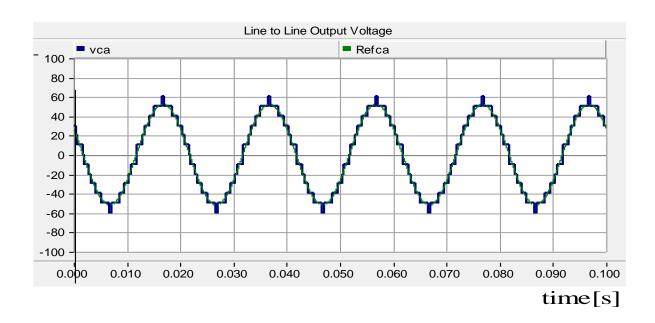

| Figure 5.10: Phase CA line-to-line load voltage waveform                            | 107 |

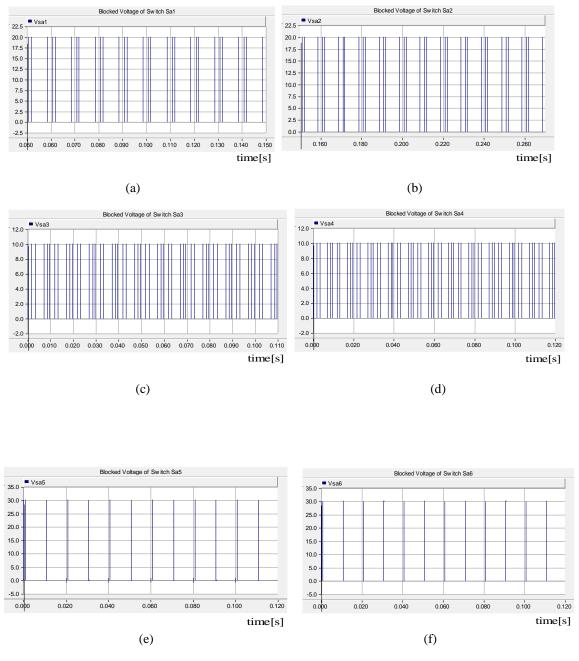

| Figure 5.11: Blocked voltage of switches in Phase A                                 | 108 |

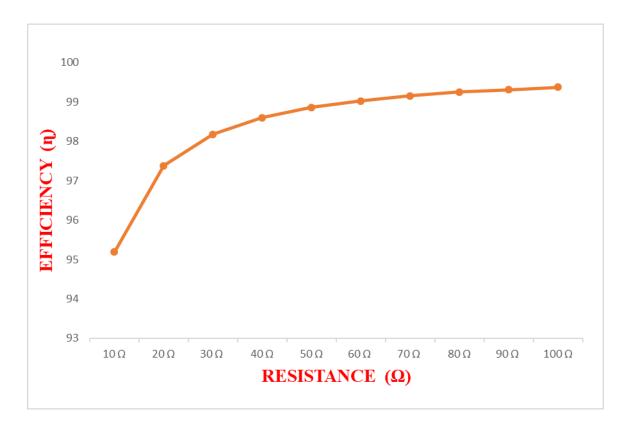

| Figure 5.12: Efficiency curve with constant input voltage (100V)                    | 110 |

| Figure 5.13: Experimental prototype                                                 | 112 |

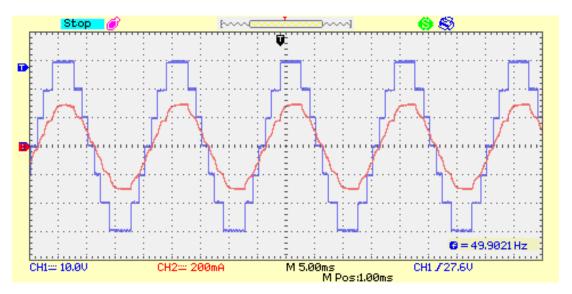

| Figure 5.14: Phase A voltage and current experimental waveforms                     | 112 |

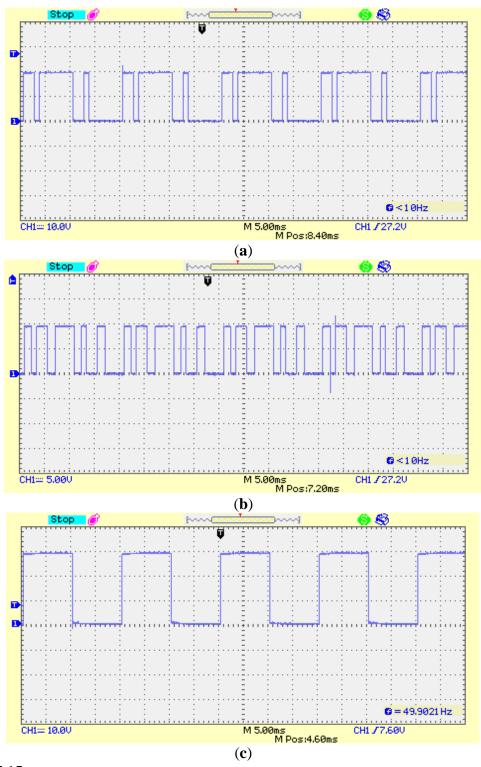

| Figure 5.15: Blocked voltage of switches in Phase A                                 | 113 |

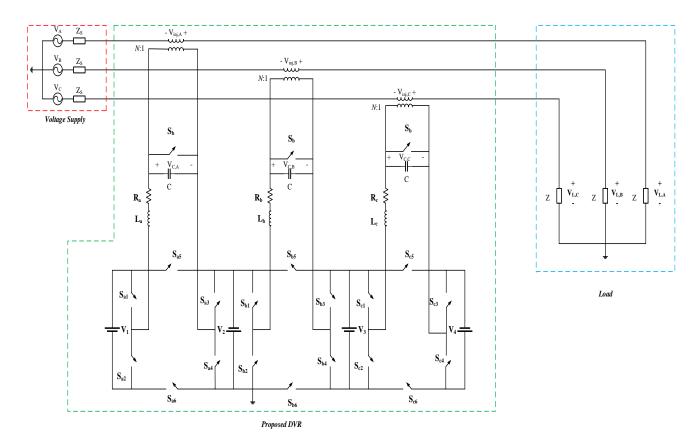

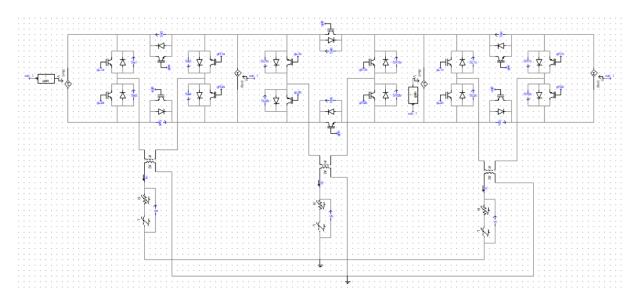

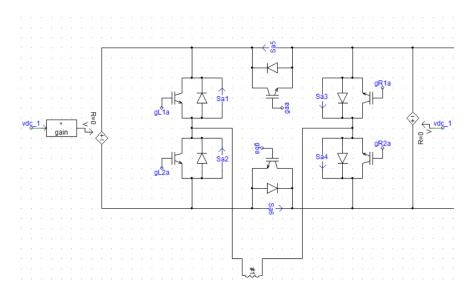

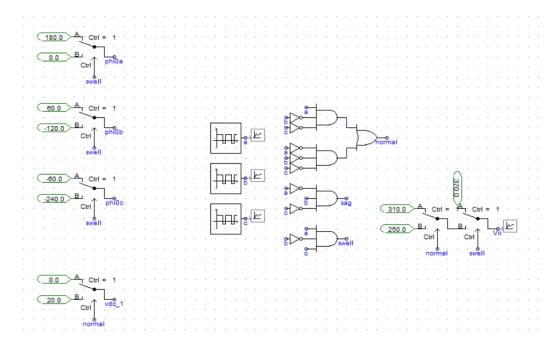

| Figure 5.16: Proposed DVR Topology                                                  | 114 |

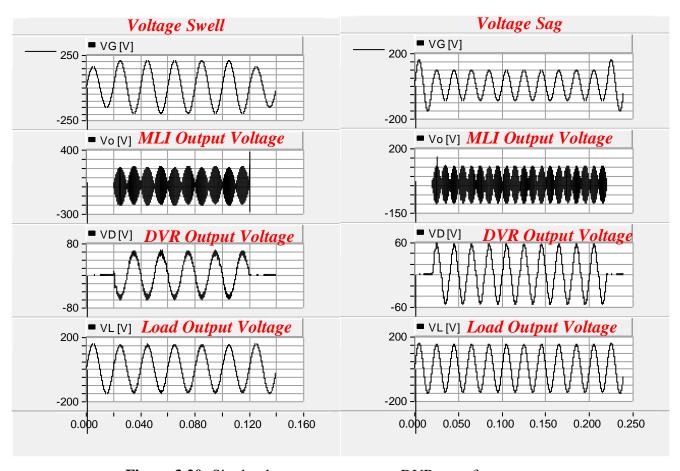

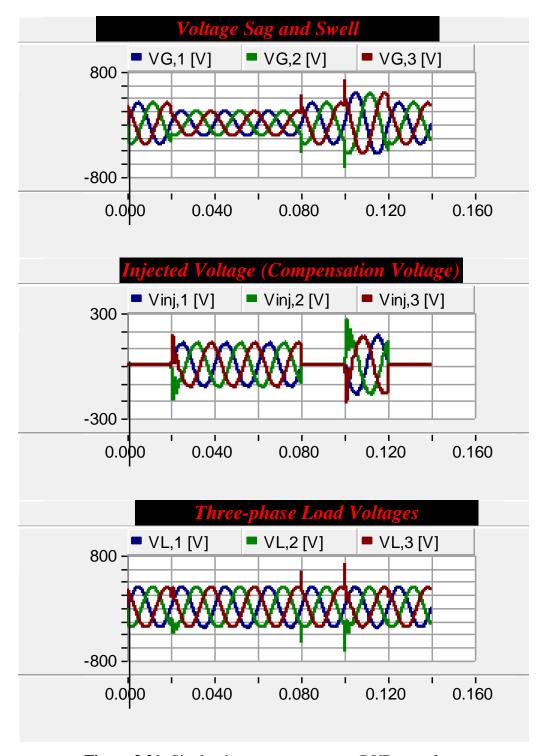

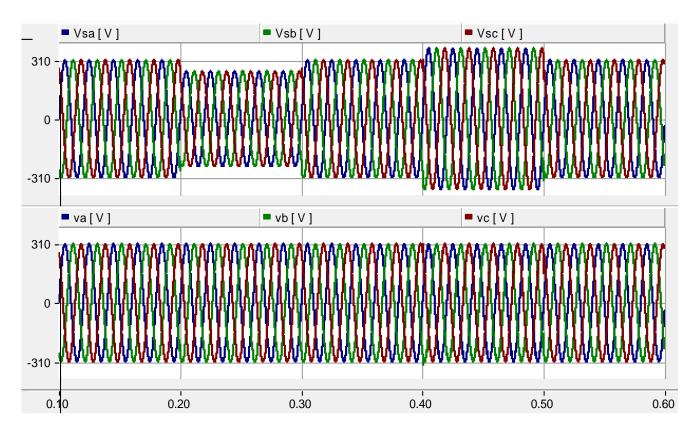

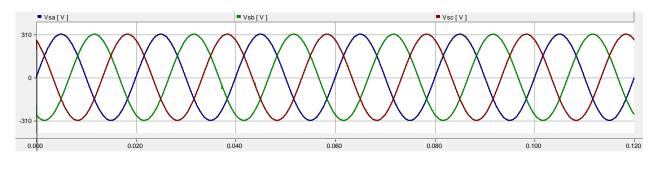

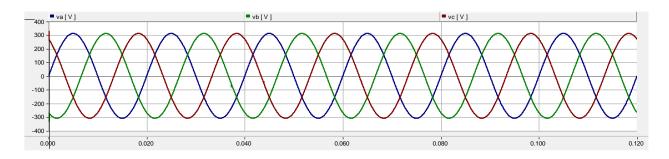

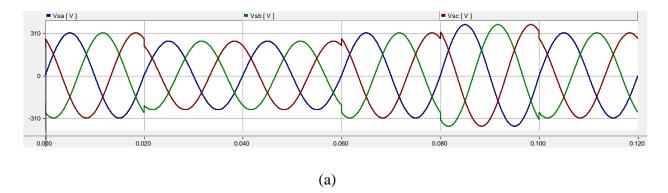

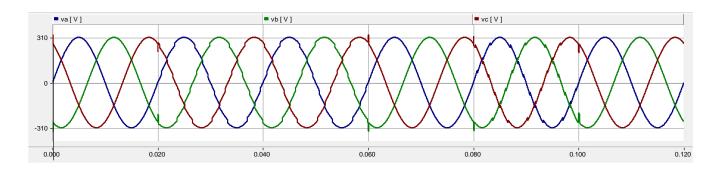

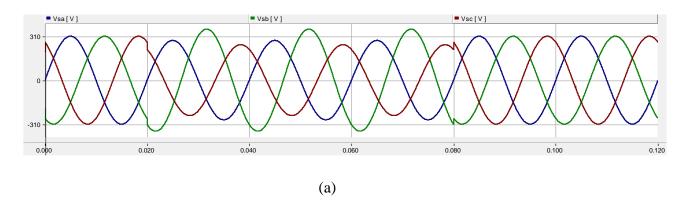

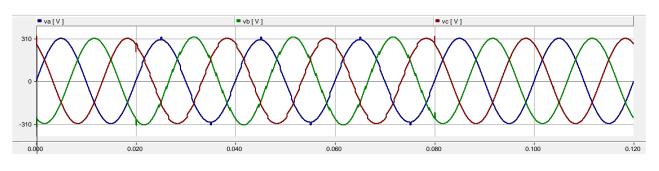

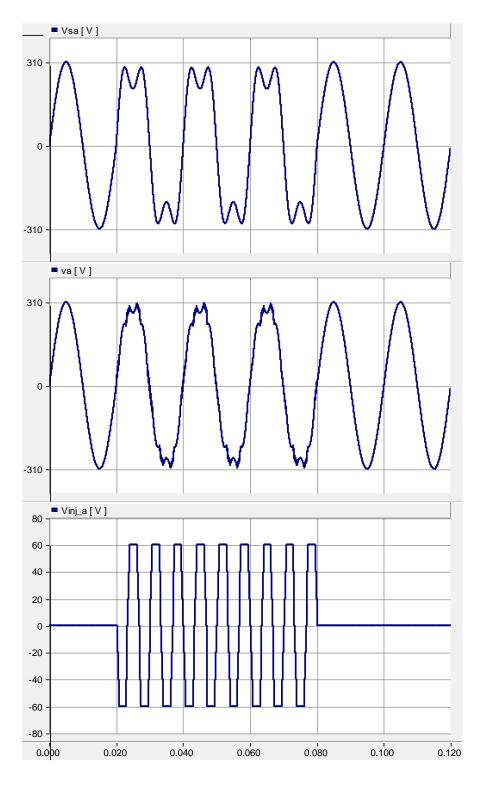

| Figure 5.17: Three-phase input and output voltage waveforms under grid disturbances | 115 |

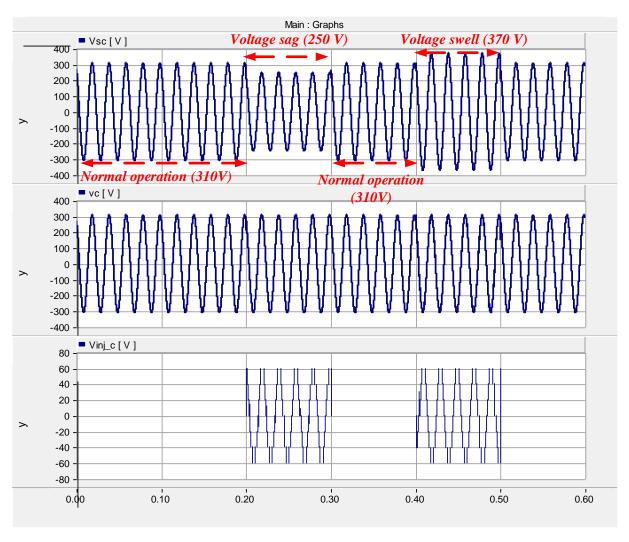

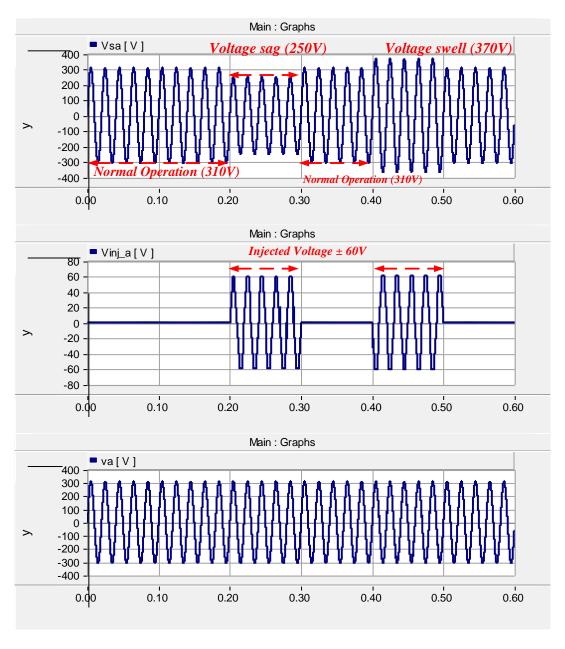

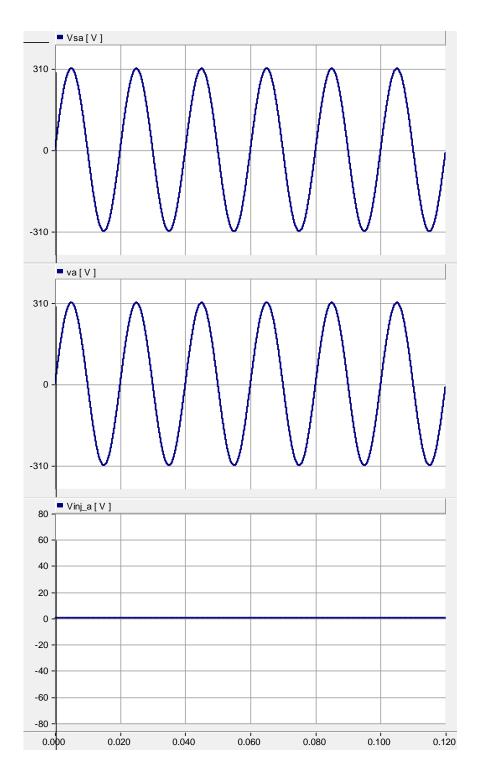

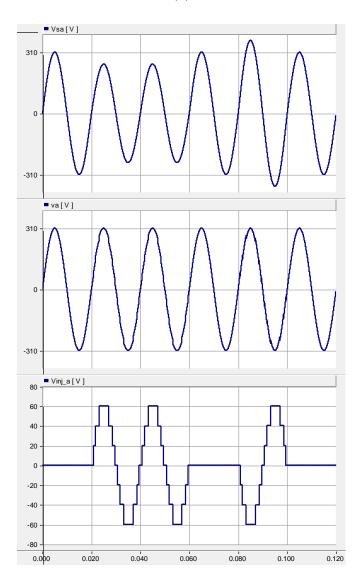

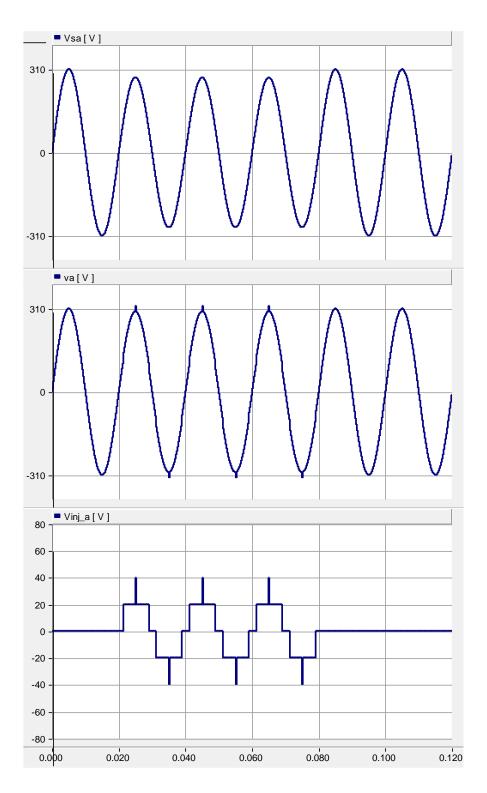

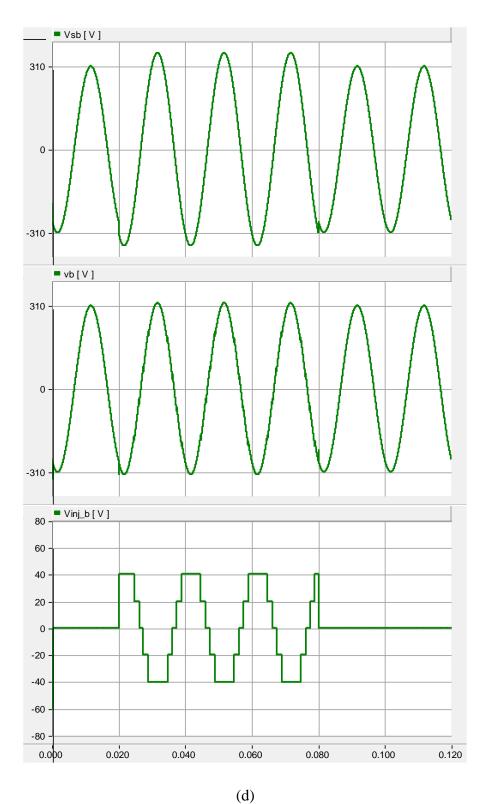

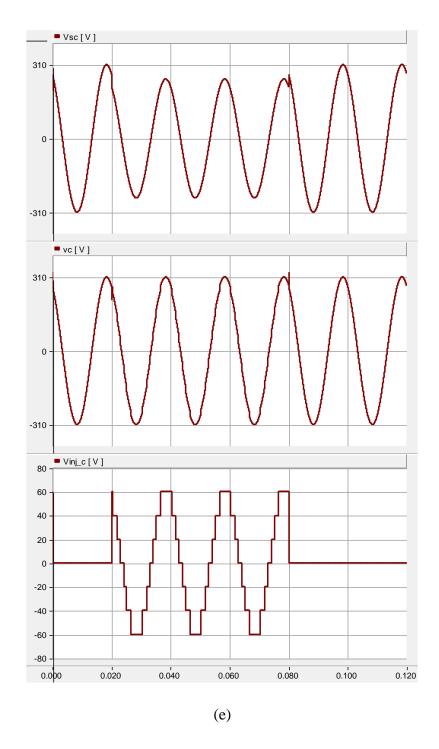

| Figure 5.18: Waveform of input and output voltages of phase A                       | 116 |

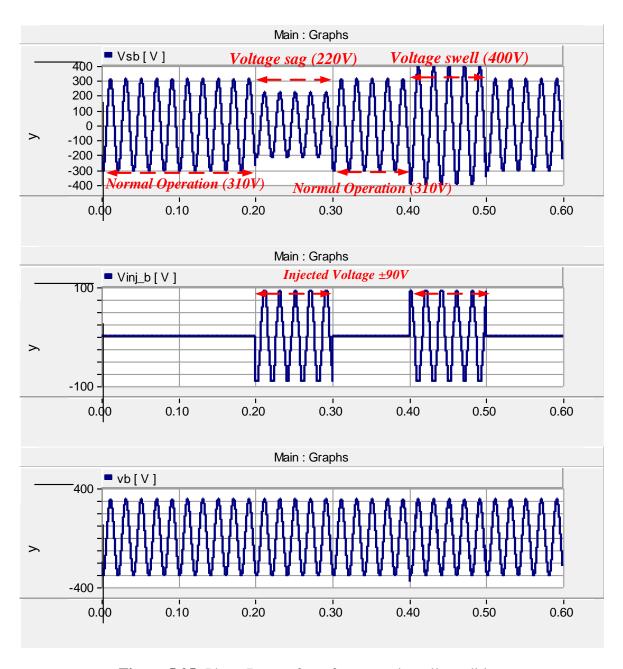

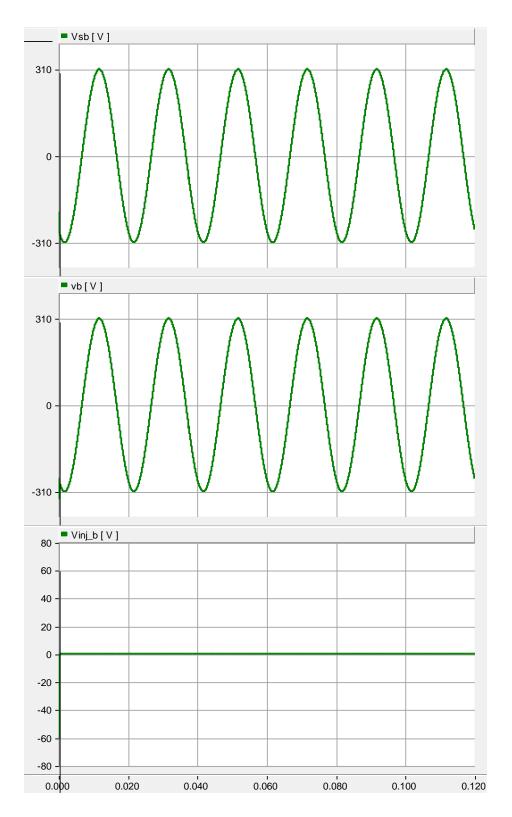

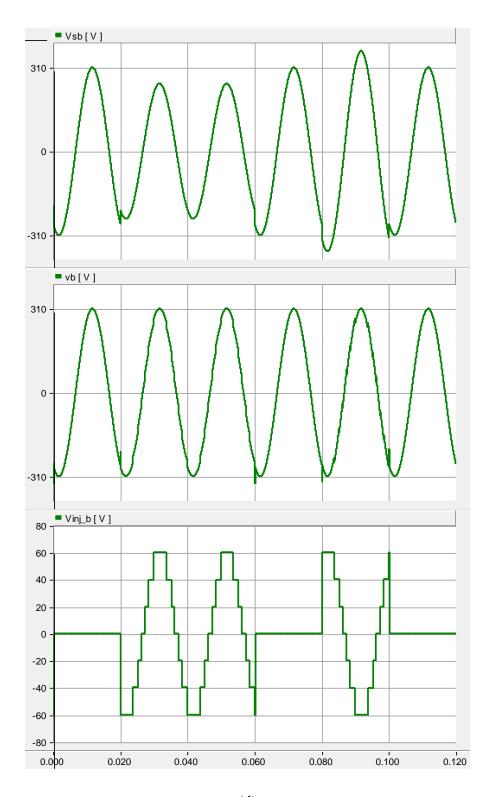

| Figure 5.19: Waveform of input and output voltages of phase B                       | 117 |

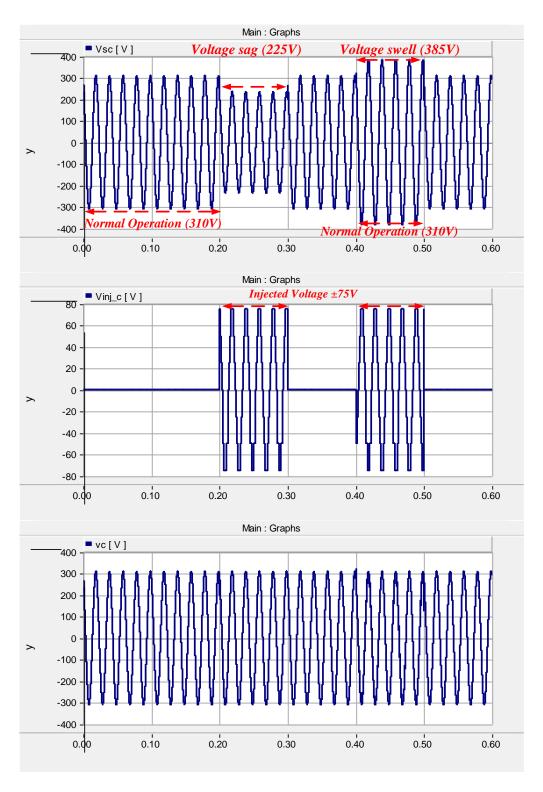

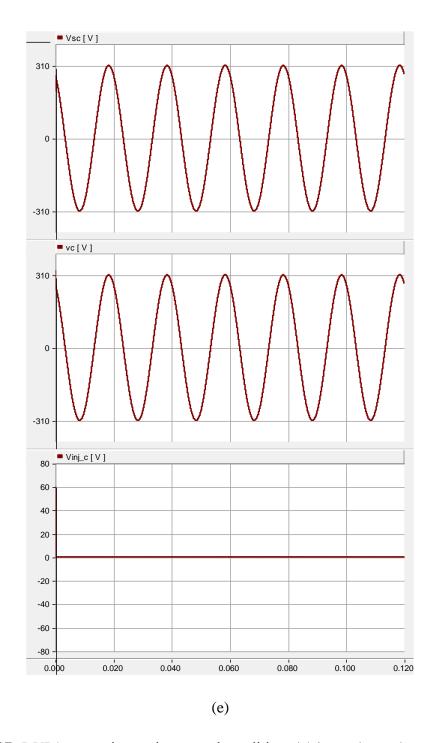

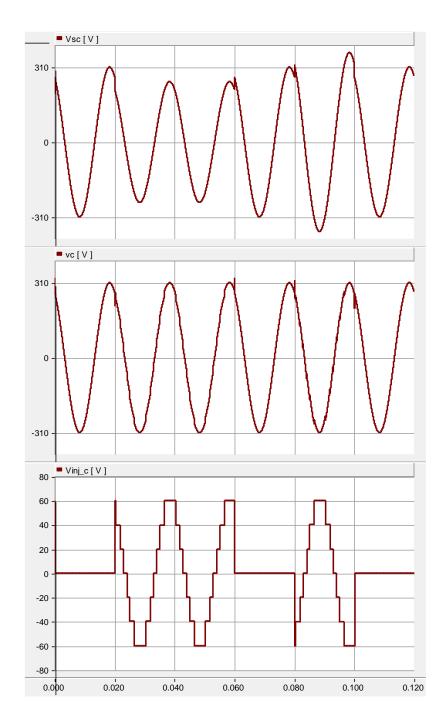

| Figure 5.20: Waveform of input and output voltages of phase C                       | 118 |

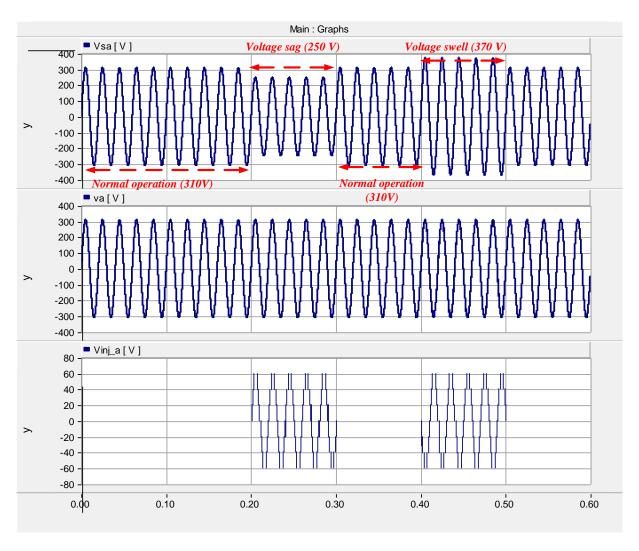

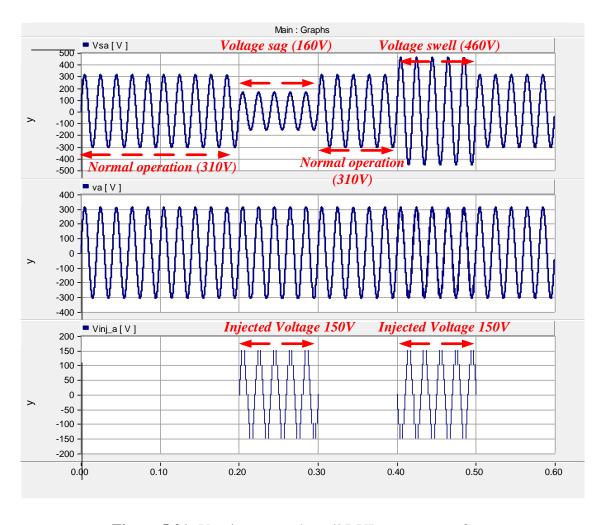

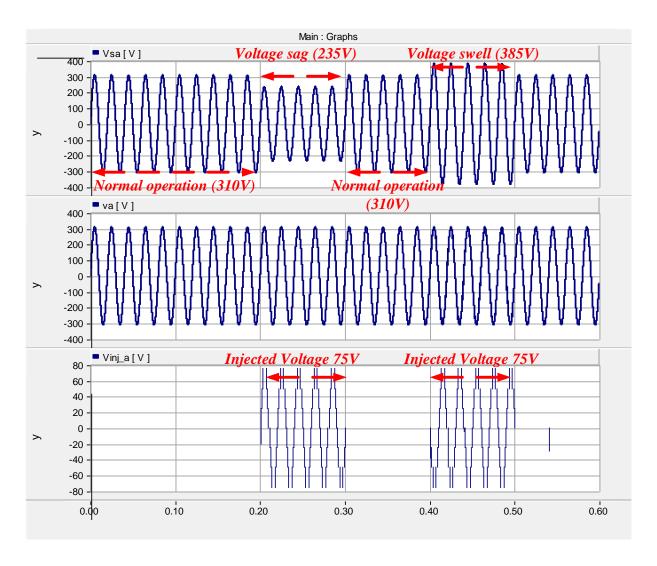

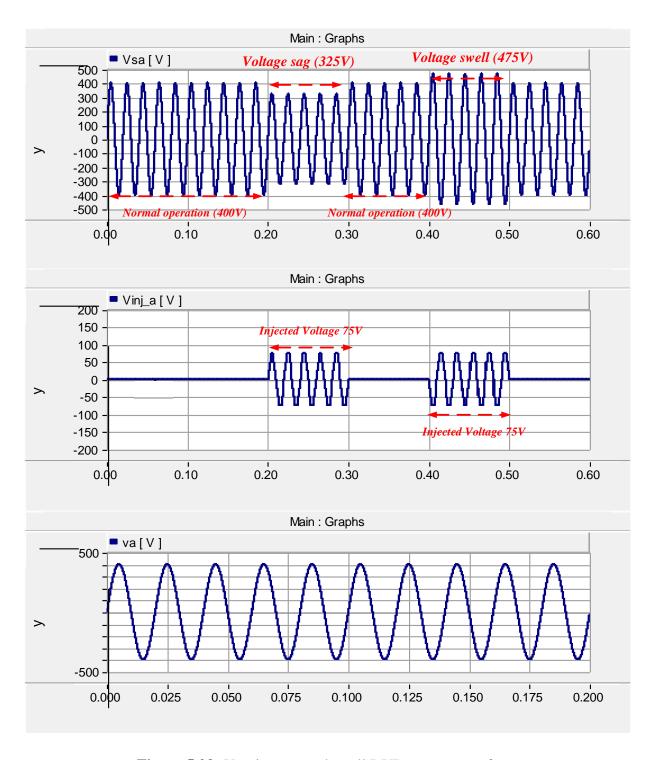

| Figure 5.21: Varying sag and swell DVR output waveform                              | 119 |

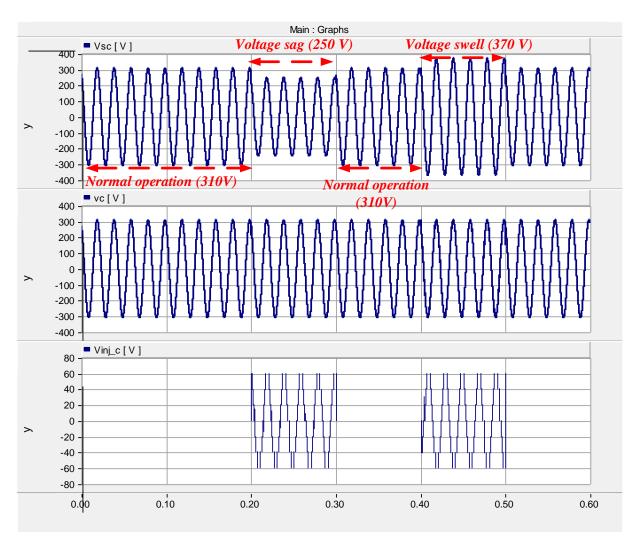

| Figure 5.22: Varying sag and swell DVR output waveform                              | 120 |

| Figure 5.23: Varying sag and swell DVR output waveform                              | 121 |

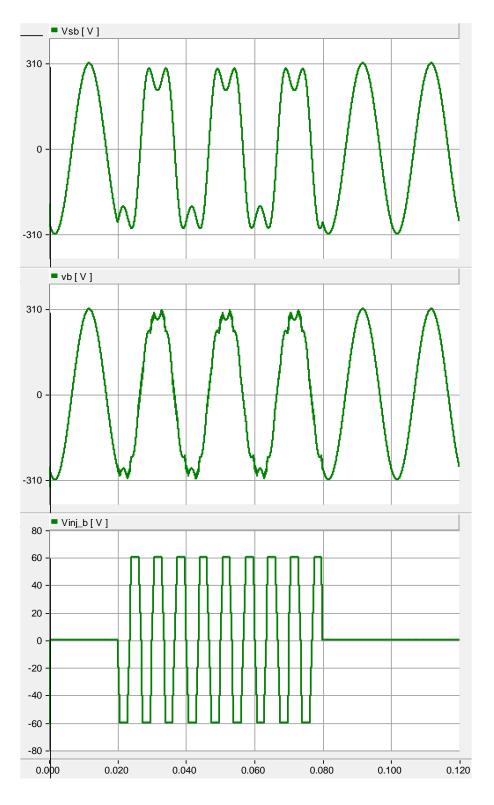

| Figure 5.24: Phase A waveform for sag and swell condition                     | 122 |

|-------------------------------------------------------------------------------|-----|

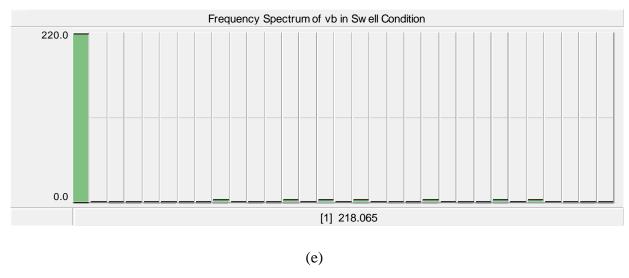

| Figure 5.25: Phase B waveform for sag and swell condition                     | 123 |

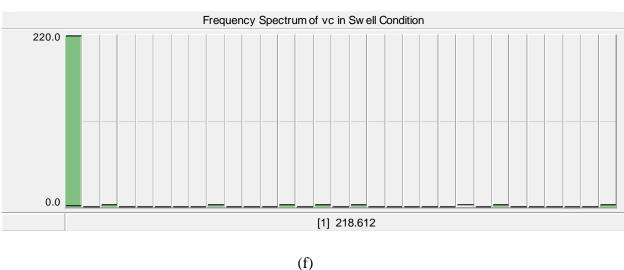

| Figure 5.26: Phase C waveform for sag and swell condition                     | 124 |

| Figure 5.27: DVR's operation under normal condition                           | 129 |

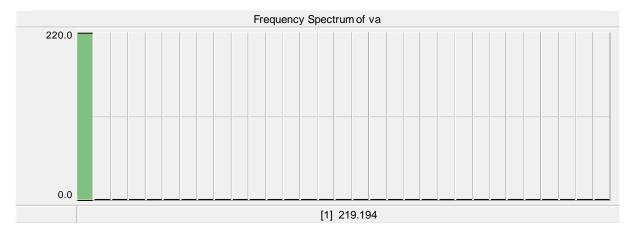

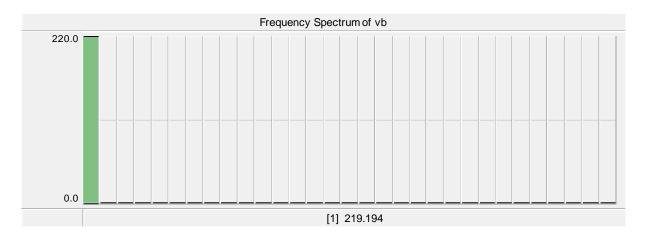

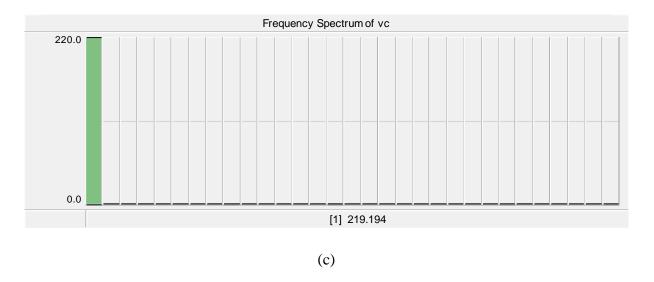

| Figure 5.28: Harmonic spectrum of output three-phase load in normal condition | 131 |

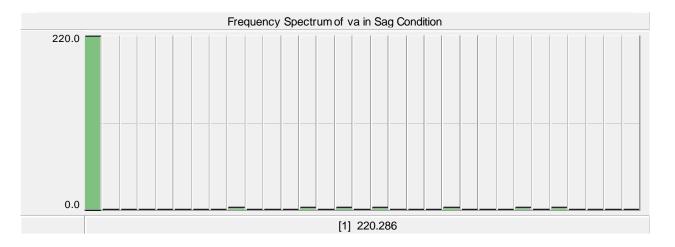

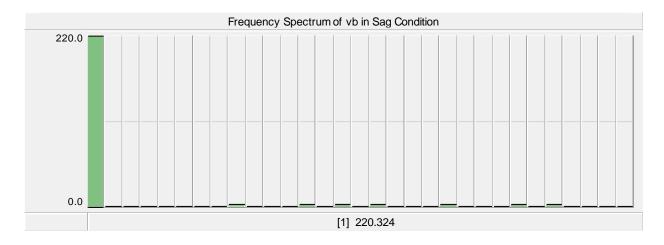

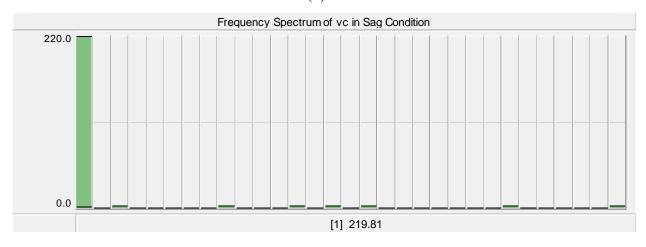

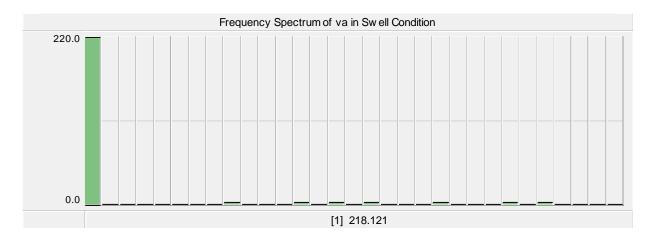

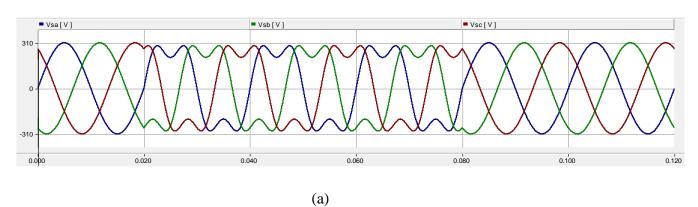

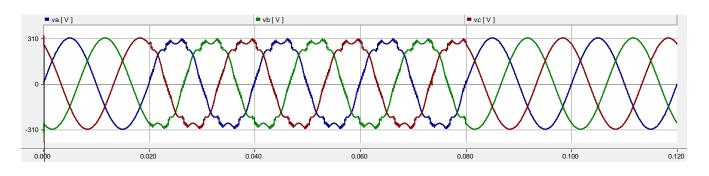

| Figure 5.29: DVR's operation under voltage sag-swell condition                | 135 |

| Figure 5.30: Harmonic spectrum of output three-phase load                     | 138 |

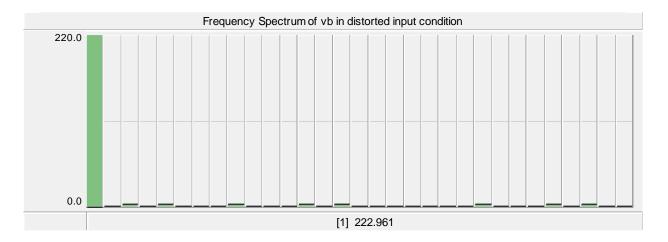

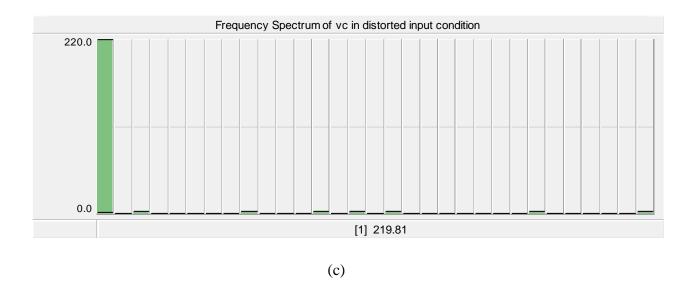

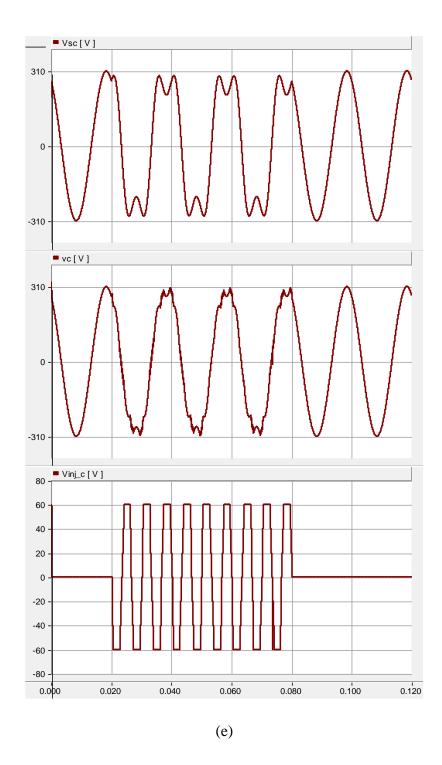

| Figure 5.31: DVR's operation under distorted three-phase input voltage        | 142 |

| Figure 5.32: Harmonic spectrum in unbalanced input voltage condition.         | 144 |

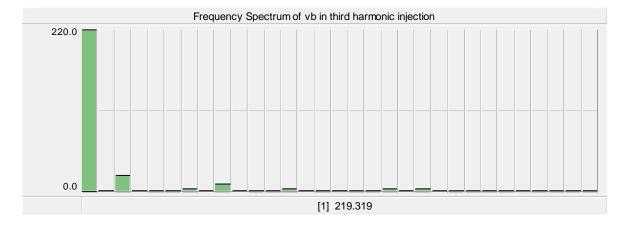

| Figure 5.33: DVR's operation under third harmonic injection                   | 148 |

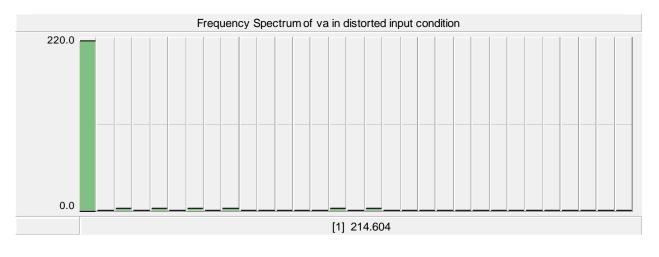

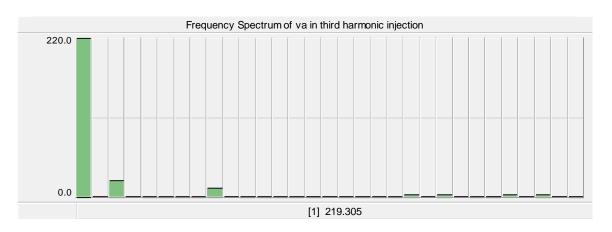

| <b>Figure 5.34:</b> Harmonic spectrum in third harmonic injection case        | 150 |

#### LIST OF TABLES

| <b>Table 2.1:</b> Switching Pattern for 5-levels cascaded converter                | 11  |

|------------------------------------------------------------------------------------|-----|

| Table 2.2: Symmetrical and Asymmetrical converter comparison                       | 14  |

| <b>Table 2.3:</b> Switching pattern for 5-levels flying capacitor inverter         | 16  |

| Table 2.4: Single Phase NPC Inverter Switching Pattern                             | 19  |

| Table 2.5: Analysis of CHB and FC inverters                                        | 21  |

| Table 2.6: Analysis of CHB and NPC inverters                                       | 22  |

| Table 2.7: Comparison study of selected topologies                                 | 44  |

| Table 4.1: Phase switching pattern                                                 | 79  |

| Table 4.2: Gate signal switching states.                                           | 86  |

| <b>Table 4.3:</b> Comparative investigation of proposed topology                   | 90  |

| Table 4.4: Equations of comparison                                                 | 91  |

| Table 4.5: Equations of comparison                                                 | 98  |

| Table 5.1: Simulation and implementation parameters                                | 101 |

| <b>Table 5.2:</b> Parameters used in the simulation to calculate losses            | 109 |

| <b>Table 5.3:</b> Loss distribution results in the simulation when $V_{in} = 20V$  | 109 |

| <b>Table 5.4:</b> Loss distribution results in the simulation when $V_{in} = 50V$  | 109 |

| <b>Table 5.5:</b> Loss distribution results in the simulation when $V_{in} = 100V$ | 110 |

| <b>Table 5.6:</b> Simulation and implementation parameters                         | 111 |

#### LIST OF ABBREVIATIONS

**AC** Alternating Current

**ANPC** Active Neutral Point Clamped

**APOD** Alternate Phase Opposition Disposition

**CD** Carrier Disposition

**DC** Direct Current

**DVC** Dynamic Voltage Compensator

**DVR** Dynamic Voltage Restorer

**ESS** Energy Saving System

**FACTS** Flexible Alternating Current Transmission System

**FC** Flying Capacitor

**FFT** Fast Fourier Transform

**GTO** Gate Turn-off Thyristor

**HB** H-bridge

**HFT** High frequency transformer

**IEC** International Electro-technical Commission

**IEEE** Institute of Electrical and Electronics Engineers

**IGBT** Insulated Gate Bipolar Transistor

LC Inductance Capacitance

**LFT** Line Frequency Transformer

**PCC** Point of Common Coupling

**PD** Phase Disposition

PLL Phase Locked Loop

**POD** Phase Opposition Disposition

**PQ** Power Quality

**PV** Photovoltaic

**PWM** Pulse Width Modulation

**PS** Phase Shift

**SV-PWM** Space Vector Pulse Width Modulation

**SHE** Selective Harmonic Elimination

**SPWM** Sinusoidal Pulse Width Modulation

**STATCOM** Static Synchronous Compensator

**SVC** Static Var Compensator

**TCT** Tap Changing Transformers

**TDVR** Transformerless Dynamic Voltage Restorer

**THD** Total Harmonic Distortion

TCR Thyristor Controlled Reactor

**TSC** Thyristor Switched Capacitor

MLI Multilevel Inverter

MMLI Modular Multilevel Inverter

**MVA** Megavolt Amperes

NPC Neutral Point Clamped

**UPS** Uninterruptible Power Supply

VAR Volt-ampere Reactive

WT Wavelet Transform

**WFFT** Wavelet Fast Fourier Transform

**ZS** Z-Source

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Overview

Application of Power electronic converters has rapidly increased in the past few years because of changes in the dynamics of electric power generation and also the utilization of more energy efficient devices. The world is gradually shifting from the use of fossil fuel for electric power generation to more sustainable methods such as renewable energy sources/resources. Developed countries such as Germany, USA China etc. generates substantial (Gigawatts) amount of electric power from renewable energy sources as a wind and solar. As a policy direction, renewable energy based electric power is increased yearly in these countries, China tops the group with respect to amount of power generated from PV systems. Renewable energy based methods of electric power generation require the use of power electronic converters for conditioning purposes. Generally, power electronic converters encompass the various electric power conditioning circuit such as cycloconverters, inverters, rectifiers and choppers (DC-DC). An inverter is a device composed of power electronic components (mostly semiconductor switches) which is used to change the characteristics of voltage i.e. from direct current voltage into alternating current voltage and also magnitude variations. Inverters are categorized according to several factors such as application; standalone or grid-tied for PV systems, low, medium and high power inverters, phase type; single, three or six phase, type of switching; soft or hard, source type; voltage or current source etc. Multilevel inverter, a class of inverters was first developed over 35 years ago.

Multilevel inverter (MLI) utilizes several number of direct current (DC) voltage sources at the input of the inverter power circuit to generate levels (steps) of voltage waveform at the output. Application of suitable number of dc voltage, semiconductor based switches and an appropriate control scheme will generate stepped output voltage waveforms which is similar to sinusoidal waveforms at the inverter's output. An almost perfect sinusoidal-like waveform has the following advantages; high quality output voltage waveform, minimum total harmonic

distortion (THD), inverter size is greatly reduced because filter size is minimized or eliminated in certain cases, lower switching losses, acceptable electromagnetic interference, less voltage stress on switches and reduced cost of inverter. These attribute makes MLI the preferred alternative when compared to other inverters most especially the two-level inverter. The main component in MLIs is the semiconductor power switch and its driver circuit. The switch type is selected with respect to the voltage medium and the application for which it's to be used. Power switches are either unidirectional or bidirectional from voltage and current point of view. Each unidirectional switch (voltage) is composed of one IGBT connected to a diode in an antiparallel style. Bidirectional switches are built from any of the following configurations; commonemitter, common collector, diode bridge, anti-parallel connected transistors and RB IGBT configuration. Appropriate control scheme is chosen to turn-on and turn-off the switches to generate the desired output waveform. In the absences of filters, semiconductor switches are the major components that determine the cost, size, volume and efficiency of the inverter. Utilizing minimum switch quantity and also lower rated switches reduces the cost, volume and size of inverter thereby increasing the efficiency of inverter. Series and parallel connections of switches provide *new* high rated switches which are commercially unavailable.

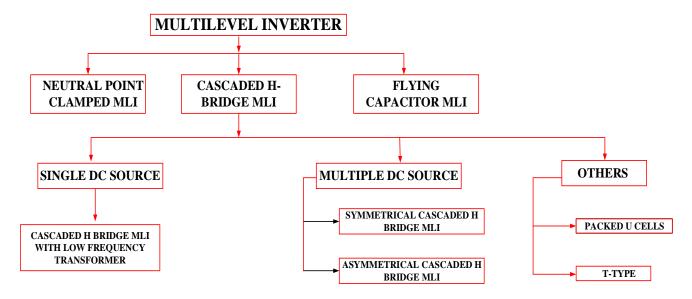

Multilevel inverters are generally classified into three categories, the first in this category is the Cascaded H-bridge MLI (Baker and Bannister 1975). The succeeding topology in this category is the Diode clamped MLI (DC MLI) (Nabae et al., 1981), which uses several diodes for clamping purposes and also series connected capacitors, finally the third member in the MLI category is Flying capacitor MLI (FC MLI) where capacitors float instead of having series connection (Meynard and Foch, 1992). Fig. 1 illustrates this classification and also a further classification based on single and multiple dc sources. Cascaded H-bridge MLI are mostly utilized in industrial applications for integration of renewable energy integrations (Patel and Hoft 1974). This is mainly because the architecture is easily scalable and there's no capacitor voltage-balancing challenges; a major challenge present in the other two topologies (DC MLI and FC MLI). Several topologies of cascaded MLI have been published in literature with the principal of increasing the stepped output voltages which significantly improves the waveform quality and also minimize the overall component quantity especially semiconductor switches.

These variations in topology are categorized into symmetric and asymmetric, with the latter having varying multiple magnitude dc sources. Reduced component count is highly realized with this topology but not suitable for high power utility systems due to lack of modularity and unbalanced voltage distribution. A solution is proposed in (Babaei and Hosseini, 2007) to resolved unbalanced voltage challenges. The symmetric topology has uniform voltage magnitude across the various unit in the cascaded architecture. The major drawback here is the higher component quantity (dc sources and switches) required for high number of stepped output voltage, however it boast of modularity, uncomplicated control scheme and equal voltage magnitudes.

Figure 1.1: Classification of multilevel inverter

Voltage disturbance, made-up of voltage dip, voltage swell, flickers, unbalances and harmonics is one of the frequently faced power quality (PQ) problems by utility providers (Elnady et al.,2005). Voltage disturbances when not appropriately mitigated will lead to the destruction of critical and sensitive loads located in hospitals, factories and office buildings (Jimichi et al., 2008), also it can cause the disruption of production lines which may result in huge financial loss or possibly the loss of vital information (Chan and Milanović 2015; Trindade et al., 2013; IEEE, 2005). The demand for sensitive load protection is on the rise likewise is the usage of

devices responsible for the pollution of distribution lines. The definition of voltage dip according IEEE 1159 and 1346 standards is a reduction in the RMS (root mean square) ac voltage from 10% to 90% of nominal voltage at the utility's frequency for a period of half cycle to 60 seconds (IEEE, 1995, 1998). An abrupt connection of large loads, start-up of large rated induction motors and short circuit faults are major causes of voltage swell (Farhadi-Kangarlu et al., 2017) Also voltage dip can be defined according to IEC 61000-2-1 standards by two characteristics; an abrupt drop and recovery of voltage in power systems for a period lasting not more than half cycle to 60 seconds. Voltage swell is also defined according to IEEE benchmark as a rise in the RMS source voltage from 110% to 180% of the nominal voltage at the utility's frequency for a period not exceeding half cycle to 60 seconds. Disconnecting large loads such as inductive loads, switching of large capacitors and energizing of heavy capacitor banks are the major causes of voltage swell (Babaei and Farhadi Kangarlu 2009). Some effects of voltage swell are breakdown of industrial devices as a result of tripping and overheating of relays, surge arresters and ac motors (Bollen 2000; Arrillaga et al., 2000). Contamination of power lines with harmonics is a drawback for sensitive loads since their control relies on two factors; maximum value and zero crossing of the source voltage. These factors are affected by harmonic distortion (Awad 2004).

Different solutions have been proposed to resolve effects of voltage disturbances on sensitive loads. Custom power devices have been the most desired solutions to mitigate against voltage disturbances due to their effectiveness, fast response and flexibility. Custom power devices are power electronic based compensators and are classified into three categories; series compensators, parallel compensators and series-parallel compensators (Kazmierkowski 2007; Ghosh and Ledwich 2002). Series compensators which encompasses Dynamic Voltage Restorers (DVR), Dynamic Voltage Compensators (DVC) and Static Series Compensators (SCC) are considered cost effective way of resolving voltage disturbances. These compensators may vary from each other with respect to purpose and control mechanism but are similar in terms of power circuit structure and principles of operation. Other devices used in voltage sag and swell corrections are STATCOM (static compensators), tap changing transformers, UPS

(uninterruptable power supply) and flywheel (Najafi and Yatim 2011). The first installed DVR is located in a rug manufacturing company in North Carolina (Woodley et al., 1999).

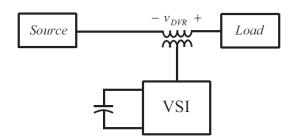

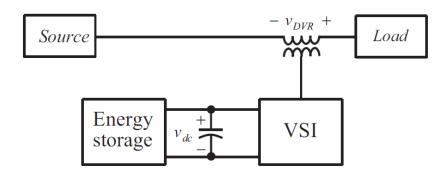

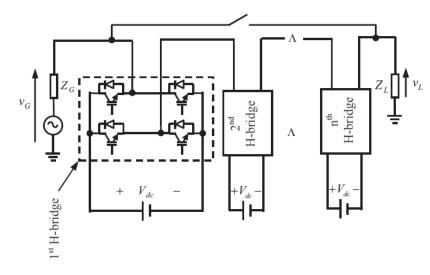

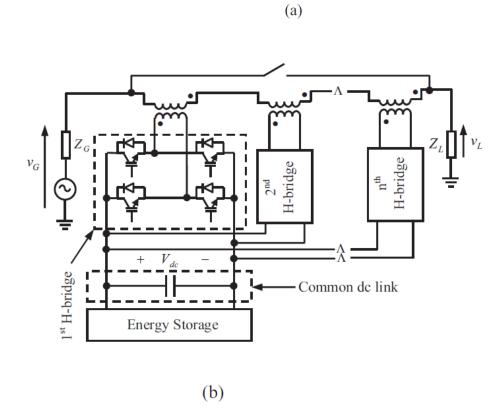

Dynamic voltage restorer is a power electronic based device whose principal function is to protect critical and sensitive loads from voltage disturbances emanating from the supply side. DVRs are coupled to the distribution line via series connection and has the potential of absorbing and generating reactive and real powers. With respect to energy storage systems (ESS) DVRs are categorized into these groups: with ESS and without ESS. DVR topologies with ESS are sub-divided into capacitor based topologies and an external ESS. DVR topologies without ESS also subdivided into two; shunt based topologies and ac-ac based topologies. The shunt based topologies are also subdivided into source side connection and load side connection.

#### 1.2 Problem Statement

Power electronic converter are regarded as integral component in all electric power generation systems (fossil fuel and renewable energy systems) and electric power conversion systems. Their usefulness is undoubtedly very important however, they are bedeviled with a number of drawback which are being addressed in both industry and academia by researchers. These drawbacks are high inverter cost, huge installation area as a result of increased size and volume, high inverter losses and reduced efficiency. The above mentioned drawbacks are directly caused by high component quantity most especially power switches and dc sources. Reducing the quantity of semiconductor switches and dc sources significantly improves or eliminates these drawbacks. The most common method of designing three-phase MLI is to replicate one singlephase three times to achieve three-phase MLI systems. This methodology increases the overall component quantity, a phenomenon that we wish to eliminate. A novel methodology will be implemented to reduce the overall component count, most importantly dc voltage source count. The use of power electronic gadgets in electric power generation, transmission and distribution has brought to the fore the problem of power quality issues such as voltage sag and swell, spikes and harmonics. These power quality related disturbances cause destruction of sensitive loads leading to huge financial burden to the consumer and utility provider.

#### 1.3 The Aim of the Thesis

The aim of this research is to significantly reduce or eliminate the limitations enumerated above (in section 1.2). This is achieved by proposing a novel developed three-phase multilevel inverter composed of less component quantity i.e. semiconductor power switches and dc sources. The proposed three-phase topology has 18 power switches and 4 dc sources. "Extension technique" is applied to the single-phase topology to derive three-phase structure. This technique reduces the overall component count which leads to an improved three-phase ML inverter with less cost, minimum installation area, reduced inverter loss hence improved efficiency and finally highly reliable inverter. So as to make the proposed topology suitable for DVR (dynamic voltage restorer) applications, three single-phase transformers are connected to the topology. Also the proposed topology is capable of providing galvanic isolation because of the transformers.

#### 1.4 The Importance of the Thesis

Because power electronic converters (inverters) are integral components of power generation and conversion systems, it's imperative to significantly minimize or eliminate limitations which bug these inverters. In view of this, the proposed three-phase ML inverter has the following merits:

- Reduced dc source count

- Reduced inverter size

- Reduced inverter volume

- Minimum area of installation

- Less quantity of semiconductor switches

- Improved reliability

- Reduced inverter cost

On the other hand, applying the proposed three-phase ML inverter in DVR systems for voltage compensations will generally lead to protection of sensitive loads in factories, hospitals etc. Generally, some advantages of DVR systems are reduce cost of replacing damaged devices, lifesaving and reduced production losses.

#### 1.5 Limitation of the Study

Generally, a number of limitations were encountered during the implementation of this research, significant amongst these limitations was the travel restrictions due to COVID 19. However, these limitations were overcome by the guidance and support of my supervisor, chairman and course advisor of electrical and electronics engineering department.

#### 1.6 Overview of the Thesis

This section describes the arrangement of the thesis. This work of research is segmented into the following chapters:

Chapter 1: introduction

- Introduction

- Problem Statement

- Aim of the thesis

- The importance of the thesis

- Limitations of the study

- Overview of the thesis

Chapter 2: literature review of multilevel inverters

- Introduction

- Cascaded H-Bridge MLI

- Flying Capacitor MLI

- Neutral Point Clamped MLI

- Comparative analysis of Cascaded H-Bridge and Flying Capacitor

- Comparative analysis of Cascaded H-Bridge and Neutral Point Clamped

- Application of MLI

- Cascaded MLI Topologies

- MLI Control Techniques

- Conclusion

Chapter 3: investigation of multilevel inverter based dynamic voltage restorers.

- Introduction

- DVR Components

- DVR Operation Range

- DVR Classification

- DVR Control System

- Application of DVR

- DVR Topologies

- Conclusion

Chapter 4: proposed three-phase mli based DVR

- Proposed Three-phase Multilevel Inverter

- Blocking Voltage

- Calculation of Inverter Power Losses

- Conduction Power Losses

- Switching Power Losses

- Comparative Investigation

- Conclusion

Chapter 5: simulation and experimental results

- Introduction

- Simulation Results

- Experimental Results

- DVR Simulation

- Conclusion

Chapter 6: conclusion

#### CHAPTER 2

#### LITERATURE REVIEW OF MULTILEVEL INVERTERS

#### 2.1 Introduction

Multilevel inverters (MLI) are inverters that produce several levels of load voltages by employing single or multiple dc source voltage at the input side. The concept of multilevel inverter was proposed over 35 years ago. Diode Clamped MLI was the first functional multilevel inverter introduced in 1980 by (Nabae et al., 1981). Basically, any inverter capable of producing three or more levels of output voltage is considered to be a multilevel inverter. The conventional two-level inverter precedes the multilevel inverter. MLIs are the appropriate devices for high voltage and high power applications because the synthesized output waveforms contain acceptable harmonic spectrum, also lower rated switches are used to synthesize high voltages (Manjrekar et al., 1999). Generally, multilevel inverters produce better quality output waveforms when the number of output levels is increased. This characteristic makes the MLI topology a better alternative to the two level inverter. Higher levels of output waveforms mean the magnitude of the output step voltages are small hence power switches of lower ratings are utilized. Lower rated switches reduce power losses hence increases the efficiency of the inverter. Other advantages of MLI are minimum harmonic content, reduced dv/dt stress and application of low speed semiconductor switches.

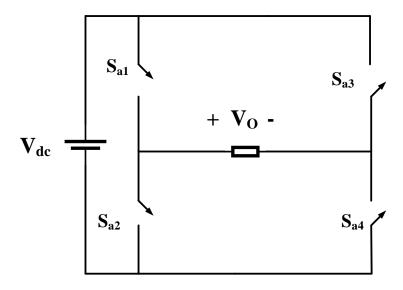

#### 2.2 Cascaded H-Bridge

Cascaded H-bridge inverter is derived by series connection of two or more H-bridge structures. Each H-bridge inverter (cell) in the series connection has a separate dc-link or source. The number of voltage levels that can be generated by the cascaded structure is determined by the number of H-bridges in the cascaded structure and the magnitude of the dc-links. For evenly distributed dc-link magnitudes, the output voltage level is computed by 2n + 1 where n + 1 where n

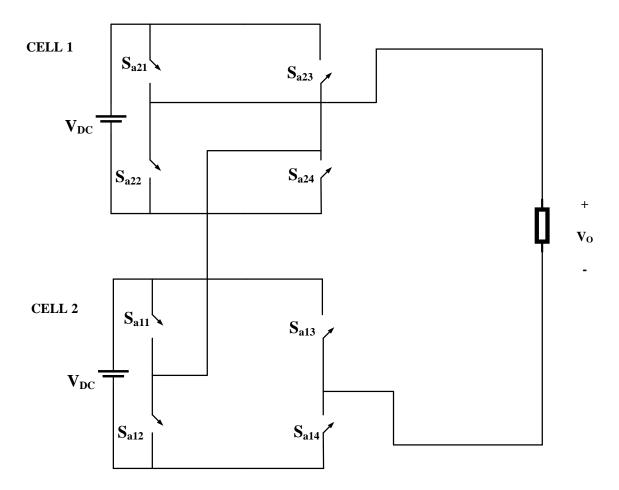

simplicity of the H-bridge topology makes it convenient for deriving a cascaded topology unlike other types of multilevel inverters. An example of a cascaded topology made of two H-bridge cells is shown in Fig. 2.1. The switching pattern of this cascaded structure used in generating the desired output voltage  $(V_0)$  is shown in Table 2.1. E is the input voltage for each cell. It should however be noted that not all switching states in Table 1 are required. Switching states which produce short circuit of switches and dc-link as well as open circuit of the load should be avoided.

Figure 2.1: 5-levels Cascaded H bridge inverter

$S_a21$  to  $S_a24$  are the switches for "cell 1" H-bridge where the input and output voltages are  $V_{DC}$  and  $V_A$  respectively.  $S_a11$  to  $S_a14$  are the switches for "Cell 2" H-bridge where the input and output voltages are  $V_{DC}$  and  $V_N$  respectively. Pulsewidth modulation control techniques can be

applied to the cascaded H-bridge multilevel converter. Some advantages of the cascaded converter are: less number of components is required, snubber circuit not needed because soft switching is applicable, each layout has same number of component making it simple to package, high power-high voltage application, and the disadvantage of the cascaded multilevel inverter lies in the separate dc source required and as such makes gives the cascaded converter limited application (Lai and Peng 1996), a new topology was presented in (Soto et al., 2003) where a single dc source was used to developed 5-levels cascaded H-bridge inverter by utilizing interface inductors between the series chain.

**Table 2.1**: Switching Pattern for 5-levels cascaded converter. (Chiasson et al., 2003).

| Sa21 | Sa23 | Sa22 | Sa24 | Sa11 | Sa13 | Sa12 | Sa14 | VA          | $V_B$             | Vo                 |

|------|------|------|------|------|------|------|------|-------------|-------------------|--------------------|

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | $+V_{DC}$   | $+ V_{DC}$        | $+2V_{DC}$         |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | $+\ V_{DC}$ | 0                 | $+ \ V_{DC}$       |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | $+\ V_{DC}$ | 0                 | $+\;V_{DC}$        |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | $+\ V_{DC}$ | - $V_{DC}$        | 0                  |

| 1    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0           | $+\ V_{DC}$       | $+ \ V_{DC}$       |

| 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0           | 0                 | 0                  |

| 1    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0           | 0                 | 0                  |

| 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0           | - $V_{DC}$        | - V <sub>DC</sub>  |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0           | $+\ V_{DC}$       | $+ \ V_{DC}$       |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0           | 0                 | 0                  |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0           | 0                 | 0                  |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0           | - V <sub>DC</sub> | - V <sub>DC</sub>  |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | - $V_{DC}$  | $+\ V_{DC}$       | 0                  |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | - $V_{DC}$  | 0                 | - V <sub>DC</sub>  |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | - $V_{DC}$  | 0                 | - $V_{DC}$         |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | - $V_{DC}$  | - $V_{DC}$        | -2 V <sub>DC</sub> |

#### 2.2.1 Symmetrical and Asymmetrical CHB

Cascaded multilevel inverters are categorized into two types, namely symmetrical cascaded multilevel inverter and asymmetrical cascaded multilevel inverter. It has already been established that cascaded multilevel inverter is the series connection of multiple H-bridge inverters. Basically, the difference between the two types of cascaded multilevel inverter lies in the magnitude of dc voltage at the input. When the magnitude of dc voltage for all H-bridges in the series connection are equal, then the multilevel inverter is known as symmetrical cascaded multilevel inverter.

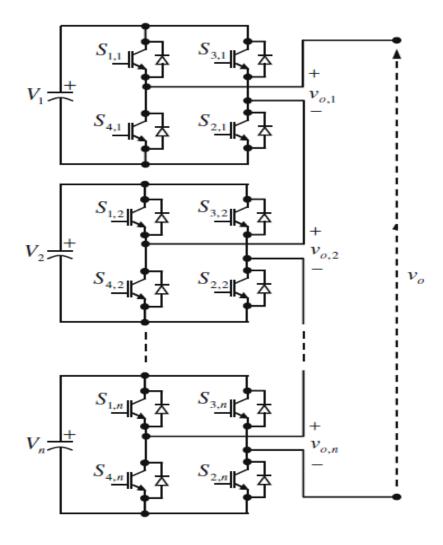

**Figure 2.2:** *n*-level cascaded H-Bridge converter

However, if there's a difference in the magnitude of the dc voltage of at least one H-bridge in the series chain, then the multilevel is known as asymmetrical cascaded multilevel inverter (Manjrekar and Lipo 1998; Schibli 2000; Rufer et al., 1999). Although there are other factors which differentiate symmetrical and asymmetrical converters; these factors will be explained in later sections, our considerations now will be on the magnitude of the input dc voltage. Based on the magnitude of the input dc voltage, symmetrical and asymmetrical inverters cannot be limited to cascaded H-bridge inverters only as symmetrical and asymmetrical diode clamped inverters have been presented in (Song-Manguelle and Rufer 2001).

Fig. 2.2 shows limitless level (n-level) of cascaded multilevel converter. For symmetrical cascaded multilevel inverter, the number of levels or steps that can be generated at the output is expressed by equation (2.1) where n in the equation is the number of H-Bridge modules in the series connection.

Number of steps

$$(n) = 2n + 1$$

(2.1)

For example, if 3 H-bridge modules are connected in series to form cascaded bridge inverter, then the maximum steps that can be generated at the output is 7-level for symmetrical H-bridge provided  $V_1 = V_2 = V_3$  where  $V_1$ ,  $V_2$ , and  $V_3$  represents the input voltage for the individual H-bridge modules in the series connection. Also the maximum voltage that can be generated by 7-level cascaded symmetrical multilevel is given by equation (2.2), where  $V_{dc}$  is the voltage across any H-bridge in the series connection.

$$Vmax = nVdc (2.2)$$

As stated above, if the voltage value ( $V_{dc}$ ) of any H-bridge module in the series connection is different i.e.  $V_1 \neq V_2 = V_3$ , the series connection is classified as asymmetrical; two types exist for the asymmetrical converter; *binary* and *trinary* cascaded asymmetrical inverter. Table 2.2 shows the difference between symmetrical and asymmetrical converter with respect to no of output levels, maximum output voltage, number of input voltage and number of semiconductor switches required (Babaei et al., 2007; Babaei and Hosseini 2008). The difference between binary and trinary asymmetrical multilevel inverter is the number of output voltage levels and

the ratio of dc voltage between H-bridges in the series chain. In the binary cascaded H-bridge multilevel inverter, the input voltage ratio is 1:2 whiles its 1:3 for the trinary cascaded H-bridge multilevel inverter, these ratios are valid provided they have the same number of input voltage and H-bridges in the series connection.

If two H-bridge modules are cascaded for asymmetrical multilevel inverter, the number of output voltage steps will be 7-level and 9-level for *binary* and *trinary* asymmetrical multilevel inverter respectively. IGBTs and diodes are the principal components in all multilevel inverters, asymmetrical cascaded have equal quantity of switches but are able to generate more levels of load voltage. from the perspective of technical and economic significance of power dissipation, using lower voltage rated switches reduces the cost and losses. Losses which occur in converters because of power semiconductor switches are categorized into three set; switching losses, off-state losses and conduction losses (Aghdam and Fathi 2005).

**Table 2.2:** Symmetrical and Asymmetrical converter comparison

|                        | Symmetrical | Asymmetrical Inverter |                     |  |  |

|------------------------|-------------|-----------------------|---------------------|--|--|

|                        | Inverter    | Binary                | Trinary             |  |  |

| Number of output steps | 2n + 1      | $2^{n+1}-1$           | 3 <sup>n</sup>      |  |  |

| Number of dc sources   | n           | n                     | n                   |  |  |

| Number of switches     | 4n          | 4n                    | 4n                  |  |  |

| Maximum output voltage | n           | 2n - 1                | $\frac{3^{n}-1}{2}$ |  |  |

One major disadvantage of the cascaded H-bridge multilevel inverter is the huge number of semiconductor power devices required as the number of output steps are increased; this results in increased number of gate driver circuits and protection circuits thus increased cost of device and maintenance cost. Asymmetrical cascaded H-bridge inverter has the advantage of increased number of output steps when compared to the symmetrical H-bridge which corresponds to small

device size, reduced device cost, and easy control technique. Despite the considerable advantages of asymmetrical multilevel inverter over symmetrical multilevel inverter, some disadvantages exist as well. Difference in magnitude of input voltage results in differences in the life-span of the voltage sources therefore increased cost due to increased battery evaluation and substitution, power losses increases due to higher voltage rated semiconductor devices. To solve the problem of high number of semiconductor devices required in the cascaded multilevel inverter, several new topologies in (Babaei et al., 2007; Babaei and Hosseini 2008) have been introduced which can produce higher voltage output steps with limited number of semiconductor switches.

#### 2.3 Flying Capacitor Multilevel Inverter

A 5-level Flying capacitor single phase inverter is shown by Fig. 2.3. In the Flying capacitor inverter which is also known as capacitor clamped inverter, clamping diodes are not required which is an added impetus when compared to NPC inverter, also one dc source is enough because of switching redundancy (Lai and Peng 1996). Each capacitor in a different leg is charged to a different value from other capacitors, and the capacitors which are connected in series determine the level of output voltage. The series connection of the capacitors as shown in Fig. 2.3 determines the level of  $V_{dc}$  output from the point of clamping. The switching pattern for the Flying capacitor converter is shown by Table 2.3. The use of multilevel inverters means that ac voltage in power systems could be increased without the utilization of transformers and lower order harmonics can be cancelled which means reduced component cost because the ac inductance size is greatly minimized. The Flying capacitor converter has numerous advantages such as: minimization of harmonics thus cost saving because the need for filters are eliminated, reduced number of diodes when compared to NPC, suitable for high voltage transmission system because reactive power can be controlled, capacitors serve as storage units, phase redundancy in Flying capacitor over line to line redundancy in the NPC inverter. Disadvantages are: lager number of capacitors are required, in high power systems efficiency is reduced because switching losses are increased thus control of the inverter becomes complex (Lai and Peng 1996).

**Table 2.3:** Switching pattern for 5-level flying capacitor inverter

| Output Voltage            | S <sub>a1</sub> | S <sub>a2</sub> | S <sub>a</sub> 3 | Sa4 | Sa'4 | Sa'3 | Sa'2 | Sa'1 |

|---------------------------|-----------------|-----------------|------------------|-----|------|------|------|------|

| $V_5 = V_{dc}$            | 1               | 1               | 1                | 1   | 0    | 0    | 0    | 0    |

| $V_4 = \frac{3}{4}V_{dc}$ | 1               | 1               | 1                | 0   | 1    | 0    | 0    | 0    |

| $V_3 = \frac{1}{2}V_{dc}$ | 1               | 1               | 0                | 0   | 1    | 1    | 0    | 0    |

| $V_2 = \frac{1}{4}V_{dc}$ | 1               | 0               | 0                | 0   | 1    | 1    | 1    | 0    |

| $V_1 = 0$                 | 0               | 0               | 0                | 0   | 1    | 1    | 1    | 1    |

Figure 2.3: Five level flying capacitor converter

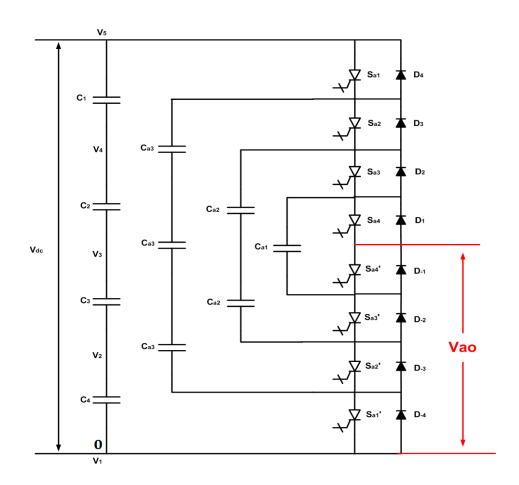

#### 2.4 Neutral Point Clamped Multilevel Inverter

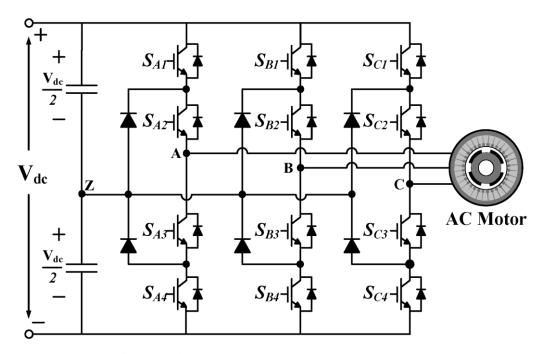

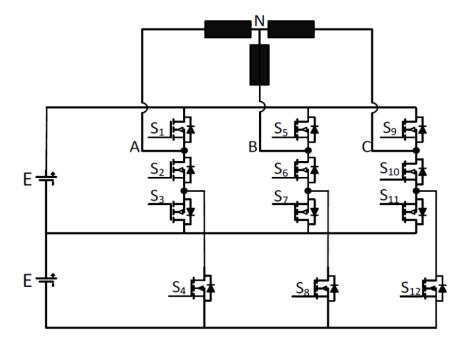

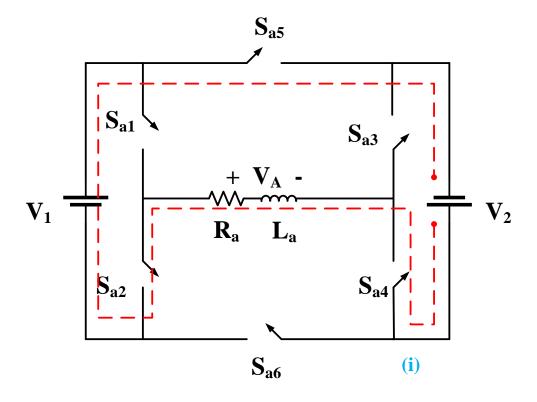

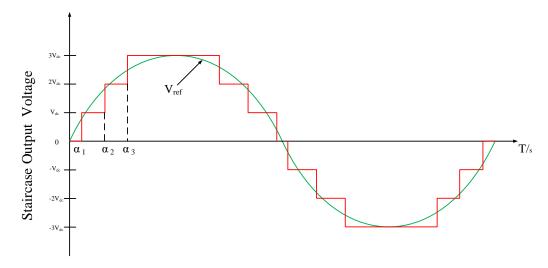

Another type of multilevel inverter which has contributed significantly to the development of quality output waveform is the Neutral Point Clamped Inverter (NPC). Fig. 2.4 shows the circuit diagram of the NPC inverter for three-phase topology, the neutral point of the circuit with respect to direct voltage source is the zero (0) point. There are two types of switches in the circuit, main switches and auxiliary switches. The main transistor switches have the responsibility or function of pulse width modulation controller and the purpose of the auxiliary transistor switches is to clamp the potentials of the output terminals to the zero point with the aid of diodes D<sub>1</sub> to D<sub>6</sub>. The main switches are S<sub>a1</sub>, S<sub>a4</sub>, S<sub>b1</sub>, S<sub>b4</sub>, S<sub>c1</sub>, S<sub>c4</sub> (upper and bottom horizontal switches) and the auxiliary switches are S<sub>a2</sub>, S<sub>a3</sub>, S<sub>b2</sub>, S<sub>b3</sub>, S<sub>c2</sub>, and S<sub>c3</sub>. All conventional pulsewidth modulation control techniques can easily be applied to this inverter which makes NPC-PWM inverter versatile in terms of control methodology (Nabae et al., 1981).

The NPC inverter shown in Fig. 2.4 is a three phase 5-level inverter; it's possible to generate line-to-line voltage between the phases available and also possible to generate phase voltage for either phases a, b or c. The switching pattern for a-phase is similar to the switching pattern of Table 2.4. Several other topologies of neutral point clamped inverter have been developed; these topologies are derived by changing the structure of the conventional NPC. Examples of these newer NPC inverters are:

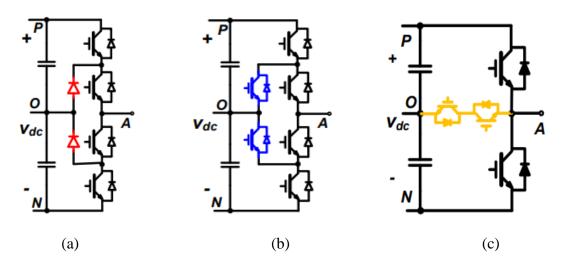

- a. Active NPC

- b. T-Type NPC

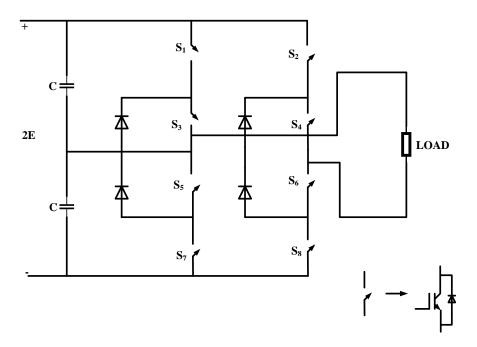

The active NPC inverter is developed by substituting the clamping diode in the NPC inverter with an active switch. The T-type NPC also known as switch clamp is derived by connecting the output point together with the neutral point via bidirectional switches. Figure 2.5a, 2.5b and 2.5c shows the ANPC and T-type NPC derived from 3-level diode clamped inverter. Single phase NPC-PWM inverter is shown in Fig. 2.6 (Nabae et al., 1981). The single NPC inverter is described as 3-state NPC inverter because of its ability to generate 3 different dc voltages at the output; 0, E, and 2E. As explained in the 3-phase NPC inverter, switches S<sub>1</sub>, S<sub>2</sub>, S<sub>7</sub>, and S<sub>8</sub> are

the main switches and switches  $S_3$ ,  $S_4$ ,  $S_5$ , and  $S_6$  are the auxiliary switches; their function is to complement the main switches to derive desired output voltage. Table 2.4 shows the switching pattern for the single phase NPC inverter.

Figure 2.4: Neutral point clamped inverter

Figure 2.5: (a) NPC (b) ANPC (c) T-type NPC

During any switching pattern, the maximum blocking voltage across each semiconductor switches must be equivalent to half the dc supply. Proper controlling of the inverter to avoid abrupt alterations between E and -E will produce lower harmonics and prevent simultaneous turning on and off of two switches. Some advantages of NPC are: harmonic elimination at higher levels, higher efficiency due to fundamental frequency switching, control of reactive power, simple control techniques and the demerits are: large number of diodes are required for higher levels, real power flow control is difficult for individual converters (Lai and Peng 1996).

**Table 2.4:** Single Phase NPC Inverter Switching Pattern

| Switches |       |       |       |       |                |  |  |

|----------|-------|-------|-------|-------|----------------|--|--|

| State    | $S_1$ | $S_7$ | $S_2$ | $S_8$ | Output Voltage |  |  |

| I        | 1     | 0     | 0     | 1     | 2E             |  |  |

|          | 1     | 0     | 0     | 0     |                |  |  |

| II       | 0     | 0     | 0     | 1     | E              |  |  |

|          | 1     | 0     | 1     | 0     |                |  |  |

| III      | 0     | 0     | 0     | 0     | 0              |  |  |

|          | 0     | 1     | 0     | 1     | 0              |  |  |

|          | 0     | 0     | 1     | 0     |                |  |  |

| IV       | 0     | 1     | 0     | 0     | -E             |  |  |

| V        | 0     | 1     | 1     | 0     | -2E            |  |  |

Figure 2.6: Single phase NPC- PWM inverter

## 2.5 Comparative Analysis of Cascaded H-Bridge and Flying Capacitor.

Although the cascaded H-bridge and Flying capacitor inverters are all categories of multilevel inverters; there are a couple of differences between them; these differences can be mainly traced to the circuit structure. Fig. 2.1 and Fig. 2.3 shows the circuit diagrams of the two inverters having 5-level output voltage, these inverter circuits are that of cascaded H-bridge and Flying capacitor inverters respectively. The number of diodes and power switches in both circuits are equal but the Flying capacitor has 10 capacitors more than cascaded H-bridge. From the power source pint of view, the cascaded H-bridge inverter is made up two dc source and the Flying capacitor inverter has only one dc source. Capacitor voltage levels in the latter topology can be balanced by phase redundancies technique. The power ratings of power switches in the Flying capacitor inverters are different. This is because different levels of power ratings are applied to different switches but in the case of the cascaded H-bridge the voltage ratings are the same, these differences cause difficulties in the blocking voltage analysis of the Flying capacitor

inverter. The blocking voltage or standing voltage of converters have become an important point of reference when determining the reliability of the converter. Standing voltage is directly linked to the cost, size and efficiency of any proposed converter (Babaei et al., 2014). Control of the Flying capacitor is complicated because each leg has different voltage ratings of capacitors hence different voltage levels; discharging and discharging period becomes problematic. The cascaded H-bridge inverter control is less problematic as compared to Flying capacitor inverter; the same number of components in the first cell/module is repeated in the next cell/module hence its control is simple, also no capacitors required in the main topology structure. Due to the large number of capacitors required in the Flying capacitor topology, the structure of the system becomes bulky and heavy, not to talk about increased cost and reduced efficiency. Increasing the output voltage level will result in uneven package/layout but the cascaded H-bridge topology has modularized structure making the model or packaging less difficult (Lai and Peng 1996). Comparative analysis of the two topologies with respect to the number of component and the type of component utilized in the main inverter circuit is shown in Table 2.5. Cascaded H-bridge inverter has the following advantages over the Flying capacitor inverter;

- a. simple control technique

- b. very reliable irrespective of the desired levels of output voltage hence high modularity

- c. Uniform blocking voltage

- d. Reduced cost, simple structure and increased efficiency (Babaei and Laali 2015).

**Table 2.5:** Analysis of CHB and FC inverters

| No. of Components | Cascaded HB | Flying Capacitor |  |  |

|-------------------|-------------|------------------|--|--|

| Capacitor         | -           | 10               |  |  |

| Switch            | 8           | 8                |  |  |

| Source            | 2           | 1                |  |  |

| Diode             | 8           | 8                |  |  |

| Total             | 18          | 27               |  |  |

# 2.6 Comparative Analysis of Cascaded H-Bridge and NPC

Cascaded H-bridge inverter and the NPC inverter are similar when analyzed with respect to the level of output voltage. Fig. 2.1 and Fig 2.6 show the single phase circuit diagram of cascaded H-bridge and NPC inverter respectively. These topologies are referred to as 5-level inverters because of the steps (5-level) of output voltage that can be generated.

The number of components required in the two topologies are not equal; the cascaded H-bridge requires 8 switches (antiparallel connection of a transistor and a diode) and two dc sources to generate 5-steps of output voltage whiles the NPC topology requires 8 switches (antiparallel connection of a transistor and a diode), two capacitors, four diodes and one dc source to generate the same level of output voltage as the cascaded H-bridge topology. Comparing the NPC topology to the conventional inverter will exhibit superior advantages for the NPC topology but when compared to the cascaded H-bridge topology, the latter topology exhibits more advantages than the former. The main advantages of the NPC inverter are derived when it's compared to the traditional inverter, some advantages are reduced harmonic content, quality output waveform and minimum switch stress caused by high voltage. Also it should be noted that NPC converter is mostly suitable for renewable energy application. Due to complex nature of the topology, increasing the output voltage beyond 5-level becomes complicated hence the 3-level NPC inverter has received lots of applications (Nabae et al., 1981).

**Table 2.6:** Analysis of CHB and NPC inverters

| No. of Components | Cascaded HB | NPC |

|-------------------|-------------|-----|

| Capacitor         | -           | 2   |

| Switch            | 8           | 8   |

| Source            | 2           | 1   |

| Diode             | 8           | 12  |

| Total             | 18          | 23  |

From Table 2.6, the following deductions can be made about the two topologies; cascaded H-bridge and NPC. The number of switches utilized in the two topologies are the same, 8 bidirectional switch with respect to current for each topology. However, the NPC topology has two capacitors connected to the dc source and four diodes for voltage blocking purposes. The output voltage of the NPC inverter is dependent on the voltage ratings of the two capacitors; however, the voltage ratings of these capacitors are the same. Therefore, the input voltage is shared equally between the capacitors.

Again cascaded H-bridge inverter exhibits superior advantages over NPC inverter with the following advantages; reduced number of components, simple structure hence increasing the output levels is less complicated, modularity of the structure is easily achieved, quality output waveform, reduced loses and increased efficiency. Some advantages of NPC are: harmonic elimination at higher voltage levels, higher efficiency due to fundamental frequency switching, control of reactive power, simple control techniques and the demerits are: large number of diodes are required for higher levels, real power flow control is difficult for individual converters (Lai and Peng 1996). During any switching pattern, the maximum blocking voltage across each semiconductor switches must be equivalent to half the dc supply. Proper controlling of the inverter to avoid abrupt alterations between E and -E will produce lower harmonics and prevent simultaneous turning on and off of two switches.

## 2.7 Application of Multilevel Inverters

One major application of the multilevel inverter in the early 1990s to late 1990s is VAR compensation technique in high power transmission lines; FACTS. Reactive power control popularly known as VAR is an integral component in power systems which increases the power transmission capabilities of the system, reduce power losses due to transmission and stabilizes system (Peng and Lai 1997). Due to the MVA requirements of the power systems and the low power ratings of GTOs available, parallel connection of multilevel units or modules to achieve higher currents rating were proposed in (Schauder et al., 1995; Mori et al., 1993); this topology

did not require an increase in the GTO power ratings which was a problem at that time but lower order harmonics could be minimized with an appropriate control technique.

Application of multilevel converter in the compensation area of power systems ranges from VAR to SVC, ASVC, STATCOM (Mwinyiwiwa et al., 1997; Chen and Ooi 1996;). The various reactive power compensators such SVC, ASVC etc. have come to replace the traditional method of VAR compensation; TCR and TSC (Peng and Lai 1997; Schauder et al., 1994; Mori et al., 1993). Basically, multilevel converter are important devices in controlling the various components of flexible ac transmission system as reported in (Mwinyiwiwa et al., 1997; Mori et al., 1993; Schauder et al., 1995; Gyugyi 1995). One limitation of the GTO is the low switching frequency medium in which it can operate (Damiano et al., 1997) but IGBTs with high powerhigh switching frequency capabilities were reported in (Hiyoshi et al., 1995; Brunner et al., 1996). Some applications of multilevel converters reported in (Damiano et al., 1997) are: compensation of reactive power (Waltrich and Barbi 2009). Large induction motor drives (Menzies et al., 1994) and active filtering (Damiano et al., 1997).

Other application of multilevel converters in areas of electric drives as reported in (Sinha and Lipo 1997); an inverter/converter is required in adjustable speed drives due to the variable voltage and frequency capabilities of converters. Problems due to traditional adjustable speed drives as opposed to multilevel speed drives are reported in (Sinha and Lipo 1997). Multilevel converter based unified power flow controller application in (Chen et al., 2000), STATCOM application using chain converters. Grid Photovoltaic system using single phase multilevel converter induction motor application, AC drive application, universal power conditioner application.

### 2.8 Cascaded MLI Topologies

This section will focus on reviewing cascaded MLI topologies. Analysis will be done with respect to newer or different topologies that have been presented in past recent years with focus on the number of components utilized, the number of dc source used, permissible levels of output voltage that can be generated, type of control method used and finally compare

advantages of the various topologies reviewed. It worth mentioning at this point that the various topologies of cascaded MLI been investigated comes in different categories; some do not include the H-bridge structure whiles others include, mostly the ones without H-bridge are unable to produce negative step voltages. Also there are topologies which by design are only able to generate positive step voltages.

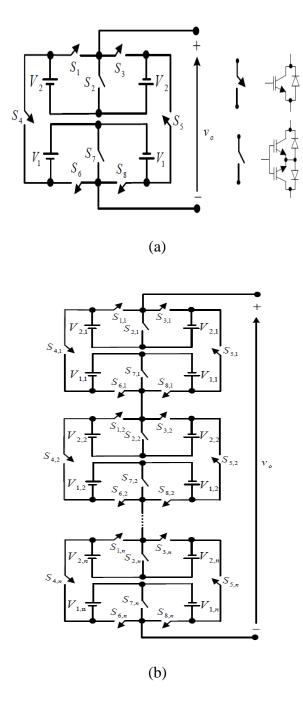

## 2.8.1 Single-phase Cascaded MLI Topologies

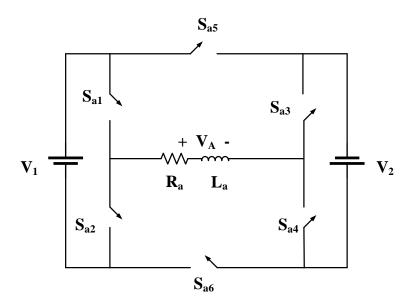

Conventional multilevel inverter topologies; Flying capacitor, cascaded H-bridge and NPC can be formed into a cascaded topology. A cascaded topology simply means connection of several units of the fundamental topology into a series chain. Because cascaded H-bridge topology has already been presented above, only new cascaded MLI topologies will be discussed from this point forward. To achieve higher efficiency, reduced cost and less component size, a new cascaded MLI structure is introduced by (Aalami et al., 2018) with minimum number of components. The basic structure of the proposed inverter is shown in Fig. 2.7. The structure is made up of 2 dc sources and 10 power switches. The proposed inverter is a further development of the conventional H-bridge structure to increase the number steps generated at the output. The number of steps generated at the output is seven (7); which is an improvement of the conventional H-bridge structure. The cascaded topology of the presented inverter is achieved by utilizing only one H-bridge structure with several units of designed topology consisting of one dc source and two power switches. The required level of output voltage determines the number of units of the designed topology which are combined with the H-bridge inverter.

Two switches are connected in the upper and lower sections of the bridge inverter to provide bidirectional power flow for both section of the bridge inverter. Fig. 2.8 show the circuit diagram of cascaded topology which is capable of generating n levels of output voltage. Five different methods or algorithms are proposed to determine the magnitude or level of the dc source voltage and also to determine the following crucial parts of the converter: a. blocking voltage, b. maximum output voltage, c. number of possible output steps of voltage, d. number of variety of the converter.

Figure 2.7: H-bridge based MLI (Aalami et al., 2018)

Figure 2.8: H-bridge based cascaded MLI (Aalami et al., 2018)

A new topology of cascaded MLI which has features of producing higher steps of output voltage whiles using limited number of components is presented in (Shahir and Babaei 2016). This topology has the ability to generate 16 steps of output voltage whiles maintaining less number of components as possible. The presented topology is able to generate only positive values of output voltage hence H-bridge structure is added to the topology to produce negative output

voltage. 16 steps of output voltage are generated without using the H-bridge structure. 4 dc source and 8 switches (two bidirectional switches and 6 switches) are harnessed in generating 16 positive steps at the inverter output. One major advantage of the proposed inverter is that; conduction losses is not really high due to the fact that only three switches are ON during generation of any level of output voltage which means that the switching losses will not be very high. Thirty-one steps of output voltages are generated when the H-bridge structure is incorporated in the basic unit. Fig. 2.11 show the basic unit of the proposed structure whiles Fig. 2.9 and Fig. 2.10 shows two cascaded structure of newly proposed topologies. 31-level output voltage of the same topology can be achieved with little changes to the basic unit. The presented topology when compared to previously published papers shows more advantages for the presented inverter in (Shahir and Babaei 2016).

Figure 2.9: Basic unit of positive16-level MLI (Shahir and Babaei 2016).

Figure 2.10: 31-level cascaded MLI (Shahir and Babaei 2016).

A new cascaded MLI with analysis from symmetric and asymmetric features utilizing reduced number of components is presented in (Babaei et al., 2016). The presented cascaded MLI has the capacity to generate 10 steps of output voltage by using 7 switches and 3 dc sources which are unequal in magnitude. One feature of the presented topology is the ability to generate only positive voltages, hence H-bridge inverter is required when negative output voltages are required to be generated. Fig. 2.11a and Fig. 2.11b shows the basic structure of the proposed inverter and output waveforms respectively. Two topologies are produced when the H-bridge

structure is added to the basic unit to derive the cascaded structure. The two proposed connections of the H-bridge are shown by Fig. 2.12a and Fig. 2.12b respectively. The basic unit is able to generate 19-steps of output voltage; this is possible due to connection of the basic unit and the H-bridge structure.

Figure 2.11: Positive 10-level inverter (Babaei et al., 2016).

Figure 2.12: Cascaded multilevel inverter (Babaei et al., 2016).

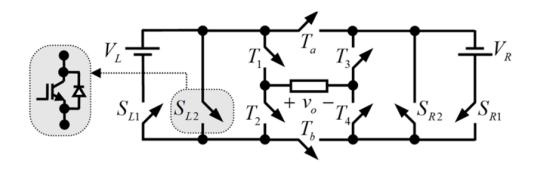

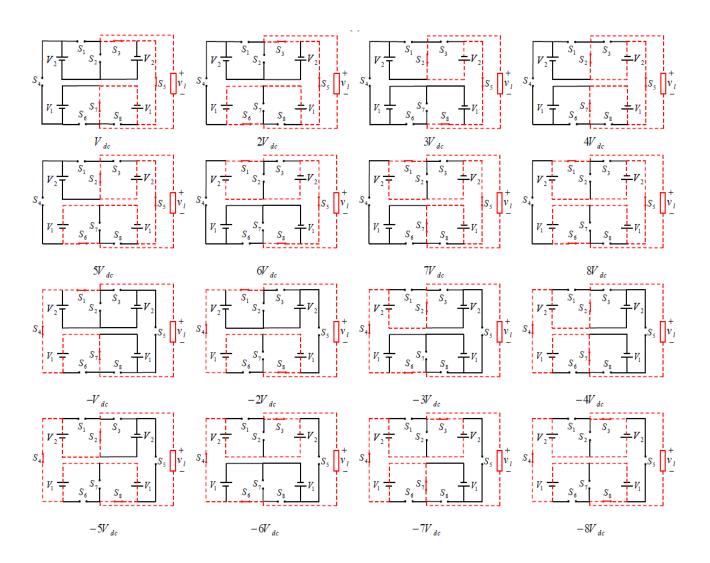

A new topology of cascaded MLI was presented by (Sarbanzadeh et al., 2016). This topology combines bidirectional switches and unidirectional switches to generate the desired level of output power. 17-level of output voltage are generated by this proposed inverter; 4 input dc voltage and 8 switches are utilized to achieve the desired maximum output voltage. Fig. 2.13a shows the basic structure of the presented MLI topology. Fig. 2.14 shows all requisites switching states of the proposed inverter. Fig. 2.13b shows cascaded structure of the same presented inverter where several units of the basic structure are connected in series to achieve a certain level of output voltage. The results of comparison between the proposed topology and other presented topologies such as (Manjrekar and Lipo 1998; Alishah et al., 2015) are presented in

the paper (Sarbanzadeh et al., 2016). This presented topology is able to achieve higher levels of output voltage and also generate negative voltage at the output without using the H-Bridge structure.

Figure 2.13: Bidirectional and unidirectional switch based MLI (Sarbanzadeh et al., 2016)

Figure 2.14: Switching states of presented MLI (Sarbanzadeh et al., 2016)

Two topologies of multilevel inverters which are dissimilar from the conventional multilevel inverter structures are presented in (Laali and Babaei 2016) and (Salehahari et al., 2017). In the topology presented in (Laali and Babaei 2016), a capacitor based basic unit structure is presented. The sources of the proposed topology are composed of one dc source and one capacitor, each connected to a separate unit of structure having two switches. In all, the overall structure is composed two sources and four switches and it's able to generate 3 steps of output voltage. In the topology of (Salehahari et al., 2017), 9-steps of output voltage are possible by the use of a coupled inductors, one dc source and 8 switches. The basic unit of the presented

hybrid coupled inductor MLI is represented by Fig. 2.15. Cascaded topology of the hybrid coupled inductor MLI is illustrated by Fig. 2.16.

Figure 2.15: Hybrid coupled inductor MLI (Salehahari et al., 2017)

Figure 2.16: Cascaded hybrid coupled inductor MLI (Salehahari et al., 2017)

Another topology of cascaded MLI cable of generating 15-levels of output voltage utilizing less number of components is presented in (Babaei and Laali 2016). The proposed topology uses four dc inputs and eight switches in deriving the desired steps of output voltage. Extension of the 15 steps from the basic structure to a possible 71-steps in a cascaded structure is possible

and also represented in (Babaei and Laali 2016). The circuit of the basic structure of the proposed topology is given by Fig. 2.17 whiles the circuit diagram of the 71-steps is represented by Fig. 2.18. The topology of 15-level and 71-level output voltage is compared with other topologies (Laali et al., 2010; Hinago and Koizumi 2010; Waltrich and Barbi (2009). The following factors are used in the comparisons; capacity of the dc input voltage, the number of components used, and the standing voltage of the inverter, also the symmetric and asymmetric functionality of the source voltage.

Figure 2.17: 15-level H-bridge inverter (Babaei and Laali 2016)

Figure 2.18: 71-level H-bridge inverter (Babaei and Laali 2016)

A further developed H-bridge multilevel inverter is presented by (Alilu et al., 2013). This topology is derived by including two switches and one dc source to conventional H-bridge topology; this results in a 7-level inverter. In all, the presented topology is composed of two dc sources and six power switches. Changing the polarity connection of one of the dc sources will results in the derivation of two topologies; these topologies are represented by Fig. 2.19a and Fig. 2.19b respectively. From the same presented MLI, 31-level and 127-level topologies are derived and represented by Fig. 2.20a and Fig. 2.20b respectively.

**Figure 2.19:** Fundamental multilevel inverter topology (Alilu et al., 2013)

Figure 2.20: 31-level and 127-level developed H-bridge (Alilu et al., 2013)

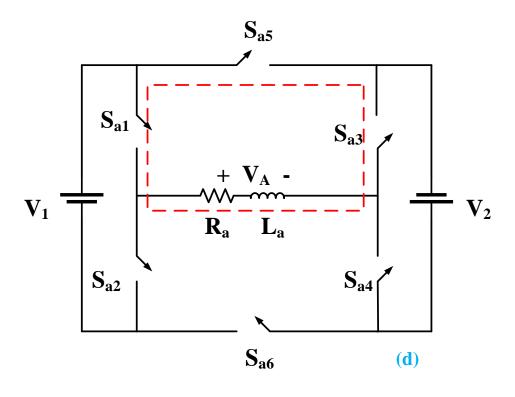

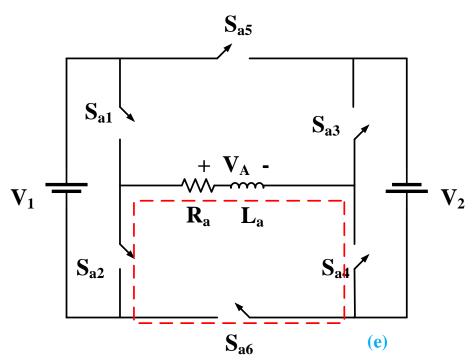

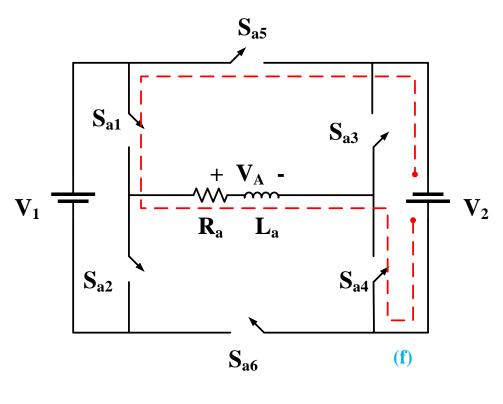

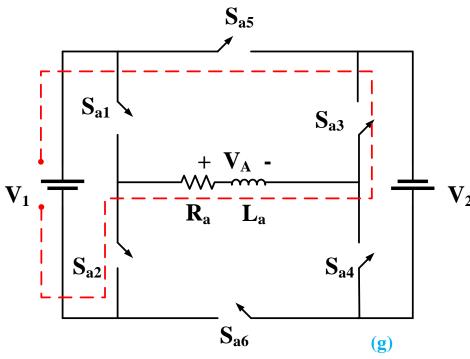

In (Alishah et al., 2016), the presented topology is derived by linking sub units of multilevel topologies. This topology just as the previously reviewed topologies achieves better efficiency by utilizing the less amount of components, minimum blocking voltage across the switches, and minimum number of dc sources but generates higher steps of output voltage. The fundamental unit of the proposed topology is given by Fig. 2.21 whiles the cascaded unit is derived by cascading the basic unit. The fundamental unit of the proposed topology in (Alishah et al., 2016) is able to produce 17-steps at the output voltage. This topology is also a further development of the H-bridge structure, hence without considering H-Bridge structure, the following equations valid in determining the component count for the following: IGBTs, driver circuit and dc sources. N is the number of units in the sub-multilevel.